The International Journal of Electrical Engineering & Education

## A Tool for Facilitating the Automated Assessment of Engineering/Science Courses

| Journal:                         | The International Journal of Electrical Engineering & Education                                                                              |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Manuscript ID                    | MIJEEE-2019-0443.R2                                                                                                                          |

| Manuscript Type:                 | Original Article                                                                                                                             |

| Date Submitted by the<br>Author: | n/a                                                                                                                                          |

| Complete List of Authors:        | Beg, Azam; United Arab Emirates University, Computer & Network<br>Alhemeiri, Mouza ; UAE University<br>Beg, Ajmal; Cortex Business Solutions |

| Keywords:                        | Massive open online course (MOOC), automated assessment, engineering education, electrical engineering, logic schematics                     |

|                                  |                                                                                                                                              |

SCHOLARONE<sup>™</sup> Manuscripts

5

6

7

8

9

10

11 12

# A Tool for Facilitating the Automated Assessment of Engineering/Science Courses

Journal Title XX(X):2--?? ©The Author(s) 2019 Reprints and permission: sagepub.co.uk/journalsPermissions.nav DOI: 10.1177/ToBeAssigned www.sagepub.com/

# Azam Beg<sup>1</sup>, Mouza Alhemeiri<sup>1</sup>, and Ajmal Beg<sup>2</sup>

#### Abstract

22 In recent years, massive open online courses (MOOCs) have become quite popular. 23 Such courses are either completely free or cost nominally. Generally, the MOOCs 24 face the challenge of not being recognized as 'regular' courses (i.e., the ones taken 25 at the traditional learning institutions). One of the main reasons for this lack of 26 acceptability is the assessment in an unsupervised environment, which is prone to 27 the problems of test-taker's online lookups or interaction with others for finding the 28 answers to the test questions. A few ways of alleviating this problem include: limiting 29 the time for answering the questions, the avoidance of repetitive questions, and the 30 creation of a large number of questions.

31 This paper presents a tool named QAgen that enables the automatic creation 32 of a large number of questions and answers related to different topics in 33 computer/electrical engineering (ECE), computer science, physics, etc. Specifically, 34 the tool is related to the courses on digital logic design, computer architecture, 35 etc. The generated guestions are in a format that is suitable both for 36 learning management system (LMS) based and/or non-LMS-based assessment 37 in conventional courses or MOOCs. The proposed tool is based on open-source 38 software, thus eliminating the need for any commercial software packages. The 39 underlying principles of QAgen are applicable to other engineering/science courses 40 as well, if the assessment methods require the creation of some connected-object 41 diagrams, tables and equations.

For assessing the usefulness of QAgen, practice question sets were created for three different courses. The student surveys for these courses indicated that the questions helped students prepare for actual tests/examinations. Especially favored by the students was the availability of correct answers at the end of each practice test/examination.

48

49

#### Keywords

1 2

3

4

5 6 7

8 9

10

11

12

13

14

15

16

Massive open online course (MOOC), engineering education, distance learning, elearning, automated assessment, test-bank, logic design, circuit schematics.

#### Introduction

In the past few years, massive open online courses (MOOCs) have gained significant popularity. Such courses are either completely free or cost very little. Due to the very nature of the MOOCs, a learner is not constrained by time or physical space. A reasonably-sized MOOC is expected to be taken by the students with a variety of strengths and weaknesses, learning styles, and cultural and educational backgrounds. For such students, the *adaptive learning* methodology is particularly useful as it offers them efficient and customized paths to learning, especially in the MOOC settings [Hao and Huiyan (2018), Lu et al. (2018)].

17 The learning outcomes of a MOOC can be assessed using a set of formative 18 and/or summative tests [Ip et al. (2018), Cross et al. (2019)]. Currently, hundreds of 19 MOOCs are available through different platforms, but they still face the challenge of 20 not being recognized as 'regular' courses (i.e., the ones taken at traditional learning 21 institutions) [Banks (2016)]. One of the main reasons for this lack of acceptability is 22 the course assessment in an unsupervised environment being prone to the problem of an 23 examinee seeking help from off-line and/or online sources during an examination/test 24 [De Rosa and Pistolese (2019)]. Although, at present, a few companies (for example, 25 ProctorU, Examity, ProctorFree, etc.) offer online, video-based proctoring solutions, 26 their wide-spread use may remain limited due to the scalability and the cost issues 27 [Soltani et al. (2019)]. Other possible solutions include: constricting the test times, not 28 repeating test questions, using a large test question database, etc [Posner (2020)]. For 29 many courses related to science or engineering, even a moderately-sized set of questions 30 can be turned into a large question database by varying the test question data within 31 pre-specified ranges. Such an *expanded* database can be instrumental in facilitating the 32 MOOC assessment. 33

Presently, many electrical/computer engineering (ECE) courses are offered in the MOOC format [Cou (2020), Uda (2020)]. The automated assessment of such courses can be enhanced significantly by using large databases comprising *unique* questions-and-answers – doing so is the aim of our current work.

The rest of this paper is organized as follows: In the first section (Literature Review), we review the work related to the test creation and test administration. The section also includes the work related to the drawing of logic/circuit diagrams (a key component

- 42 <sup>1</sup>United Arab Emirates University, Al-Ain, United Arab Emirates

- 43 <sup>2</sup>Cortex Business Solutions, Calgary, Canada

- Corresponding author:

- 45 Azam Beg

- 46 Email: abeg@uaeu.ac.ae

Prepared using sagej.cls [Version: 2017/01/17 v1.20]

https://mc.manuscriptcentral.com/mijeee

50 51

34

35

36

37

38

39

40 41

44

47 48

49

4

5

6

7

8 9

11

12

of the assessment instruments of many ECE courses). The next section provides the implementation details of QAgen, the proposed enabling tool for automated assessment. The QAgen algorithms (primarily for schematic creation) are also explained in this section. Additionally, a few examples of the QAgen usage and application are provided. The last section concludes the paper.

### 10 Literature Review

## Test Creation and Test Administration

13 The test creation and the test administration are essential parts of any academic 14 assessment process. The tests can be generated statically by using integer linear 15 programming (using multiple assessment variables) [Nguyen and Fong (2013)] or 16 by using the *semantic*-based method [Miranda et al. (2013)]. Whereas the dynamic 17 test creation can be done using the *bi-proportional matrix scaling* technique 18 [Paul and Pawar (2013)]. The integration of different tools for generating the question 19 sets for high-school subjects was proposed in [Bednarik and Kovacs (2012)]. A multi-20 year project on Internet-based learning and evaluation tool for the skill improvement 21 of the freshman and sophomore years of a university was presented in [Smaill (2005)]. 22 In order to automatically create test sheets for the candidates taking the Examination 23 System of Electrical Energy Measurement, a *fishnet* algorithm was proposed in 24 [Yuan-Bin and Jie (2012)]. The use of a concept inventory for digital logic courses was 25 proposed in [Herman and Handzik (2010)] and [Herman and Loui (2011)], but without 26 the details of the generation of question-and-answer sets. A genetic algorithm was used 27 for test question creation in [Liu et al. (2010)], however, the answer generation was not addressed. The *adaptive learning* technique can create efficient and customized 28 29 learning paths for the MOOC students. The adaptive learning directly benefits from 30 artificial intelligence techniques, such as data mining, machine learning, and predictive analytics [Lu et al. (2018)]. In order to facilitate the LMS-based courses, *learning* 31 32 object repositories can be used [Nascimento et al. (2013)]. The costs of design, delivery and assessment for such courses can be reduced by using software agents 33 [Bassi et al. (2014)]. A learning analytic tool [Al-Ashmoery and Messoussi (2015)] can 34 35 also be deployed for course instructors to study the interaction patterns of online students. Ahmed et al. proposed a scheme for grading text answers to digital design course 36 37 comparing a known set of keywords and phrases in the correct answers with the students' using cosine similarity scores [Ahmed et al. (2018)]. In order to stimulate creativity and 38 motivation among students, Oliveira et al. combined online peer assessment with scoring 39 rubrics to allow students to assess their peers' work [Oliveira et al. (2018)]. 40

41 42

43

44

45

46 47 48

49

50 51

#### Drawing Circuit Schematics

At present, a variety of university-level ECE courses are offered as MOOCs [Cou (2020), Uda (2020)]. The assessment instruments in many of these courses require the drawing of circuit/logic diagrams/schematics [Chen (2011), Rahman and Ogunfunmi (2010)]. For

4 Journal Title XX(X)

use in the assessment instruments, the auto-generation of the diagrams in *bulk* is one of the daunting challenges that is yet to be tackled.

Over the years, the drawing of the logic diagrams has been addressed [Brennan (1975), Arva et al. (1985), Aleman and Couleur (1990), Chiueh (1991), Naveen and Raghunathan (1993), Lageweg (1998), Kim et al. (2000)], however, none of the presented techniques can be utilized in the MOOC-assessment process, mainly due to the problem of scalability. The circuit diagram tool presented in 10 [Beg and Beg (2016), Beg and Beg (2018)] is limited to the analog domain. The logic-11 circuit-related open-source tools include: ChipVault [Chi (2020)], Icarus [Ica (2020)], 12 QFlow [QFl (2020)], Verilator [Ver (2020)], and Yosys [Yos (2020)]. ChipVault and 13 Icarus synthesize logic but do not create logic diagrams. QFlow and Verilator are other tools for logic synthesis sans logic diagrams. Yosys is also primarily used for logic 14 15 synthesis; the tool creates block diagrams instead of logic diagrams.

16 Two other non-commercial (open-source) tools for the *manual* drawing of circuit 17 diagrams are SmartDraw [Sma (2020)] and KTechLab [KTe (2020)]. Even though a few commercial products (for example, Cadence [Cad (2020)], Concept Engineering 18 [Con (2020)], Silvaco [Sil (2020)] and Zuken [Zuk (2020)]) generate logic diagrams, 19 these are not suitable for academic assessment because the symbols in the diagrams 20 21 are labeled with details (labels, sizes, etc.) which are only required for industrial 22 circuit design. The other major issue is the heavy licensing/administration cost of these 23 commercial products.

## QAgen – A Tool for Automatically Generating Questions and Answers

None of the literature known to the authors presents a technique for automatically 28 generating large sets of questions and the related diagrams; this points to the need for a 29 method for creating not just the test questions but also the associated diagrams, especially 30 for the purpose of MOOC assessment. 31

32 This paper proposes an automated tool that helps improve the automated assessment of engineering/science courses. The tool enables the creation of a large number of questions 33 and answers related to many topics in computer/electrical engineering, computer science, 34 35 etc. The examples of the covered engineering courses include: digital logic design, hardware description language (HDL) based design, computer architecture, digital circuit 36 37 testing, etc.

The proposed question-and-answer generation tool named 'QAgen', is based on 38 Octave, an open-source scripting language (compatible with Matlab) for scientific 39 applications. Being a commercial product, Matlab software and toolboxes carry hefty 40 licensing cost for non-students. As an example, QAgen automatically creates both 41 42 the questions and their answers related to these topics in a logic design course: analysis of combinational logic circuits, analysis of sequential logic circuits, design 43 of combinational logic circuits, and design of sequential logic circuits. The specific 44 topics in such a course include: number systems, digital building blocks (gates, decoders, 45 multiplexers, etc), Boolean functions and their simplification, etc. Thousands of unique 46

1 2 3

4

5

6

7

8

9

24 25

26

27

47 48

49

50 51 **г** ר

28 29

36

37

38 39

40 41

42

43

44

45

46 47 48

49

50 51

question-answer sets can be produced within minutes by running QAgen on an ordinary

computer. Depending on the topics being assessed, the question creation may require

one or more of these steps: automatic generation of tables of varying sizes (truth tables

and Karnaugh maps), creation of properly formatted Boolean equations with multiple

variables, and the *drawing* of logic diagrams representing arbitrary Boolean functions.

Among these steps, the automated drawing of diagrams is significantly harder than the

creation of question text, tables or Boolean equations.

QAgen is fully configurable and allows an examiner to customize the questions and

answers by setting these parameters: (a) type of circuit elements – gates, decoders,

multiplexers, etc; (b) number of circuit inputs/variables; (c) number of circuit outputs;

(d) number of gates, decoders, multiplexers, etc; (e) circuit depth (for gate-only circuits);

(f) types of gates; and (h) question format – multiple-choice, fill-in-the-blank, etc.

QAgen generates all of the question-related 'outputs', i.e., the pieces of code for:

(a) creating the complete question text including Boolean equation, truth table, etc., (b)

drawing any related circuit schematic, and (c) finding the answer for grading purpose.

The LaTex format of the QAgen outputs is suitable for both the traditional paperbased testing and the LMS-based testing for MOOCs. For use with LMSes, the opensource tools (for example, LaTeXML) can be used to easily convert the LaTex into the web-friendly HTML or XML formats; such text-based formats allow bulk uploading of large number of questions-and-answers into the well-known LMSes, such as Moodle and Blackboard.

QAgen can be readily used for test-generation for multiple courses offered by the

Departments of Computer Engineering and Electrical Engineering at our university, for

instance: Digital Design & Computer Organization, Computer Architecture, and Digital

System Design.

## QAgen Algorithms

This section presents a set of algorithms for generating random Boolean functions and related circuit descriptions (i.e., Verilog models), in a speedy fashion. A few examples and use-cases are also included. The algorithms can be coded in any web-friendly language, such as, Java, Perl, PHP, Python, etc. The algorithms serve these core functions [Beg et al. (2017)] (see Appendix A):

- 1. Creating a random Boolean equation

- 2. Representing the Boolean equation in reverse polish notation (RPN)

- 3. Creating Verilog code from the RPN

- 4. Drawing a logic diagram representing the Verilog code

The creation of *random* Boolean equations is constrained by a set of user-specified parameters. The user can specify the complexity of a logic function/circuit in terms of number of input variables, number of logic gates, and number of layers/levels. The *allowed* logic functions can also be specified, i.e., INV, AND, OR, NAND, NOR, XOR,

| Journa | l Title . | XX(X) |

|--------|-----------|-------|

|--------|-----------|-------|

and XNOR. Being able to specify the complexity of logic functions helps tailor the questions to the level of difficulty of a course or a topic. (Refer to the pseudo-code for Algorithm-1 in Appendix A).

A Boolean equation created by Algorithm-1 needs to be *pre-processed* for use by other components of QAgen. To do so, the widely-known RPN representation is used. The common RPN algorithms deal only with arithmetic functions and not with Boolean functions. In our case, an issue to contend with was the identification and processing of multi-input '*dual*' functions, i.e., NAND (applying NOT to the ANDed variables), NOR or XNOR. Therefore, we had to come up with a modified RPN algorithm to process logic operations, both *singular* and *dual*. (Refer to the pseudo-code for Algorithm-2 in Appendix A).

An RPN-formatted Boolean question facilitates the process of Verilog code creation. Firstly, the string array representing the RPN-equation is parsed to create an array that contains: type of logic gate, set of gate input signals, and gate output. The internal wires are also identified. Then, the Verilog-file creation starts by generating the required 'module' command and the set of 'input,' 'output,' and 'wire' declarations. After this step, all gate declarations are made in the proper sequence: type (AND, OR, etc.), label (G1, G2, etc.), output and input nets. Lastly, the 'endmodule' keyword is added before saving the ready-to-use Verilog file. (Refer to the pseudo-code for Algorithm-3 in Appendix A).

At the end, a logic diagram is generated from the Verilog code. To do so, firstly, the circuit inputs and outputs are parsed and then the gate descriptions (i.e., gate name, gate's input and output labels, etc) are parsed. The circuit input nodes are drawn first, followed by the gates driven only by the circuit inputs. The remaining gates are staggered (i.e., diagonally) to simplify the wiring. For aesthetic purposes, the output gates are shifted up. The wirings of the inputs are done first and then the *internal* wires are drawn. Lastly, the output wires are drawn. The input and output labels are placed next to the input and output terminals. (Refer to the pseudo-code for Algorithm-4 in Appendix A).

The creation of the textual descriptions of questions is much simpler than drawing the schematics. This simply involves displaying fixed/pre-set text strings for different question types.

The *correct answer* to a question is found by simulating its HDL code; an open-source simulator Icarus [Ica (2020)] is used for this purpose.

#### QAgen Applications

As mentioned earlier, QAgen has applications in many courses in a typical ECE curricula, as illustrated by the following examples.

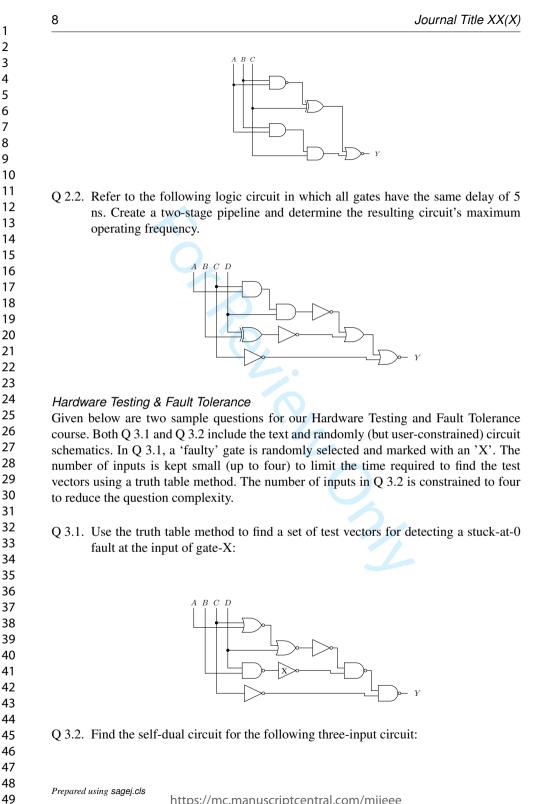

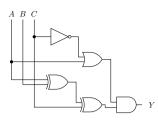

#### Digital Design

Given below are three sample questions for our Digital Design & Computer Organization

course and the Digital System Design course. Q 1.1 requires the display of question text

and the drawing of a circuit schematic with a random mix of logic gates. The number of

gates and their types are specified as input parameters to QAgen. Q 1.2 needs only the

1 2 3 question text and a randomly generated Boolean equation with a user-specified number of variables (three in this case, i.e., A, B, and C). Lastly, Q 1.3 requires the question text 4 5 and a random piece of Verilog HDL code; the code is constrained by the user-defined 6 parameters, i.e., number of circuit inputs and the count and the types of logic gates. 7 O 1.1. Draw the truth table for the following logic circuit: 8 9 ABC 10 11 12 13 14 15 16 17 Q 1.2. Convert the following *dataflow* style function into *gate-level* HDL format: 18 19  $Z = (A + B.C).(A \oplus C)$ 20 21 Q 1.3. Write an *exhaustive* testbench for the logic circuit described by the following 22 Verilog HDL code: 23 24 module fcn1 (Y, A, B, 25 input A, B, C; 26 output Y; 27 wire w1, w2, w3; 28 nand G1 (w1, C, B); 29 not G2 (w2, A); 30 G3 (w3, B); not 31 G4 (Z, w3, w2); or 32 endmodule 33 34 35 Computer Architecture 36 Given below are two sample questions related to the timing and pipelining of circuits 37 in our Computer Architecture course. Q 2.1 involves the display of question text and 38 the generation of the schematic of a random logic circuit, for which the contamination 39 and the propagation delays need to be calculated. Here, the number of circuit inputs and 40 numbers and types of gates are specified by the user. The numerical values (i.e., 'delays') 41 vary randomly within a user-specified integer range (let's say between 2 ns and 10 ns). 42 Q 2.2 is about the pipelining of a logic circuit. Although this question requires a logic 43 circuit larger than the one in Q 2.1, the schematic drawing process remains the same.

Q 2.1. Refer to the following logic circuit in which all gates have the same delay of 10 ns. Calculate the circuit's contamination delay and the propagation delay.

50 51

49

44 45

https://mc.manuscriptcentral.com/mijeee

## QAgen Evaluation

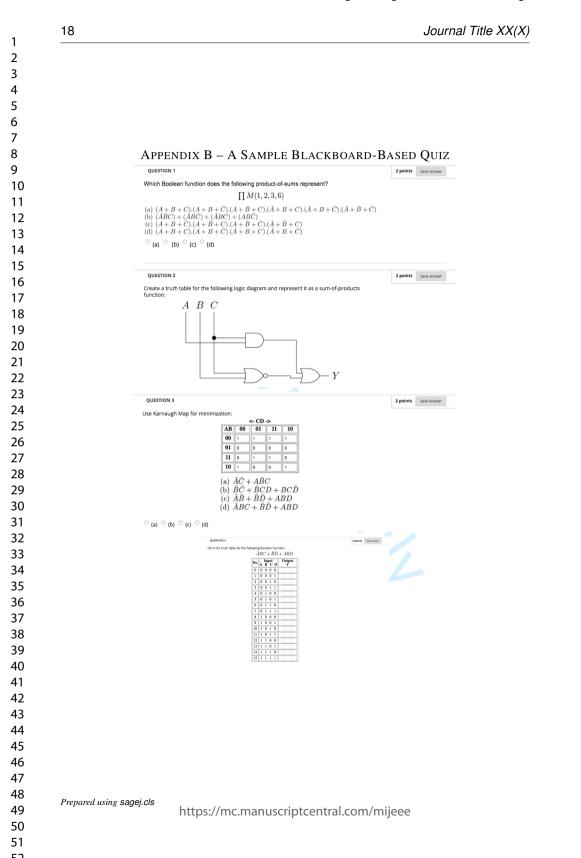

As a proof-of-concept, a large number of questions were generated for different traditional/classroom-based courses during the Spring 2019 semester. A few examples of the questions uploaded on BlackBoard (a well-known LMS) are shown in Appendix B. The examples include questions about logic equations, logic diagrams, Karnaugh maps, and truth tables for our Digital Design & Computer Organization course. At this stage, the questions were provided to the students only for practice, i.e., their scores were not included in their actual course grades. The students were asked to fill in surveys (similar to the ones in [Patel et al. (2002), Lawand and Pang (2014)]) about the questions for three courses. The results of the surveys are shown in Table I. The majority of students used the questions for practice before the actual (graded) test/examination. Most of the students felt that the questions helped them prepare for the tests/examinations. The availability of the answers to the questions was overwhelmingly favored by the students. A large number of students felt more confident in problem-solving after going through the questions. Finally, the students believed that their grades improved when they practiced with the question-answer sets. Our initial assessment of the QAgen tool motivates us to extend the tool's usage to MOOC(s).

Prepared using sagei.cls

https://mc.manuscriptcentral.com/mijeee

| Table 1. Student survey statements for three different coursSlightly disagree, 3 = Neutral, 4 = Slightly agree, 5 = StronglDigital Design & Computer Orgar | y agree | e) ( | gly disa  | gree, 2 | = |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-----------|---------|---|

| Question                                                                                                                                                   | 1       | 2    | 3         | 4       |   |

| I solve the practice questions before an actual test/exam.                                                                                                 | 3%      | 0%   | 9%        | 33%     | 5 |

| The practice questions help me prepare for an actual test/exam.                                                                                            | 0%      | 0%   | 3% 15%    |         | 8 |

| Having answers to the practice questions is useful for my checking my understanding.                                                                       | 0%      | 0%   | 0% 3% 3%  |         | 9 |

| It would be a good to work with practice questions for different topics in this course.                                                                    | for 0%  |      | 6%        | 24%     | 7 |

| I have more confidence in my skills after solving practice questions.                                                                                      | 0%      | 0%   | 3%        | 24%     | 7 |

| My score in an actual assessment is higher when I solve practice questions.                                                                                | 0%      | 6%   | 9%        | 33%     | 5 |

| Computer Architecture                                                                                                                                      |         |      |           |         |   |

| Question                                                                                                                                                   | 1       | 2    | 3         | 4       |   |

| I solve the practice questions before an actual test/exam.                                                                                                 | 6%      | 0%   | 0% 18% 29 |         |   |

| The practice questions help me prepare for an actual test/exam.                                                                                            | 0%      | 12%  | 6%        | 29%     |   |

| Having answers to the practice questions is useful for my checking my understanding.                                                                       | 6%      | 0%   | 6%        | 13%     | , |

| It would be a good to work with practice questions for different topics in this course.                                                                    | 6%      | 0%   | 18%       | 6%      |   |

| I have more confidence in my skills after solving practice questions.                                                                                      | 6%      | 6%   | 21%       | 11%     |   |

| My score in an actual test/exam is higher when I solve practice questions.                                                                                 | 6%      | 6%   | 18%       | 23%     |   |

| Hardware Testing & Fault Toler                                                                                                                             | ance    |      |           |         |   |

| Question                                                                                                                                                   | 1       | 2    | 3         | 4       |   |

| I solve the practice questions before an actual test/exam.                                                                                                 | 0%      | 0%   | 44%       | 37%     |   |

| The practice questions help me prepare for an actual test/exam.                                                                                            | 0%      | 0%   | 12%       | 19%     |   |

| Having answers to the practice questions is useful for my checking my understanding.                                                                       | 0%      | 0%   | 6%        | 13%     | ł |

| It would be a good to work with practice questions for different topics in this course.                                                                    | 0%      | 0%   | 19%       | 25%     |   |

| I have more confidence in my skills after solving practice questions.                                                                                      | 0%      | 0%   | 25%       | 13%     |   |

| My score in an actual test/exam is higher when I solve<br>Propraotice                                                                                      | 6%      | 0%   | 13%       | 31%     |   |

4

5

6

7

8

9

10

11

12

13

14

15

16

17 18

19 20

21

22

23

24

29

30

31

32 33

34

35

36

37

38

## Conclusions

The proposed QAgen tool is capable of automatically generating a large number of test questions and the corresponding answers in a format suitable for LMS and/or non-LMS-based traditional course or MOOC assessment. The tool is based on an opensource software thus eliminating the need for any commercial packages. The algorithms for automatically creating the circuit diagrams have been included in this work. The QAgen-generated questions have been used in recent offerings of a few courses; the student surveys from these courses show the students benefitted from the varied sets of practice problems, specifically, the students prepared better for their actual/graded tests/examinations.

The principles used herein can also be helpful for other traditional courses or MOOCs, provided they require the creation of diagrams with connected geometric objects, codebased problems, equations and their solutions, etc. Our future work will be focused on extending the capabilities of QAgen for a complete MOOC.

# References

- [Ahmed et al. (2018)] Ahmed B, Kagita M, Wijenayake C and Ravishankar J (2018) Implementation Guidelines for an Automated Grading Tool to Assess Short Answer Questions on Digital Circuit Design Course. In: 2018 IEEE Int. Conf. Teaching, Assessment, and Learning for Eng. Wollongong, Australia, pp. 1142–1145.

- [Al-Ashmoery and Messoussi (2015)] Al-Ashmoery Y and Messoussi R (2015)

Learning analytics system for assessing students' performance quality and text

mining in online communication. In: 2015 Intell. Syst. Comput. Vis. Fez, Morocco,

pp. 1–8.

- [Aleman and Couleur (1990)] Aleman E and Couleur J (1990) Automated schematic capture with the USC51 embedded microcontroller. In: *Euro ASIC '90*. Paris, France, pp. 461–465.

- [Arya et al. (1985)] Arya A, Swaminathan V, Misra A and Kumar A (1985) Automatic Generation of Digital System Schematic Diagrams. In: 22nd Des. Autom. Conf. Las Vegas, NV, USA, pp. 388–395.

- [Banks (2016)] C Banks and Edward M (2016) The Acceptability of MOOC Certificates in the Workplace. In: *Int. Conf. e-Learning*. Madeira, Portugal, pp. 419–423.

- [Bassi et al. (2014)] Bassi R, Daradoumis T, Xhafa F, Caballe S and Sula A (2014)

Software Agents in Large Scale Open E-learning: A Critical Component for the

Future of Massive Online Courses (MOOCs). In: 2014 Int. Conf. Intell. Netw.

Collab. Syst. Salerno, Italy, pp. 184–188.

- [Bednarik and Kovacs (2012)] Bednarik L and Kovacs L (2012) Implementation and

assessment of the automatic question generation module. In: 2012 IEEE 3rd Int. *Conf. Cogn. Infocommu.* Kosice, Slovakia, pp. 687–690.

50 51

47 48

**FD**

| Journal Title XX(X                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| eg et al. (2017)] Beg A, Alhemeiri M and Beg A (2017) Enhancing automated<br>assessment for engineering MOOCs. In: <i>IASTED Int. Conf. Model. Simul. Identif</i><br>( <i>MSI 2017</i> ) Calgary, AB, Canada, pp. 1–5.                        |

| eg and Beg (2016)] Beg A and Beg A (2016) Auto-Generating Publication-Quality<br>Circuit Schematics Using Open Technologies. In: 21st West. Can. Conf. Comput<br>Educ. (WCCCE '16). Kamloops, BC, Canada, pp. 51–56.                          |

| eg and Beg (2018)] Beg A and Beg A (2018) Using Open Technologies fo<br>Automatically Creating Question-and-Answer Sets for Engineering MOOCs<br><i>Comput. Appl. Eng. Educ.</i> 26(3): 617–625.                                              |

| rennan (1975)] Brennan RJ (1975) An Algorithm for Automatic Line Routing on<br>Schematic Drawings. In: <i>12th Des. Autom. Conf.</i> Piscataway, NJ, USA, pp. 324-<br>330.                                                                    |

| ad (2020)] Cadence (2020). URL http://www.cadence.com/.                                                                                                                                                                                       |

| hen (2011)] Chen P (2011) Construction of test question database for electrical and electronic technology. In: 2011 Int. Conf. Electron. & Mechanical Eng. Inf. Technol Harbin, China, pp. 1347–1350.                                         |

| hi (2020)] ChipVault (2020). URL http://chipvault.sourceforge.net/.                                                                                                                                                                           |

| hiueh (1991)] Chiueh TC (1991) HERESY: A hybrid approach to automatic<br>schematic generation (for VLSI). In: <i>Eur. Conf. Des. Autom.</i> Amsterdam<br>Netherlands, pp. 419–423.                                                            |

| on (2020)] Concept Engineering (2020). URL https://www.concept.de.                                                                                                                                                                            |

| ou (2020)] Coursera (2020). URL https://www.coursera.org/.                                                                                                                                                                                    |

| ross et al. (2019)] Cross JS, Keerativoranan N, Carlon MKJ, Tan YH, Rakhimberdina Z and Mori H (2019) Improving MOOC quality using learning analytics and tools In: 2018 13th Int. Conf. Comput. Sci. Educ. Milwaukee, WI, USA, pp. 174-0179. |

| Pe Rosa and Pistolese (2019)] De Rosa A and Pistolese M (2019) Evolution, Education<br>and Massive Open Online Courses: A Multiverse Proposal. In: 2019 IEEE Learning<br>With MOOCS (LWMOOCS). Milwaukee, WI, USA, pp. 191–195.               |

| Tao and Huiyan (2018)] Hao W and Huiyan L (2018) Research on Blended Teaching<br>Reform and Innovation Strategy Based on MOOC Education. In: 2018 13th Int<br>Conf. Comput. Sci. Educ. (ICCSE 2018), Colombo, Sri Lanka, pp. 1–4.             |

| Terman and Handzik (2010)] Herman GL and Handzik J (2010) A preliminary<br>pedagogical comparison study using the digital logic concept inventory. In: 2010<br>IEEE Front. Educ. Conf. Washington, DC, USA, pp. F1G–1–F1G–6.                  |

| pared using sagej.cls https://mc.manuscriptcentral.com/mijeee                                                                                                                                                                                 |

| Logic Concept            | 2011)] Herman GL and Loui MC (2011) Administering a Digita t Inventory at Multiple Institutions. In: 2011 ASEE Annu. Conf. Expo<br>C, Canada, pp. 1–12.                                                  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [Ica (2020)] Icarus      | (2020). URL https://sourceforge.net/projects/iverilog/.                                                                                                                                                  |

| Design and E             | HSH, Li C, Leoni S, Chen Y, Ma K, Wong CH and Li Q (2018 valuate Immersive Learning Experience for Massive Open Online OCs). <i>IEEE Trans. Learn. Technol.</i> : 1–10.                                  |

| an efficient scl         | Kim NH, Kim KS, Choi KM and Kong JT (2000) RightTopologizer hematic generator for multi-level optimization. In: <i>13th Annu. IEEI C Conf.</i> Arlington, VA, USA, pp. 387–391.                          |

| [KTe (2020)] KTec        | hLab (2020). URL https://sourceforge.net/projects/ktechlab/.                                                                                                                                             |

|                          | Lageweg C (1998) Designing an Automatic Schematic Generator fo<br>cription. Technical report, Delft University of Technology, Delft                                                                      |

| monitor learni           | (2014)] Law E and Pang S (2014) Use of online assessments to ng outcomes in higher level engineering courses. In: <i>4th Interdiscip</i> c. Conf. Santa Clara, CA, USA, pp. 18–23.                       |

| Test Paper Ge            | Liu D, Zheng L, Wang X and Zhuan S (2010) Research on Intelligen<br>eneration Based on Improved Genetic Algorithm. In: 2010 Second<br>ngr. Intell. Syst., volume 2. Guilin, China, pp. 363–365.          |

| Recent Studie            | u M, Zhao H, Guo Y, Wang K and Huang Z (2018) A Review of the s on MOOCs. In: 2018 13th Int. Conf. Comput. Sci. Educ. (ICCS) bo, Sri Lanka, pp. 1–5.                                                     |

| (2013) Autom             | 3)] Miranda S, Mangione GR, Orciuoli F, Gaeta M and Loia V<br>natic generation of assessment objects and Remedial Works for<br>2013 12th Int. Conf. Inf. Technol. Based High. Educ. Train. Antalya<br>8. |

| model to supp            | 2013)] Nascimento MGF, Brandao LO and Brandao AAF (2013) A ort a learning object repository for web-based courses. In: 2013 IEEE Conf. Oklahoma City, OK, USA, pp. 548–552.                              |

| - 0                      | nathan (1993)] Naveen B and Raghunathan K (1993) An automatic matic generator. <i>IEEE Des. Test Comput.</i> 10(1): 36–41.                                                                               |

| tive Static Test         | (2013)] Nguyen ML and Fong ACM (2013) Large-Scale Multiobjec<br>Generation for Web-Based Testing with Integer Programming. <i>IEEI</i><br><i>Technol.</i> 6(1): 46–59.                                   |

| Prepared using sagej.cls | https://mc.manuscriptcentral.com/mijeee                                                                                                                                                                  |

**FD**

| 14                             | Journal Title XX(X                                                                                                                                                                                                                                         |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Assessment as<br>Undergraduate | [8)] Oliveira T, Stringhini D and Corrêa D (2018) Online Pee<br>nd Scoring Rubric to Produce Better Digital Systems Designs in a<br>e Computer Engineering Curriculum. In: <i>Amer. Conf Learning Tech</i><br>o Paulo, Brazil, pp. 393–399.                |

| web-based tut                  | Patel N, Covic G and Hussmann S (2002) Experience using a nove<br>torial and assessment tool for advanced electronics teaching. In: <i>Interput. in Educ.</i> , Auckland, New Zealand, pp. 643–647.                                                        |

| Generation Us                  | 013)] Paul D and Pawar J (2013) Dynamic Question Paper Templat<br>sing Bi-proportional Scaling Method. In: 2013 IEEE Fifth Int. Con<br>Kharagpur, India, pp. 80–83.                                                                                        |

|                                | osner Z (2020) What is Adaptive Learning Anyway? URL http:<br>acation.com/ideas/what-is-adaptive-learning.html.                                                                                                                                            |

| [QFl (2020)] QFlo              | w (2020). URL http://opencircuitdesign.com/qflow/.                                                                                                                                                                                                         |

| questions for                  | funmi (2010)] Rahman M and Ogunfunmi T (2010) A set of a concept inventory for a DC Circuits course. In: 2010 IEEE In s Syst. Paris, France, pp. 2808–2811.                                                                                                |

| [Sil (2020)] Silvac            | o (2020). URL https://www.silvaco.com.                                                                                                                                                                                                                     |

|                                | naill C (2005) The Implementation and Evaluation of OASIS: A Web<br>ng and Assessment Tool for Large Classes. <i>IEEE Trans. Educ.</i> 48(4)                                                                                                               |

| [Sma (2020)] Sma               | rtDraw (2020). URL https://www.smartdraw.com/circuit-diagram/.                                                                                                                                                                                             |

| and Jararweh<br>System for M   | P)] Soltani M, Zarzour H, Babahenini MC, Hammad M, Al-Smadi M<br>Y (2019) An Emotional Feedback Based on Facial Action Codin<br>IOOCs with Computer-Based Assessment. In: 2019 6th Int. Com<br>Anal., Management and Security Granada, Spain, pp. 286–290. |

| [Uda (2020)] Udac              | city (2020). URL https://www.cadence.com.                                                                                                                                                                                                                  |

| [Ver (2020)] Verila            | ator (2020). URL https://www.veripool.org/.                                                                                                                                                                                                                |

| [Yos (2020)] Yosys             | s (2020). URL http://www.clifford.at/yosys/.                                                                                                                                                                                                               |

| Automatic Te                   | (2012)] Yuan-Bin C and Jie D (2012) Design on Algorithm (<br>est Papers Generation for Examination System of Electric Energy<br>. In: 2012 Int. Conf. Comput. Sci. Serv. Syst. Nanjing, China, p                                                           |

| [Zuk (2020)] Zuke              | n (2020). URL https://www.zuken.com/.                                                                                                                                                                                                                      |

| Prepared using sagej.Cls       | https://mc.manuscriptcentral.com/mijeee                                                                                                                                                                                                                    |

6 APPENDIX A – QAGEN ALGORITHMS 7 8 Procedure: CreateBooleanEquation Input: integer nGateCount string BoolEq 9 Output: 10 initialize g, boolEq; while (g < nGateCount) {

Pick a random logic operation

Pick a random number of input variables</pre> 11 12 Apply logic operation to randomly picked variables to create a logic gate Save the logic gate as array-element gate[g] 13 Increment q 14 Append a random number of left brackets to boolEq Append gate[0] to boolEq 15 Append a random logic symbol to boolEq (g=1; g<=nGateCount; g++) { 16 Append gate[g] to boolEq Append a random number of right brackets to boolEq 17 Append a random logic symbol to boolEq Append a random number of left brackets to boolEq 18 Append any remaining right brackets to boolEq 19 return boolEq 20 Pseudo-code 1. Creating Boolean Equations. 21 22 éc. 23 24 25 26 27 28 29 Procedure: ConvertBoolean2RPN 30 string BoolEq Input: Output: string rpn 31 Store first token in BoolEq as output, outputName 32 for (i=2; i<length(BoolEq); i++) {</pre> Read token at i 33 if token is a left parenthesis { Push it onto the stack 34 if token is a right parenthesis { 35 Until the token at the top of the stack is a left parenthesis, pop stack contents to output string rpn 36 if token is an operator { while (operator precedence <= stack peek precedence) { 37 Pop stack contents to rpn string 38 if token is an operand { 39 Append token to rpn string 40 Pop remaining stack contents to rpn string 41 Pseudo-code 2. Transforming the Boolean functions into RPN notation. 42 43 44 45 46 47

Prepared using sagej.cls

48

49

16 Journal Title XX(X) 1 2 3 4 5 6 7 8 9 10 11 Procedure: ConvertRPN2Verilog Input: string rpn file code.v 12 Output: 13 % Parse rpn and store it in vArray[operation, output, operand1, operand2] nflag = 0; % consider nand/nor/xnor if high

gateCount = 0; % number of gates

prevOut = '' % keep track of the previous operation 14 15 for (i=1; i<length(rpn); i++) {</pre> 16 Read token at j if (token is an operand) { 17 Push it onto the stack Append operand to inputList 18 else if (token is an operator) { 19 Find operation name from operator (operator is INV) { 20 Store previous gate in prevOut, if any If(stack peek equals prevOut and nflag is high) { 21 change vArray[gateCount,1] to the appropriate gate (NAND, NOR, XNOR) 22 else ( Increment gateCount 23 Store operation name in vArray[gateCount, 1] Create wire name and store it in wireList and vArray[gateCount, 2] Pop stack and store value in vArray[gateCount, 3] 24 Push the created wire onto the stack 25 } 26 else { Increment gateCount 27 Store operation name in vArray[gateCount,1] Create wire name and store it in wireList and vArray[gateCount, 2] Pop stack for operand 1 and store it in vArray[gateCount, 3] 28 Pop stack again for operand 2 and store it in vArray[gateCount, 4] Push the created wire onto the stack 29 } 30 31 % Generate verilog code and write to file Print 'module' definition to a string 32 Append output name ('Y') Append input list from vArray-inputList 33 Append wire list from vArray-wireList for (r=1; r<=vArray rows; r++)</pre> 34 Print vArray contents in Verilog format newline 35 Append 'endmodule' to the string 36 Write string to a file 'code.v 37 Pseudo-code 3. Creating the Verilog models from the RPN format. 38 39 40 41 42 43 44 45 46 47 48 Prepared using sagej.cls 49 https://mc.manuscriptcentral.com/mijeee

51

```

6

7

8

Procedure: CreateLogicDiagram

9

file Code.v

file LogicDiagram.tex

Input:

Output:

10

% nInputs is number of input ports; nOutputs is number of output ports; and nWires is number of wires (internal nets)

11

Open Code.v file for reading

Identify code line(s) starting with 'input', and parse to store input labels in input[nInputs-1:0]

Identify code line(s) starting with 'output', and parse to store output labels in output[nOutputs-1:0]

12

Identify code line(s) starting with 'wire', and parse to store wire labels in wire[nWires-1:0]

13

nGate = 0;

while not('endmodule') {

14

Parse the gate descriptions to extract input and output labels.

Store gate input and output labels in gateInput[] and gateOutput[] arrays

15

Identify which gate input is driven by which circuit-input or other gate-output

nGate++

16

% --- Draw gates -

17

% (x, y) is gate coordiate; x is horizontal position and y is vertical

Mark locations of all gates as 'not-assigned'

18

Set x = 0, y = 0

for (i=0; i<nGates; i++) {</pre>

19

if gate[i] is driven only by circuit inputs, draw gate at (x, y) {

mark gate[i] location as

20

y-- % next gate below this one

21

\stackrel{\times}{x} = 1; y = 1; for (i=0; i<nGates; i++) ( if gate[1] location is 'unassigned' and it does not drive an output, draw gate at (x, y) (

22

23

mark gate[i] location as 'assigned'

x++; y-- % next gate is on the right and below

24

}

25

for (i=0; i<nGates; i++) {

if gate[i] location is 'unassigned' and gate drives an output {</pre>

26

set gate[i] y as middle of its driving gate y

draw gate at (x, y)

27

mark gate[i] location as 'assigned'

3

28

% --- Draw wires and labels ---

29

x = -1; y = 0

for (i=0; i<nInputs; i++) {</pre>

30

for (j=0; j<nGateInputs; i++) {</pre>

draw wire from (x, y) to all gate-inputs driven by input[i] with small horizontal lines at the gate input j and

31

input[i]

display input labels at (-0.5, y)

32

y--

}

33

for (i=0; i<nGates; i++) {</pre>

34

for (j=0; j<nGateInputs; i++) {</pre>

draw wire from gateInput[j] to its 'driver' gate (using wire[] with small horizontal lines at the gate input j

35

and the driver output[i]

36

for (i=0; i<nOutputs; i++) {</pre>

37

draw small horizontal output wire

display output label

38

Save logic diagram .tex file

39

Pseudo-code 4. Drawing logic diagrams from the Verilog code.

40

41

42

43

44

45

46

47

48

Prepared using sagej.cls

49

https://mc.manuscriptcentral.com/mijeee

50

```