# MEMORY-BASED HARDWARE-INTRINSIC SECURITY MECHANISMS FOR DEVICE AUTHENTICATION IN EMBEDDED SYSTEMS

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Soubhagya Sutar

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

August 2020

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Dr. Vijay Raghunathan, Chair School of Electrical and Computer Engineering Dr. Anand Raghunathan School of Electrical and Computer Engineering

Dr. Kaushik Roy

School of Electrical and Computer Engineering

Dr. Shreyas Sen

School of Electrical and Computer Engineering

### Approved by:

Dr. Dimitrios Peroulis

Head of the School Graduate Program

Dedicated to my parents, **Meena** and **Janmejay**, who taught me the values of sincerity and hard work and to my wife, **Nupur**, who gave me the gift of unconditional love

#### ACKNOWLEDGMENTS

Pursuing a Ph.D. has been one of the most challenging but equally rewarding phases of my life. An incredible number of people have supported me on this journey and helped me achieve this long-cherished goal. First and foremost, I express my deepest gratitude towards my advisor, Prof. Vijay Raghunathan, for his intellectual guidance, active support, and constant encouragement throughout my entire academic life at Purdue University. I thank him for giving me the freedom to explore my areas of interest as a new Ph.D. student and sharing his valuable advice that helped me decide my dissertation topic. As my major advisor, he carefully stimulated ideas in me without explicitly prescribing the next steps, thereby helping me develop the thought process required of an independent researcher. His ability to present his ideas and work most articulately has always amazed me and helped me learn the skills of an effective presenter. I truly appreciate his support and understanding through the many ups and downs of my Ph.D. journey. Whether it is about a difficult paper rebuttal, finding an assistantship, or a personal issue, Prof. Raghunathan has always been a patient listener and helped me overcome the situation. I am extremely grateful to him for believing in me and allowing me to join his research group, where I could work towards addressing some of the most exciting and challenging research problems in embedded systems design.

I am also grateful for the immense support and understanding of the other members of my dissertation committee –

**Prof. Anand Raghunathan**, for his valuable advice that helped me get started as a new Ph.D. student, teaching me key concepts in embedded systems design, and giving me constructive feedback on my research and course projects,

**Prof. Kaushik Roy**, for sharing his invaluable insights and feedback on my research work, and

**Prof. Shreyas Sen**, for his helpful suggestions and constructive feedback towards improving key aspects of my dissertation.

While this journey has been challenging, it has certainly been enjoyable through the association of my lab-mates and friends. I sincerely thank my lab-mate, Arnab, who collaborated with me on several projects and guided me in my initial days in the group. I enjoyed our research discussions and appreciate the insights and ideas that he brought into them. I am extremely grateful to my lab-mate, Hrishikesh, who mentored me as a senior member of the group, motivated me and helped me build the skills required to pursue research. I am very grateful to the other members of my research group – Younghyun for his invaluable help with my first publication and Woosuk for helping me out with the TA duties. I would also like to thank my current lab-mates – Soumendu and Malin for giving me their precious support and allowing me to share my thoughts and feedback on their research work. Along this path, I also met several great people and made some very good friends. I would like to thank each one of them – Krishna, Arnab, Priya, Hrishikesh, Shubham, Gowtham, Ashish, and Soumendu, who gave me several fond memories over these years and made my life truly eventful.

Finally, I express my deepest gratitude to my parents, who are my first teachers and role models. I thank my mother, *Meena*, who taught me the importance of sincerity and hard work, deeply cared for me, and supported me selflessly all these years. I am very thankful to my father, *Janmejay*, who nurtured the curiosity in me about science and inspired me to pursue engineering as a career. I am also grateful to my grandparents and other family members, who have showered me with their blessings and love. Last but not the least, I dedicate this dissertation to my lovely wife, *Nupur*. I am truly humbled by her unconditional love, selfless support, and unwavering trust, all of which gave me the strength to embark upon this difficult and exciting journey.

# TABLE OF CONTENTS

|    |      |        | Page                                                                                                 |

|----|------|--------|------------------------------------------------------------------------------------------------------|

| LI | ST O | F TAB  | LES                                                                                                  |

| LI | ST O | F FIGU | JRES                                                                                                 |

| Al | BSTR | ACT    |                                                                                                      |

| 1  | INT  | RODU   | CTION                                                                                                |

|    | 1.1  | Resear | cch Contributions and Dissertation Overview                                                          |

|    |      | 1.1.1  | An Intrinsically-Reconfigurable DRAM PUF for Device Au-<br>thentication and Random Number Generation |

|    |      | 1.1.2  | Memory-Based Combination PUFs for Device Authentication<br>in Embedded Systems                       |

|    |      | 1.1.3  | A Lightweight End-to-End Authentication Protocol for Implantable<br>Medical Devices                  |

| 2  | BAC  | CKGRO  | UND AND RELATED WORK                                                                                 |

|    | 2.1  | Device | e Authentication                                                                                     |

|    | 2.2  | Physic | cally Unclonable Functions (PUFs)                                                                    |

|    |      | 2.2.1  | Memory-based PUFs                                                                                    |

|    |      | 2.2.2  | DRAM: Structure and PUF mechanisms                                                                   |

|    |      | 2.2.3  | SRAM: Structure and PUF mechanisms                                                                   |

|    |      | 2.2.4  | Other Memory-based PUFs                                                                              |

|    |      | 2.2.5  | Reconfigurable PUFs                                                                                  |

|    |      | 2.2.6  | Strong and Weak PUFs                                                                                 |

|    |      | 2.2.7  | Combination PUFs                                                                                     |

|    | 2.3  | Authe  | ntication in Implantable Medical Devices (IMDs)                                                      |

|    |      | 2.3.1  | Trusted-entity Approach and the IMD Ecosystem                                                        |

|    |      | 2.3.2  | Other Approaches to IMD Authentication                                                               |

vii

| 3 |     |        | NSICALLY RECONFIGURABLE DRAM PUF FOR DEVICE<br>ICATION AND RANDOM NUMBER GENERATION 21 |

|---|-----|--------|----------------------------------------------------------------------------------------|

|   | 3.1 | Chapt  | er Contributions                                                                       |

|   | 3.2 | Motiv  | ation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $24$                                |

|   | 3.3 | D-PU   | F: An Intrinsically-reconfigurable DRAM PUF                                            |

|   | 3.4 | Device | e Authentication using D-PUF                                                           |

|   |     | 3.4.1  | Definitions and Assumptions                                                            |

|   |     | 3.4.2  | Challenge and Response Message Format                                                  |

|   |     | 3.4.3  | Characterization phase                                                                 |

|   |     | 3.4.4  | Enrollment Phase                                                                       |

|   |     | 3.4.5  | Authentication Phase                                                                   |

|   | 3.5 | Rando  | om Number Generation using D-PUF                                                       |

|   | 3.6 | Exper  | imental Methodology                                                                    |

|   |     | 3.6.1  | Experimental Setup                                                                     |

|   |     | 3.6.2  | Characterization Methodology                                                           |

|   | 3.7 | Exper  | imental Results                                                                        |

|   |     | 3.7.1  | Device Authentication                                                                  |

|   |     | 3.7.2  | Effects of Parameter Variations                                                        |

|   |     | 3.7.3  | Uniqueness Analysis                                                                    |

|   |     | 3.7.4  | Robustness Analysis: Authentication under Varying Operating<br>Conditions              |

|   |     | 3.7.5  | True Random Number Generation                                                          |

|   | 3.8 | Discus | ssions                                                                                 |

|   |     | 3.8.1  | Attack Scenarios and Assumptions                                                       |

|   |     | 3.8.2  | Mitigation of Authentication Latency                                                   |

|   |     | 3.8.3  | Generation of Challenge Bit-Stream                                                     |

|   |     | 3.8.4  | Block Selection: Solution Space and Optimal Solution 63                                |

|   | 3.9 | Conclu | usion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $64$              |

viii

| 4 |                                                                                     |                | BASED COMBINATION PUFS FOR DEVICE AUTHENTI-                               | . 65 |  |

|---|-------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------|------|--|

|   | 4.1                                                                                 | Chapt          | er Contributions                                                          | . 65 |  |

|   | 4.2                                                                                 | 4.2 Motivation |                                                                           |      |  |

|   |                                                                                     | 4.2.1          | Identity based on a Single Component                                      | . 67 |  |

|   |                                                                                     | 4.2.2          | Low Entropy and Few Challenge-Response Pairs (CRPs) $\ . \ . \ .$         | . 69 |  |

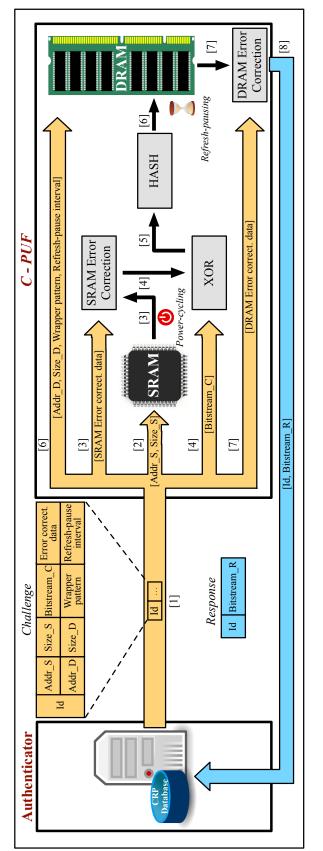

|   | 4.3                                                                                 | C-PUI          | F: A Memory-based Combination PUF                                         | . 70 |  |

|   |                                                                                     | 4.3.1          | Challenge-Response Mechanism                                              | . 73 |  |

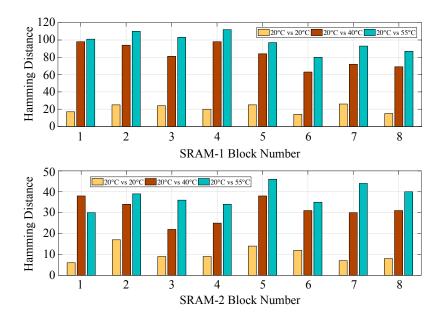

|   |                                                                                     | 4.3.2          | SRAM Error Correction                                                     | . 75 |  |

|   |                                                                                     | 4.3.3          | DRAM Error Correction                                                     | . 79 |  |

|   |                                                                                     | 4.3.4          | Device Authentication using C-PUF                                         | . 80 |  |

|   |                                                                                     | 4.3.5          | Intrinsic Reconfigurability                                               | . 86 |  |

|   | 4.4                                                                                 | Experi         | imental Setup                                                             | . 88 |  |

|   |                                                                                     | 4.4.1          | Implementation Overhead and Performance                                   | . 90 |  |

|   | 4.5                                                                                 | Results        |                                                                           |      |  |

|   |                                                                                     | 4.5.1          | Entropy Analysis                                                          | . 91 |  |

|   |                                                                                     | 4.5.2          | CRP Analysis                                                              | . 96 |  |

|   |                                                                                     | 4.5.3          | Robustness Analysis: Authentication under Varying Operating<br>Conditions | . 97 |  |

|   |                                                                                     | 4.5.4          | Replacing Genuine DRAM with a Counterfeit                                 | 102  |  |

|   |                                                                                     | 4.5.5          | Intrinsic Reconfigurability: A Sample Timeline                            | 104  |  |

|   | 4.6                                                                                 | Discus         | sions                                                                     | 105  |  |

|   |                                                                                     | 4.6.1          | Attack Scenarios                                                          | 105  |  |

|   |                                                                                     | 4.6.2          | C-PUF versus [SRAM PUF + DRAM PUF]                                        | 107  |  |

|   |                                                                                     | 4.6.3          | Effect of Variations in Supply Voltage                                    | 108  |  |

|   | 4.7                                                                                 | Conclu         | usion                                                                     | 108  |  |

| 5 | A LIGHTWEIGHT END-TO-END AUTHENTICATION PROTOCOL FOR<br>IMPLANTABLE MEDICAL DEVICES |                |                                                                           |      |  |

|   | 5.1                                                                                 | Chapt          | er Contributions                                                          | 111  |  |

|    |      |         |                                                                | Page |

|----|------|---------|----------------------------------------------------------------|------|

|    | 5.2  | Motiva  | tion                                                           | 112  |

|    |      | 5.2.1   | Challenges with the Trusted-entity and PUF-based Approaches    | 115  |

|    | 5.3  | An En   | d-to-End Authentication and Key-exchange Protocol for IMDs     | 116  |

|    |      | 5.3.1   | Enrollment Phase                                               | 118  |

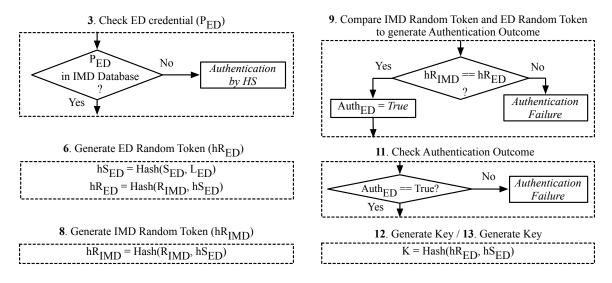

|    |      | 5.3.2   | Authentication Phase                                           | 119  |

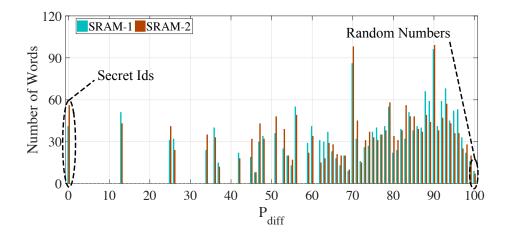

|    |      | 5.3.3   | Generation of Secret IDs and True Random Numbers $\ . \ . \ .$ | 129  |

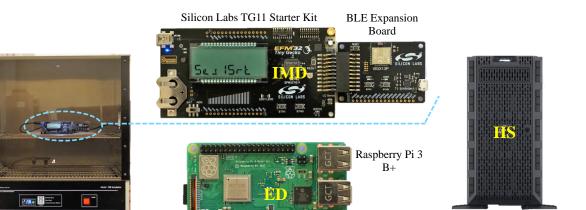

|    | 5.4  | Implen  | nentation and Analysis                                         | 129  |

|    |      | 5.4.1   | Prototypes and Experimental Setup                              | 129  |

|    |      | 5.4.2   | Overhead Analysis at the IMD                                   | 131  |

|    |      | 5.4.3   | Security Analysis                                              | 133  |

|    | 5.5  | Additio | onal Discussions and Results                                   | 135  |

|    |      | 5.5.1   | SRAM PUF: Generation of Secret IDs and Random Numbers          | 135  |

|    |      | 5.5.2   | Emergency Access to the IMD                                    | 138  |

|    | 5.6  | Conclu  | sion                                                           | 138  |

| 6  | SUM  | MARY    |                                                                | 140  |

| RF | EFER | ENCES   | \$                                                             | 142  |

| VI | TA   |         |                                                                | 150  |

## LIST OF TABLES

| Table |                                                                                               |      |

|-------|-----------------------------------------------------------------------------------------------|------|

| 3.1   | Parameter values used in our evaluation                                                       | . 44 |

| 4.1   | Parameter values and operating conditions varied during DRAM Error Characterization           |      |

| 4.2   | (SRAM, DRAM) used in different <i>C-PUF</i> instances                                         | . 87 |

| 4.3   | Parameter values used in the experiments                                                      | . 87 |

| 4.4   | $\mathrm{HD}_{\mathrm{Response}}$ values for different parameters                             | . 95 |

| 4.5   | Hamming Encoder-Decoder $\langle n, k \rangle$ values for different <i>enrollment point</i> . | s 98 |

| 4.6   | Match Threshold and [Maximum Corrected Bits] values at different au-<br>thentication points   | . 99 |

| 5.1   | Capabilities of the different entities in the IMD ecosystem                                   | 113  |

| 5.2   | Notations and terminology used in the protocol                                                | 117  |

| 5.3   | Protocol Overhead at the IMD                                                                  | 132  |

## LIST OF FIGURES

| Figu | re Pa                                                                       | ige |

|------|-----------------------------------------------------------------------------|-----|

| 1.1  | Security and Privacy Concerns in the IoT                                    | 2   |

| 1.2  | Building a secure IoT network through Device Authentication                 | 3   |

| 1.3  | Research contributions made by this dissertation                            | 4   |

| 2.1  | Overview of challenge-response-based authentication                         | 11  |

| 2.2  | A 1T-1C DRAM bit-cell                                                       | 14  |

| 2.3  | A 6T SRAM bit-cell                                                          | 15  |

| 2.4  | An End-to-End IMD Ecosystem                                                 | 18  |

| 3.1  | Examples of embedded systems containing DRAM                                | 22  |

| 3.2  | Authentication using D-PUF                                                  | 27  |

| 3.3  | Challenge and Response Format and CRP database                              | 28  |

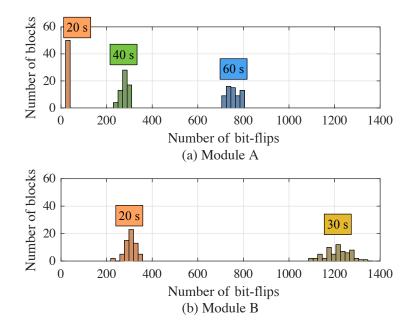

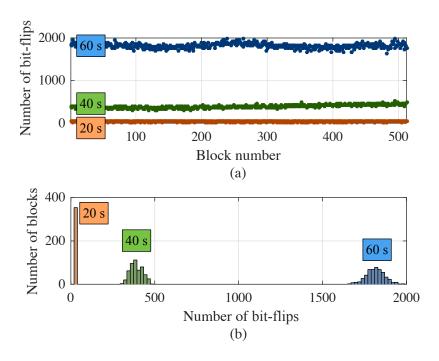

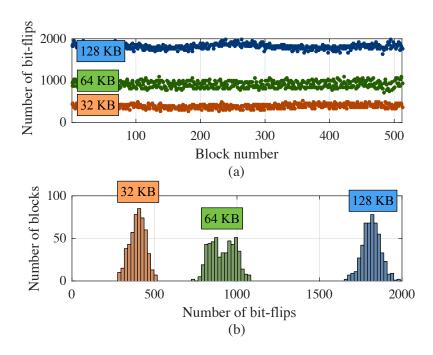

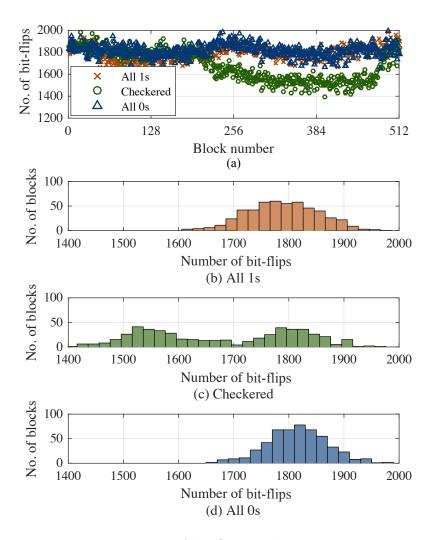

| 3.4  | Variation of bit-flips across different DRAM modules                        | 30  |

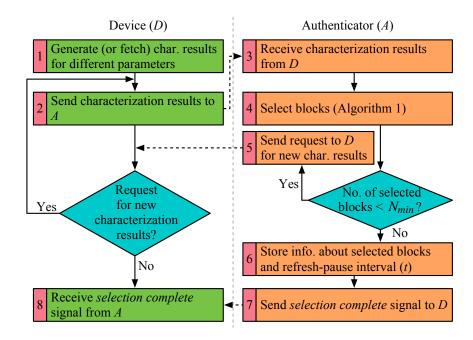

| 3.5  | D-PUF Characterization phase                                                | 31  |

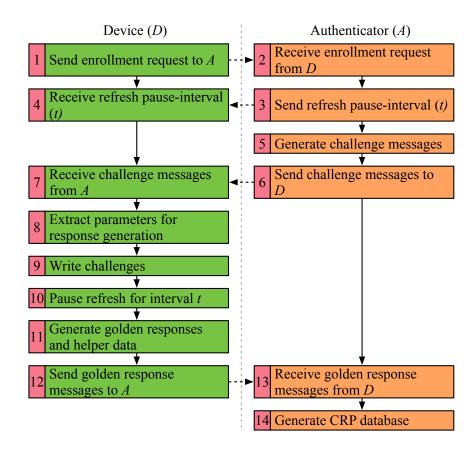

| 3.6  | D-PUF Enrollment phase                                                      | 35  |

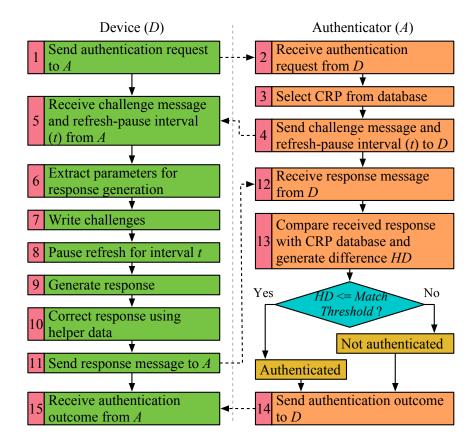

| 3.7  | D-PUF Authentication phase                                                  | 37  |

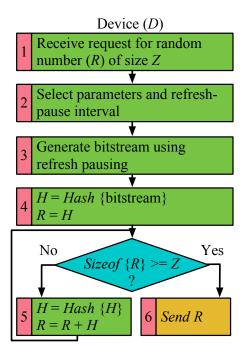

| 3.8  | Random number generation using D-PUF                                        | 39  |

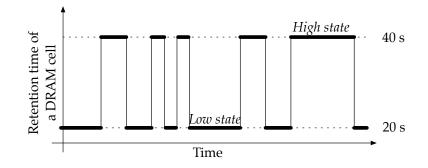

| 3.9  | Different retention states in a DRAM cell due to VRT                        | 40  |

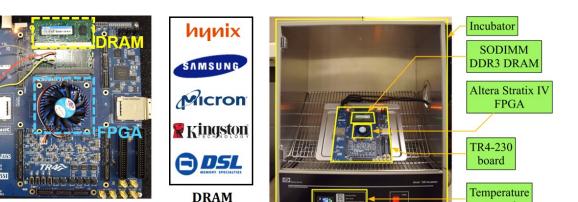

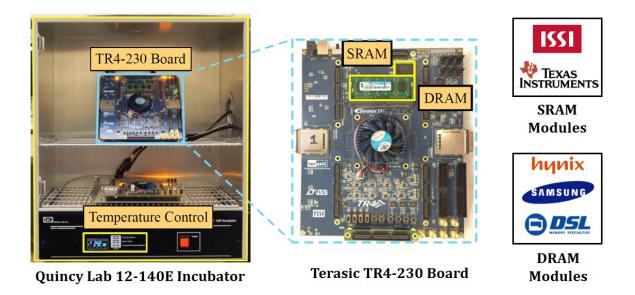

| 3.10 | Experimental setup                                                          | 41  |

| 3.11 | Variation of bit-flips with refresh-pause interval                          | 45  |

| 3.12 | Variation of bit-flips with block-size                                      | 45  |

| 3.13 | Variation of bit-flips with wrapper pattern                                 | 46  |

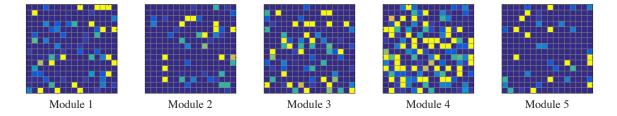

| 3.14 | Unique responses generated from different DRAM modules                      | 47  |

| 3.15 | Unique responses generated from the same DRAM Module                        | 48  |

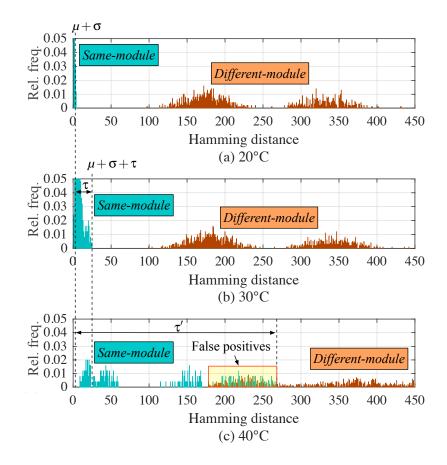

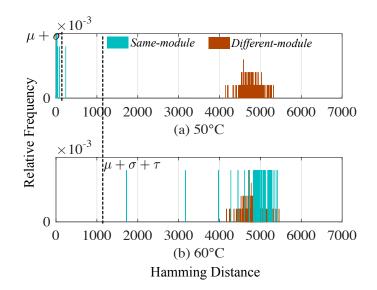

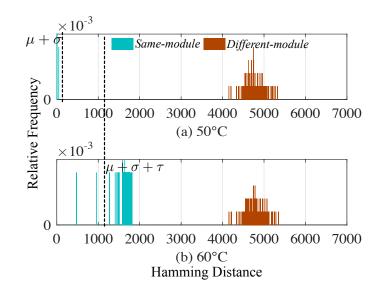

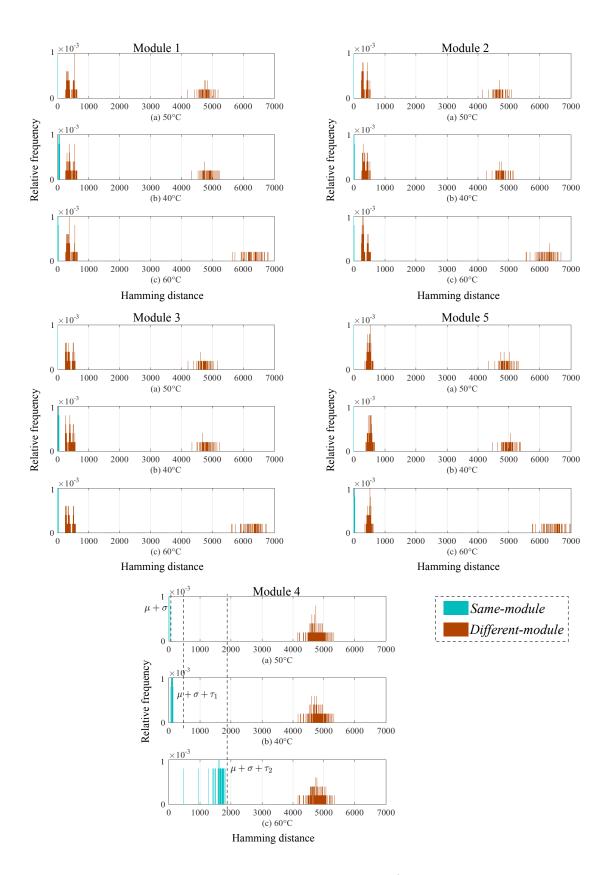

| 3.16 | Robustness across different temperatures (naive approach) $\ . \ . \ . \ .$ | 49  |

| 3.17 | Inadequate error correction                                                 | 52  |

| Figu | re                                                                                                                                                                                                              | Рε | age |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 3.18 | Adequate error correction with static $MT$                                                                                                                                                                      |    | 53  |

| 3.19 | Robustness across different temperatures (dynamic $MT$ with adequate error correction) $\ldots \ldots \ldots$ |    | 55  |

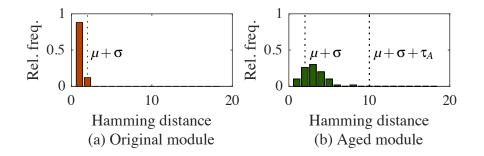

| 3.20 | Robustness under aging                                                                                                                                                                                          |    | 57  |

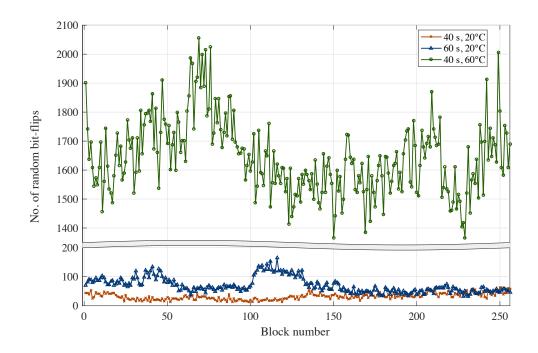

| 3.21 | Variation of <i>random bit-flips</i> with refresh-pause interval and temperature                                                                                                                                |    | 58  |

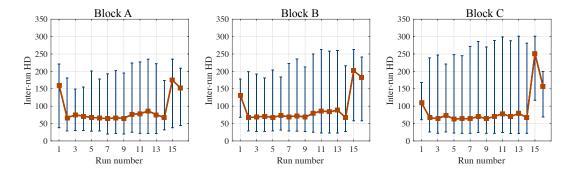

| 3.22 | Inter-run HD across 16 runs spread over 24 hours                                                                                                                                                                |    | 59  |

| 3.23 | NIST Statistical Test Suite results                                                                                                                                                                             |    | 60  |

| 4.1  | Examples of IoT devices containing multiple memory technologies                                                                                                                                                 |    | 66  |

| 4.2  | Authentication using – (a) a Single Component and (b) Multiple Components in a system                                                                                                                           |    | 68  |

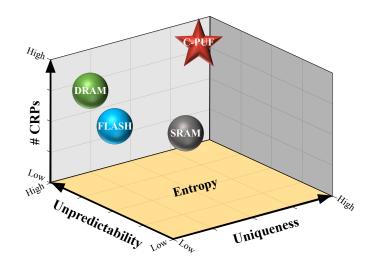

| 4.3  | Qualitative comparison of different memory-based PUFs                                                                                                                                                           |    | 69  |

| 4.4  | Overview of the proposed $\ensuremath{\textit{C-PUF}}$ design utilizing SRAM and DRAM                                                                                                                           |    | 72  |

| 4.5  | Variations in SRAM startup values with temperature                                                                                                                                                              |    | 76  |

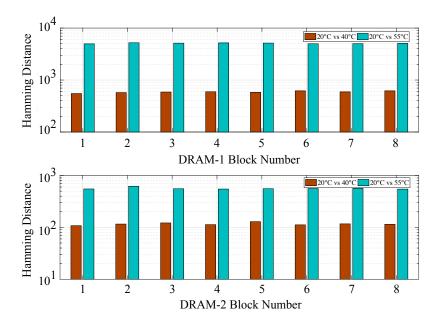

| 4.6  | Variations in DRAM responses with temperature                                                                                                                                                                   |    | 80  |

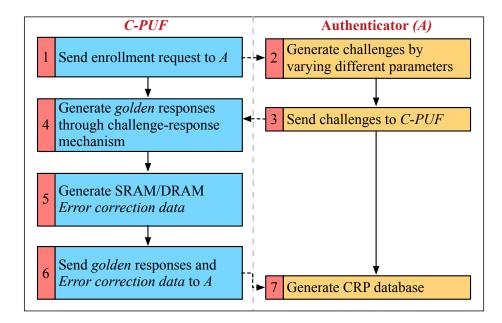

| 4.7  | Flowchart showing the <i>enrollment phase</i> in <i>C-PUF</i>                                                                                                                                                   |    | 81  |

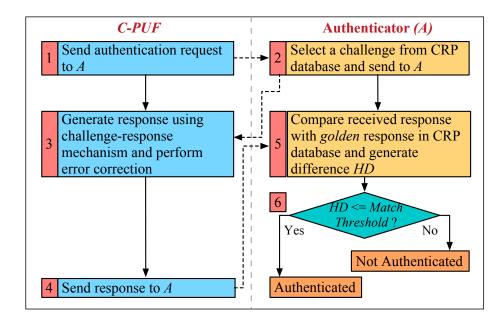

| 4.8  | Flowchart showing the <i>authentication phase</i> in <i>C-PUF</i>                                                                                                                                               |    | 82  |

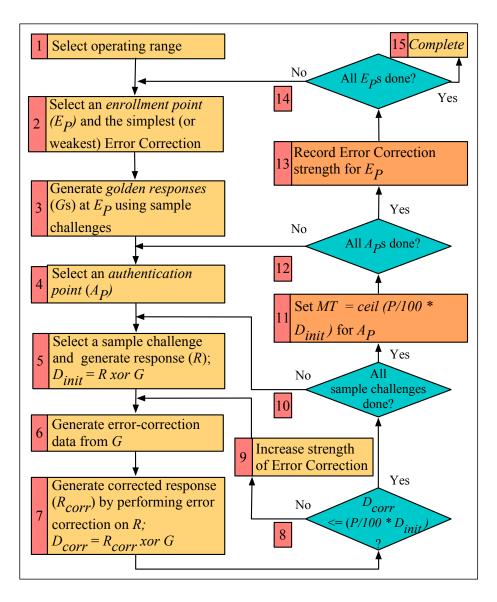

| 4.9  | Flowchart showing setting of Match Threshold                                                                                                                                                                    |    | 84  |

| 4.10 | Experimental Setup                                                                                                                                                                                              |    | 89  |

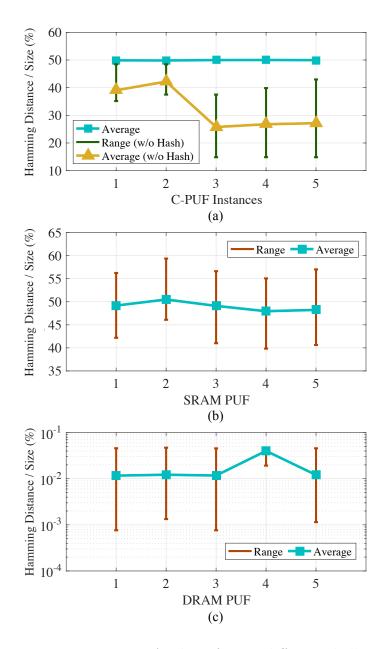

| 4.11 | Uniqueness Analysis for ten different challenges                                                                                                                                                                |    | 93  |

| 4.12 | Responses (fingerprints) from different C-PUF instances                                                                                                                                                         |    | 94  |

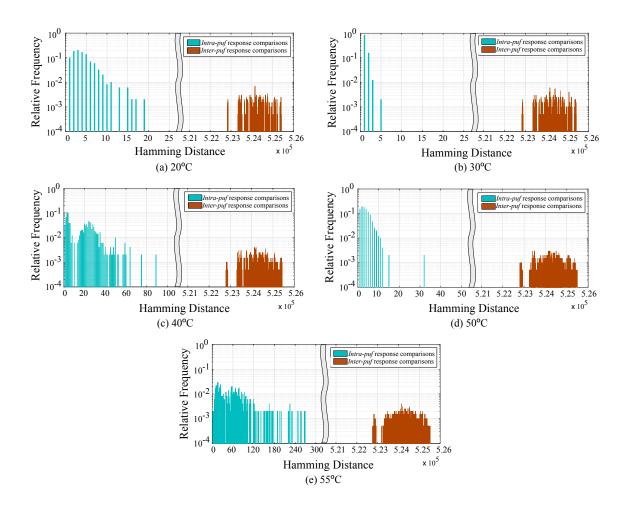

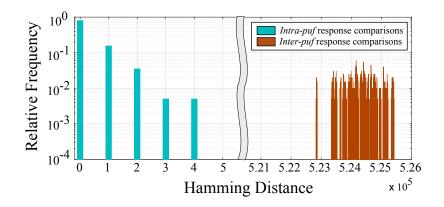

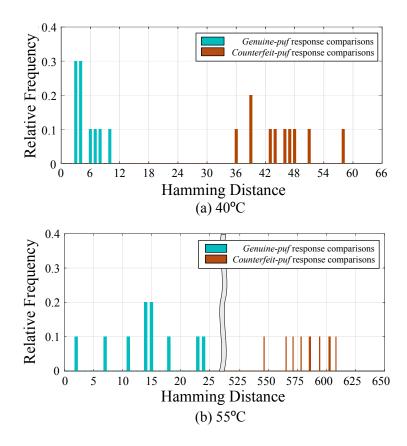

| 4.13 | Authentication under temperature variations                                                                                                                                                                     | 1  | 100 |

| 4.14 | Authentication under aging effects                                                                                                                                                                              | 1  | 101 |

| 4.15 | Authentication of PUF-2C versus PUF-2                                                                                                                                                                           | 1  | 102 |

| 4.16 | Authentication of PUF-4C versus PUF-4                                                                                                                                                                           | 1  | 103 |

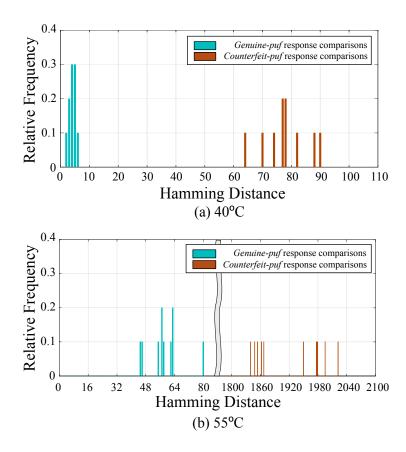

| 4.17 | Reconfiguration timeline                                                                                                                                                                                        | 1  | 105 |

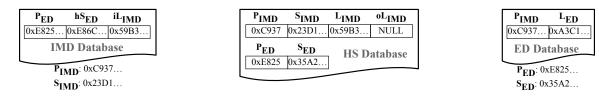

| 5.1  | Enrollment Phase                                                                                                                                                                                                | 1  | 18  |

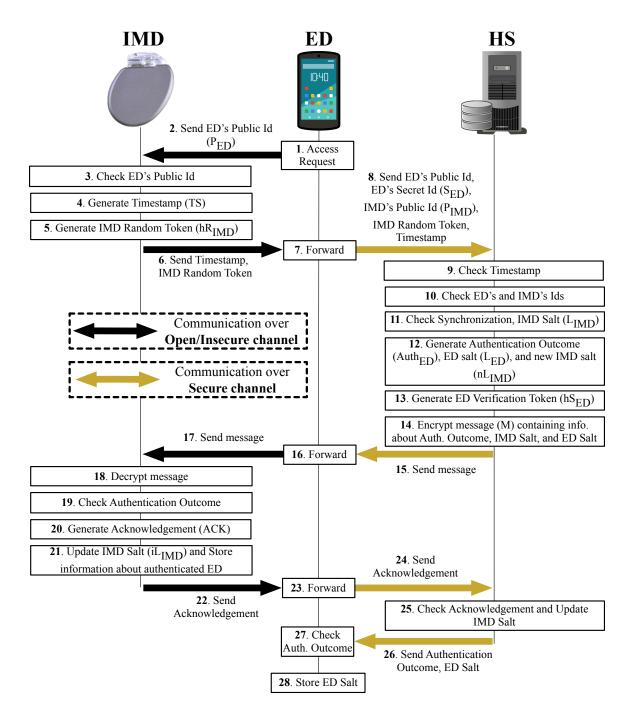

| 5.2  | Authentication by HS                                                                                                                                                                                            | 1  | 121 |

| 5.3  | Steps in Authentication by HS                                                                                                                                                                                   | 1  | 122 |

| 5.4  | Database after Authentication by HS                                                                                                                                                                             | 1  | 125 |

| Figure |                                                |     |

|--------|------------------------------------------------|-----|

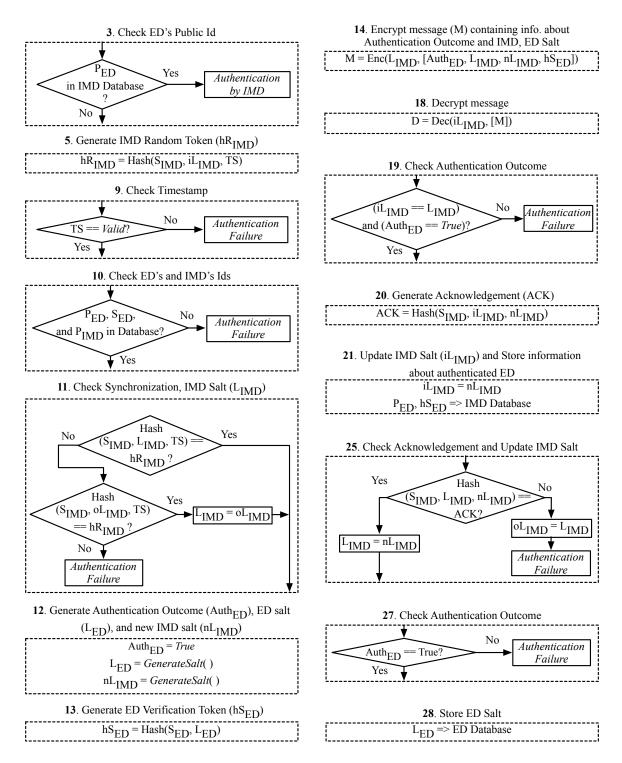

| 5.5    | Authentication by IMD                          | 127 |

| 5.6    | Steps in Authentication by IMD                 | 128 |

| 5.7    | Prototype IMD Ecosystem and Experimental Setup | 130 |

| 5.8    | Secret IDs and Random Numbers in the SRAM PUF  | 137 |

#### ABSTRACT

Sutar, Soubhagya Ph.D., Purdue University, August 2020. Memory-based Hardwareintrinsic Security Mechanisms for Device Authentication in Embedded Systems. Major Professor: Vijay Raghunathan.

The Internet-of-Things (IoT) is one of the fastest-growing technologies in computing, revolutionizing several application domains such as wearable computing, home automation, industrial manufacturing, *etc.* This rapid proliferation, however, has given rise to a plethora of new security and privacy concerns. For example, IoT devices frequently access sensitive and confidential information (*e.g.*, physiological signals), which has made them attractive targets for various security attacks. Moreover, with the hardware components in these systems sourced from manufacturers across the globe, instances of counterfeiting and piracy have increased steadily. Security mechanisms such as device authentication and key exchange are attractive options for alleviating these challenges.

In this dissertation, we address the challenge of enabling low-cost and low-overhead device authentication and key exchange in off-the-shelf embedded systems. The first part of the dissertation focuses on a hardware-intrinsic mechanism and proposes the design of two Physically Unclonable Functions (PUFs), which leverage the memory (DRAM, SRAM) in the system, thus, requiring minimal (or no) additional hardware for operation. Two lightweight authentication and error-correction techniques, which ensure robust operation under wide environmental and temporal variations, are also presented. Experimental results obtained from prototype implementations demonstrate the effectiveness of the design. The second part of the dissertation focuses on the application of these techniques in real-world systems through a new end-to-end authentication and key-exchange protocol in the context of an Implantable Medical Device (IMD) ecosystem. Prototype implementations exhibit an energy-efficient design that guards against security and privacy attacks, thereby making it suitable for resource-constrained devices such as IMDs.

### 1. INTRODUCTION

Over the past few years, the Internet-of-Things (IoT) has pervaded all aspects of our daily lives. It has fundamentally altered the way we interact with our physical environment, thereby revolutionizing a number of application domains such as home automation, wearable computing, industrial manufacturing, etc. The IoT is also one of the fastest-growing technologies across all of computing and it is expected that there would 125 billion devices connected to it by the year 2030 [1]. However, this rapid proliferation coupled with the increasingly connected nature of these devices has given rise to a plethora of new security and privacy concerns, as shown in Fig. 1.1. One such example is data theft. Though preventing it has been a challenge right from the beginning of personal computing, the problem has assumed a completely new scale due to the sheer number of these smart devices with the ability to access potentially sensitive and confidential information (e.q., banking credentials, physiological signals, etc.). Moreover, the diversity of these devices, ranging from tiny microcontrollers to large datacenter servers, makes it near impossible to employ a standard security solution. Another concern stems from the the cyber-physical nature of these devices, as a result of which, security attacks have physical consequences. For example, in 2015, attackers were able to get remote access to a Jeep Cherokee and kill some of its vital systems such as steering, braking, transmission, etc [2]. Also, there have been numerous security vulnerabilities identified in medical devices that could be exploited by attackers to cause serious harm to the patient [3, 4]. Finally, with the hardware components in these systems sourced from manufacturers across the globe, instances of counterfeiting and piracy have increased steadily. Counterfeit components not only have serious reliability implications, but also cause tremendous revenue loss to the electronics industry [5].

Fig. 1.1.: Security and Privacy Concerns in the IoT

### 1.1 Research Contributions and Dissertation Overview

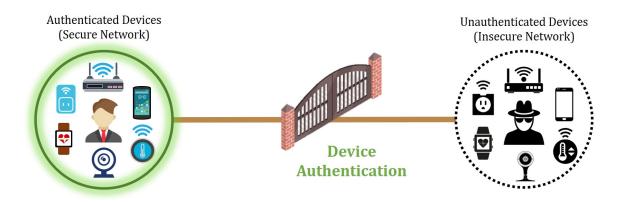

The previous section highlighted several concerns associated with the rapid growth of the IoT in recent years. One way of addressing several of these, which the dissertation focuses on, is *device authentication*. Authentication, in general, refers to any process by which a system verifies the identity of a user who wishes to access it. In the context of the IoT, the user may refer to a client device trying to connect to a network while the system is a trusted authority and may refer to the network gateway. By ensuring that each of these devices is *authentic*, in other words, by performing device authentication, a secure network can be built, as shown in Fig. 1.2.

Traditionally, device authentication has been carried out using static techniques such as passwords, secret keys, public-key infrastructure (PKI), *etc.* However, these techniques have several shortcoming such as the need for user intervention and vulnerability to present-day sophisticated attacks. Most importantly, a large number of the IoT devices are low-cost in nature and lack the resources – compute, memory, en-

Fig. 1.2.: Building a secure IoT network through Device Authentication

ergy, *etc.*, which are required by some of these authentication techniques. All of these motivate us to look into alternate techniques for performing device authentication. One such technique is based on the use of hardware-intrinsic security mechanisms such as Physically Unclonable Functions (PUFs) [6]. PUFs exploit the random physical variations inherent to any manufacturing process to generate device-specific and unclonable fingerprints. These unique fingerprints can be used as the basis for the challenge-response mechanism for device authentication as well as for random number (*e.g.*, secure key) generation. While a large variety of PUF implementations have been proposed, this dissertation leverages memory-based PUFs due to the ubiquitous presence of memory in virtually every embedded system. Moreover, memory-based PUFs require minimal or no additional circuitry for their operation, giving them a distinct advantage over other PUF implementations. Hence, towards enabling lowcost and low-overhead device authentication in embedded systems, the dissertation makes the following research contributions, as shown in Fig. 1.3:

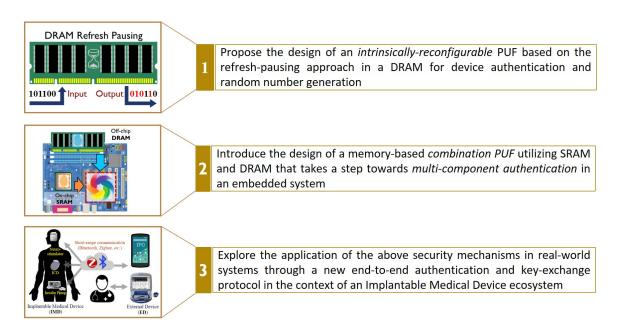

• The dissertation proposes the design of an *intrinsically-reconfigurable* PUF based on the refresh-pausing approach in a DRAM for device authentication and random number generation [7,8].

Fig. 1.3.: Research contributions made by this dissertation

- It introduces the design of a memory-based *combination PUF* utilizing SRAM and DRAM that takes a step towards *multi-component authentication* in an embedded system [9].

- It explores the application of the above security mechanisms in real-world systems through a new end-to-end authentication and key-exchange protocol in the context of an Implantable Medical Device ecosystem [10].

Next, we briefly introduce the work associated with each of the above contributions - a detailed discussion follows in the subsequent chapters.

# 1.1.1 An Intrinsically-Reconfigurable DRAM PUF for Device Authentication and Random Number Generation

Chapter 3 introduces the design of an intrinsically-reconfigurable PUF [7,8] based on the Dynamic Random Access Memory (DRAM). DRAM is used as the main memory in a large number of modern embedded systems due to its high density and low cost. As is well-known, DRAM cells must be refreshed periodically to preserve the stored data. This need for refresh operations also makes DRAM an attractive candidate for use as a PUF, especially for challenge-response-based authentication and random number generation. The key idea of a DRAM PUF based on refresh pausing is as follows (a more detailed explanation is given in Chapter 3). If data is stored in a large (say 64KB) block of DRAM cells and refresh operations to the entire block are paused for an extended amount of time (henceforth referred to as the refresh-pause interval), some of the DRAM cells in the block will lose their data. How many and which cells in the DRAM block lose their contents (for a given refresh-pause interval) is unique to a device and can, therefore, be used as the basis for implementing a PUF.

Prior approaches to DRAM-based PUFs suffer from several shortcomings such as low speed of authentication [11], non-applicability to commercial off-the-shelf (COTS) devices [12], and the need for power cycling the DRAM module prior to authentication [13]. Moreover, the near static nature of the response generation mechanism in some of the works [11, 13] makes them vulnerable to various security attacks [14]. To address these limitations, we propose a DRAM PUF, henceforth referred to as D-PUF, based on refresh pausing that not only supports a very large number of challenge-response pairs (CRPs) through the variation of different parameters, but is also *intrinsically reconfigurable*, *i.e.*, its challenge-response behavior can be substantially modified without the use of any additional circuitry. Hence, the PUF can be easily implemented in most off-the-shelf systems and provides considerable protection from various security attacks. We also use D-PUF to design a secure, low-overhead mechanism for performing device authentication. The mechanism operates robustly even in the presence of environmental and temporal variations. We implement D-PUF and our proposed authentication mechanism in a real system using off-the-shelf DRAM modules and evaluate it thoroughly. In particular, we demonstrate a 4.3X-6.4X reduction in authentication time, compared to previous work. Using controlled temperature and accelerated aging tests, we demonstrate the robustness of our authentication mechanism to temperature and aging effects. For a sample temperature range of 10°C to 60°C, we show that the mechanism achieves a 100% true-positive (successful authentication) rate and 0% false-positive rate. For a ten-month-old DRAM module, it also ensures a 100% true-positive rate and 0% false-positive rate. We also implement a True Random Number Generator (TRNG) using D-PUF by exploiting the Variable Retention Time (VRT) phenomenon in DRAMs and demonstrate that the generated random numbers pass all the tests specified in the NIST Statistical Test Suite.

# 1.1.2 Memory-Based Combination PUFs for Device Authentication in Embedded Systems

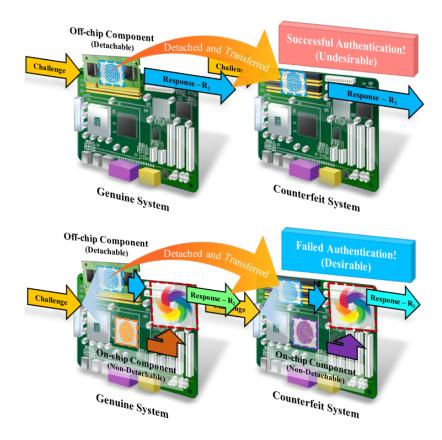

Current memory-based PUFs are constructed using a single memory component in the device, *i.e.*, based on a single entropy source. This means that the PUF represents the identity of the component and not that of the system. If the component is removed and transferred to a different system (invasive attack), the identity transfers over as well, which is undesirable. Moreover, the use of a single memory component makes it vulnerable to sophisticated non-invasive attacks [14]. To mitigate these concerns, it is desirable that the PUF be dependent on multiple system components (some of which may be more tightly integrated into the system than others), thereby performing *multi-component authentication*. Recent works [15,16] have tried to address a subset of these shortcomings. However, the choice of entropy sources used in these PUF designs renders them unsuitable for multi-component authentication. They also require the addition of custom hardware to the system and, hence, cannot be implemented using Commercial-Off-The-Shelf (COTS) systems.

As presented in Chapter 4, this dissertation overcomes these limitations by proposing the design of a memory-based combination PUF, henceforth referred to as C-PUF [9]. By tightly integrating heterogeneous memory technologies, C-PUF exhibits high entropy alongside an exponential number of CRPs, and takes the first step towards multi-component authentication in an embedded device. The heterogeneous nature of the entropy sources (memories) used and C-PUF's ability to undergo *intrinsic reconfiguration* (ability to reconfigure the PUF at runtime without any additional hardware) protects it from various security attacks. C-PUF also features a lightweight authentication scheme to ensure robust operation (authentication) under wide environmental and temporal variations. We implement, demonstrate, and evaluate several fully-functional prototypes of C-PUF in a real system using two widely-used memory technologies, Static Random Access Memories (SRAMs) and Dynamic Random Access Memories (DRAMs). Extensive authentication tests performed across a wide temperature range ( $20^{\circ}C - 55^{\circ}C$ ) and accelerated aging ( $12 \mod s$ ) achieved greater than 97.5% true-positive rate. The absence of any false-positives, even under an invasive attack, further highlights the effectiveness of the overall design.

# 1.1.3 A Lightweight End-to-End Authentication Protocol for Implantable Medical Devices

The past decade has witnessed a rapid growth in the use of IMDs for monitoring and treating a variety of medical conditions, with their global market valuation expected to reach \$50 billion by 2024 [17]. IMDs are increasingly being equipped with wireless interfaces [18], allowing them to communicate with an External Device (ED) such as a doctor's programmer or a patient's smartphone. While this greatly improves standard of care (allowing for post-deployment tuning of therapy as needed and remote, real-time access to health data), it also exposes the IMD to a range of security concerns [3, 4, 19–21] such as potential interaction with untrusted EDs and potential leakage of confidential medical data.

Several techniques [22–30] have been proposed to address these concerns. One such technique [28,30] leverages a *trusted entity* such as a Health Server (HS), which assumes the role of an authenticator and arbitrates access to an IMD when an ED requests it. However, there are three unaddressed challenges with this approach. First, due to their severely limited energy budget, IMDs [18] typically utilize shortrange communication technologies such as Bluetooth LE and, hence, do not have direct network connectivity with a remote HS. This is in contrast to an ED, such as a smartphone, which can use long-range wireless technologies such as Wi-Fi, LTE, *etc.*, for network access. Second, involving the HS for every single authentication session can incur significant energy overheads at the IMD, besides increasing the load on the HS and the network. This, in turn, gives rise to the third challenge. If the HS is not reachable over the network, the IMD and ED cannot securely communicate with each other. Besides, some of these techniques [28, 29] require the (resourceconstrained) IMD to perform asymmetric cryptography operations resulting in high energy overhead.

Chapter 5 presents the design of a lightweight end-to-end authentication and keyexchange protocol [10] based on the trusted-entity approach that fully addresses each of the aforementioned challenges. A key requirement of the proposed protocol is the availability/generation of unique identifiers/keys and random numbers on demand. Although other techniques such as statically-stored secret keys and pseudo-random number generators could be utilized, we utilize a PUF to satisfy this requirement and present its seamless integration with existing cryptography techniques in the protocol. The result is a robust, secure, and lightweight protocol, which protects against various security attacks [19–21] and can be easily implemented using Commercial-Off-The-Shelf (COTS) devices with minimal or no additional hardware resources. It also overcomes the shortcomings associated with prior PUF-based authentication techniques [29–32] and those of earlier trusted-entity approaches [28].

The rest of this dissertation is organized as follows. Chapter 2 serves as the necessary background for this dissertation and also discusses prior work. Chapter 3 presents the design of the proposed DRAM PUF alongside a robust, low-overhead mechanism for performing device authentication across temporal and environmental variations. Chapter 4 motivates the need for multi-component authentication in an embedded system and presents the design of the proposed memory-based combination PUF. Next, Chapter 5 highlights the need for authentication and key-exchange in an

IMD ecosystem and presents the design of the proposed lightweight authentication and key-exchange protocol. Finally, Chapter 6 concludes the dissertation.

### 2. BACKGROUND AND RELATED WORK

As discussed in the previous chapter, there are several challenges associated with building a secure IoT. One way of addressing several of these challenges, which the current dissertation focuses upon, is device authentication. In this dissertation, we present three research works towards enabling low-cost and low-overhead device authentication in embedded systems. Before moving into the details of their design, we discuss the necessary background and related work in this chapter.

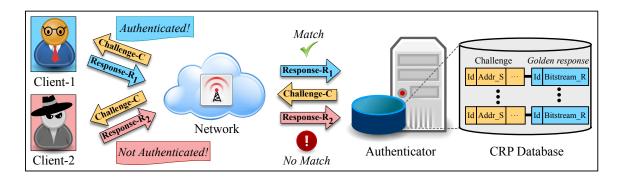

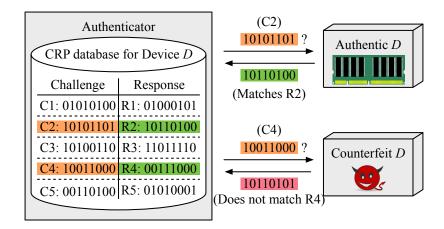

#### 2.1 Device Authentication

Authentication can be defined as a process by which a trusted system (authenticator) verifies the identity of an untrusted entity (client) before granting it access to any data or resources. It is usually performed using a challenge-response mechanism [8,33], as depicted in Fig. 2.1. The authenticator hosts a service that is restricted to genuine clients only. Note that, in other cases, the authenticator may not host the service itself but only arbitrate access to a server that does. To verify the identity of a client, the authenticator first provides it with a challenge. The client then generates a response to the challenge. Prior to this, the authenticator creates a Challenge-Response Pair (CRP) database (Fig. 2.1) that stores all the challenges and their expected responses from genuine clients. By comparing the current client's response against the one stored in the CRP database, the authenticator infers whether the client is genuine or not. As shown, Client-1 (genuine) passes authentication and is granted access to the service as its response  $(R_1)$  to the challenge (C) matches with the CRP database. On the contrary, the response  $(R_2)$  generated by Client-2 (fake) is different from the expected response of a genuine client, and hence Client-2 is not authenticated.

Fig. 2.1.: Overview of challenge-response-based authentication

In the context of the IoT, this challenge-response mechanism leads us to *device authentication*. The client, here, could refer to a device trying to connect to a (private) network while the authenticator is a trusted authority and could refer to the network gateway. By ensuring that each of these devices is *authentic*, in other words, by performing device authentication, a secure network can be built (Fig. 1.2).

#### 2.2 Physically Unclonable Functions (PUFs)

Traditionally, device authentication has been carried out using static techniques such as passwords, secret keys, public-key infrastructure (PKI), *etc.* However, these techniques have several shortcoming such as the need for user intervention and vulnerability to present-day sophisticated attacks. Most importantly, a large number of the IoT devices are low-cost in nature and lack the resources – compute, memory, energy, *etc.*, which are required by some of these authentication techniques. All of these motivate us to look into alternate techniques for performing device authentication. One such technique is based on the use of hardware-intrinsic security mechanisms such as Physically Unclonable Functions (PUFs) [6]. A PUF maps a set of challenges to a set of responses based on random physical variations during the manufacturing of a device (containing the PUF). As a result, the challenge-response behavior of the PUF is highly unpredictable. Also, the fact that it is impossible to manufacture a PUF with the same behavior as another makes it unclonable and unique. These features make PUF an ideal candidate for authentication and random number generation. Randomly generated secret keys are used by various cryptographic applications such as keyed-hash message authentication code (HMAC), encryption/decryption, *etc.*, besides serving as unique fingerprints or signatures that can be used to identify a device. A PUF enables the generation of secret keys on demand rather than permanently storing them in non-volatile memory, drastically reducing the implications of physically invasive attacks. Device authentication can be considered an extension of the above key-generation process but involves the challenge-response mechanism, described earlier, to authenticate the device (client). The authenticator sends the challenge to the device, which utilizes the PUF present inside it to respond to the challenge.

One of the earliest works on PUFs was carried out in [34], resulting in an optical PUF based on the scatter pattern of a laser beam. Ref. [6] introduced the concept of silicon PUFs and provided various circuit realizations that could be integrated into an electronic circuit. Due to this ease of integration, silicon PUFs have become extremely popular in present day implementations. Two such examples are Ring Oscillator and Arbiter PUFs [33] that exploit the inherent delay characteristics in IC components for authentication and generation of secret keys. However, both these implementations require dedicated circuitry that is added solely for the PUF operation and present an area overhead. Memory-based PUFs, which form another type of silicon PUFs and are utilized in this dissertation, are discussed next. Ref. [35] proposed a generic PUF architecture targeted towards preventing modeling attacks.

#### 2.2.1 Memory-based PUFs

Memory-based PUFs utilize the memory module (SRAM, DRAM, *etc.*) already present on the IC/SoC and require minimal (or no) additional circuitry for their operation, giving them a distinct advantage over other PUF implementations. Hence, this dissertation utilizes two such PUFs – DRAM PUF and SRAM PUF, based on the *refresh-pausing* and *power-cycling* approaches, respectively. These are explained next.

#### 2.2.2 DRAM: Structure and PUF mechanisms

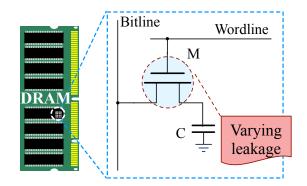

Fig. 2.2 shows the fundamental building blocks of a DRAM bit cell, namely an access transistor (M) and capacitor (C). The bit-value is decided by the charge on the capacitor; full charge implies '1' and no charge implies '0', or vice-versa. This charge leaks over time due to several factors related to the non-ideality of the access transistor and eventually results in the loss of data stored in the cell. This phenomenon is referred to as a *bit-flip* ('1' $\rightarrow$ '0' or '0' $\rightarrow$ '1') in DRAMs. To prevent this, the DRAM memory-controller refreshes the cells (replenishes the charge) periodically (*e.g.*, every 64ms). Due to process variations, the rate of leakage (or bit-flip) varies widely across DRAMs (and within the same DRAM). This forms the basis of the *refresh-pausing* approach in a DRAM PUF [7, 8, 11, 36, 37], in which refresh operations are (intentionally) paused for a certain time-interval, generating unique bit-flip patterns in the DRAM data. This data is then read out and forms the PUF's response. Unlike the SRAM PUF (described above), the parameters in a DRAM PUF's challenge can be extensively varied [8], supporting an exponential number of CRPs (Section 4.3.1).

Several DRAM PUFs have been proposed by researchers over the years. Reduction of the write-duty cycle in a DRAM module is employed in [12] to implement a strong PUF. However, the reduction is achieved by adding a delay generator to the writecircuitry of the DRAM module. This not only requires very precise control over the *write* signal but is also not applicable to off-the-shelf DRAM modules. Ref. [11] utilizes refresh pausing to generate unique identifiers and random numbers from a DRAM module. However, it employs a constant (and large) refresh-pause interval of 256 s -8192 s that could be considered too slow for authentication. A decay-based (or refreshpausing-based) DRAM PUF that can be accessed during run-time in a commodity device is presented in [38]. However, just like [11], the lack of DRAM characterization

Fig. 2.2.: A 1T-1C DRAM bit-cell

in the proposed design leads to the usage of large refresh-pause intervals (120 s - 320 s) and hence, leads to slow authentication. Ref. [39] generates random numbers from DRAM using remanence effects but requires power-cycling (power off  $\rightarrow$  power on  $\rightarrow$  read data) of the DRAM module. The power-cycling approach has also been utilized to generate the fingerprint from the start-up values of a DRAM module [13, 40]. Modifying read access latency to generate error patterns formed the basis of the DRAM PUF presented in [41]. Other approaches to realizing DRAM PUFs [42] have also been developed. However, the *refresh-pausing*-based DRAM PUF, which this dissertation utilizes, remains as one of the most popular and widely-adopted in several state-of-the-art systems.

#### 2.2.3 SRAM: Structure and PUF mechanisms

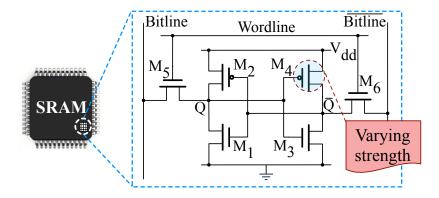

Each cell (or bit) in a Static Random Access Memory (SRAM) is arranged in a six-transistor configuration<sup>1</sup> consisting of cross-coupled CMOS inverters ( $M_1-M_4$ ) and access transistors ( $M_5-M_6$ ), as shown in Fig. 2.3. Powering-up the SRAM causes each cell to reach one of two states, [Q=1,  $\overline{Q}=0$ ] or [Q=0,  $\overline{Q}=1$ ], depending upon the relative strengths of the transistors as well as noise.

<sup>&</sup>lt;sup>1</sup>While other SRAM cells do exist, the 6-transistor cell is commonly used.

Fig. 2.3.: A 6T SRAM bit-cell

Inherent process variations during the manufacturing process cause these strengths to vary across SRAMs (and also within the same SRAM) leading to the data values in every SRAM being different immediately after start-up. This forms the foundation of an SRAM PUF [43,44] that follows the *power-cycling* (power off  $\rightarrow$  power on  $\rightarrow$  read SRAM) approach to generate unique start-up values as responses. The challenge, here, specifies the address of the block inside the SRAM from where the start-up value is to be read as well as its size (*i.e.*, number of bits).

A large body of work has also focused on building SRAM PUFs. Ref. [43] extracted unique fingerprints and generated true random numbers by using the power-up state (start-up value) of an SRAM chip. Another SRAM-based PUF was presented in [45], which utilized error-patterns in caches resulting from supply-voltage reduction. This approach enables run-time generation of SRAM fingerprints since it does not require *power-cycling.* Ref. [46] observed variations in read current with the stored content in an SRAM array and used them to extract unique fingerprints. Write failures are (intentionally) introduced in an SRAM array through a programmable wordline duty-cycle controller for generating unique responses in [47]. Ref. [48], on the other hand, proposes writing values into a column of SRAM cells, followed by concurrent activation of multiple wordlines. Thus, multiple cells in the column are read at the same time, forming the PUF response. In this dissertation, we utilize the *power*- *cycling*-based SRAM PUF as it remains one of the most popular and widely-adopted in several state-of-the-art systems.

#### 2.2.4 Other Memory-based PUFs

Non-volatile memories have also been explored as potential PUF implementations. Refs. [49,50] proposed mechanisms to extract device fingerprints from flash memories; the latter also proposed true random number generation using a similar approach. Ref. [51] proposed a scheme that utilizes NVM (*e.g.*, memristor, flash, *etc.*) cells to realize a PUF without using any *helper data* (for error correction).

#### 2.2.5 Reconfigurable PUFs

A parallel approach to the development of strong PUFs has focused on reconfiguration. Reconfigurable PUFs (rPUFs) [52, 53] have a mechanism to transform themselves, generating a new and unpredictable challenge-response behavior. Ref. [54] implements a *logically* reconfigurable SRAM PUF for secure key storage by hashing the start-up state of the SRAM with a stored bitstream, referred to as the logical *state*.

#### 2.2.6 Strong and Weak PUFs

PUFs have been divided into two broad categories [55] - strong PUFs and weak PUFs. Strong PUFs [7, 8, 11, 38, 46, 48] can support a very large number of CRPs and are well suited for authentication. On the other hand, Weak PUFs [43, 44] are primarily used for secret key generation as they support a relatively much smaller number of CRPs.

#### 2.2.7 Combination PUFs

Combining (the output of) multiple locations of one or several memory blocks located inside an IC to derive unique keys was mentioned in a patent [15]. By using an address decoder that can permute access order across different memory locations/blocks in a potentially unknown manner, the work claims to increase the resistance of the PUF against invasive attacks. However, no physical implementation or test results thereof have been published yet. A similar but non-memory-based PUF was presented in [16], which proposes combining several on-chip entropy sources (e.g., clock sinks) in an optimized manner towards better (overall) entropy and robustness.

#### 2.3 Authentication in Implantable Medical Devices (IMDs)

An increasing number of Implantable Medical Devices (IMDs) are equipped with wireless interfaces [18], allowing them to communicate with an external devices such as a doctor's programmer or a patient's smartphone, *etc.* While this greatly improves standard of care, it also exposes the IMD to a range of security concerns [3, 4, 19– 21] such as potential interaction with untrusted devices and potential leakage of confidential medical data. Several techniques [22–30] have been proposed to address these concerns. We discuss some of these next.

#### 2.3.1 Trusted-entity Approach and the IMD Ecosystem

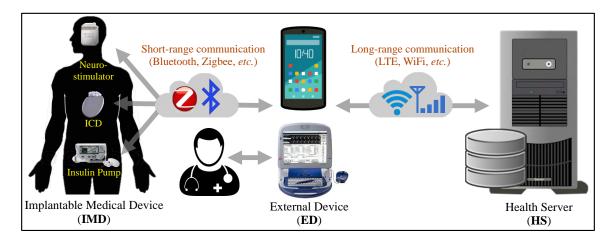

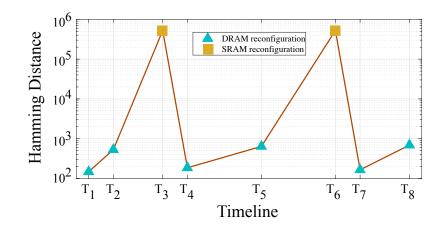

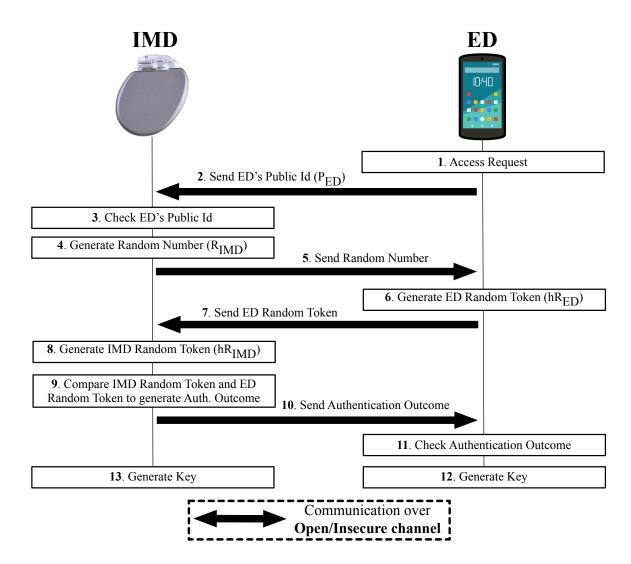

One technique of addressing the above-mentioned concerns with IMDs [28, 30] leverages a *trusted entity* such as a Health Server (HS), which assumes the role of an authenticator. Fig. 2.4 shows an IMD ecosystem based on this trusted entity and comprises of three (types of) entities: Implantable Medical Device (IMD), External Device (ED), and Health Server (HS). IMD is a small device that is embedded in a patient to monitor or treat a certain physiological condition. Typical examples of

Fig. 2.4.: An End-to-End IMD Ecosystem

IMD include Implantable Cardioverter Defibrillator (ICD), insulin pump, and neurostimulator. ED, on the other hand, is an external device that is used to program or configure IMD (after surgical implantation) as well as process the physiological data relayed by it for monitoring and therapy. Hence, ED is also known as a *programmer* in some literature and is typically a hand-held device carried by a doctor or medical practitioner. Note that such a device can also be carried by the patient for day-to-day self-monitoring. The third entity in this ecosystem is HS, which serves as the trusted entity itself. A typical example of HS is a patient database server maintained by a healthcare provider. The HS arbitrates access to an IMD when the ED requests it. Upon successful authentication of the ED, the HS distributes a shared key to both the IMD and the ED. This key is used to encrypt all further communication between the IMD and ED. Note that the trusted-entity approach is popular due to its simplified but secure usage model and requirement of no additional devices.

#### 2.3.2 Other Approaches to IMD Authentication

Over the years, several other approaches have also been proposed to enable authentication and key exchange in IMDs. Proximity-based approaches [24] authenticate an untrusted entity (e.g., ED) based on its proximity (or distance) from the authenticating entity (e.g., IMD). Biometric approaches [25, 26], on the other hand, adopt a touch-to-access policy, i.e., they use a patient's biometric or physiological values for authentication and extraction of shared keys. Another technique to authentication and key-exchange in IMDs uses a side-channel such as vibration [27]. A large body of work is proxy-based, *i.e.*, use an external (patient-carried) proxy device [26], which is trusted and mediates communication with the IMD. Lastly, the trusted-entity approach, described earlier, is used in several works [28, 30] to arbitrate access to the IMD and distribute shared keys. While each of the aforementioned approaches has its advantages and disadvantages [20, 22], we adopt the trusted-entity approach in the current work due to its better security capabilities, simplified usage model (for the patient), and the potential for seamless integration with Commercial-Off-The-Shelf (COTS) devices.

In recent years, PUFs have been used to implement several IMD-specific [29,30] as well as generic (not IMD-specific) authentication protocols [31,32]. Ref. [29] proposed utilizing two PUFs, one in an intra-body IC (IMD) and one on an FPGA (ED), both of which are *matched* to produce the same response. However, the proposed technique forces the use of an FPGA and requires a cumbersome pre-deployment *matching* process. Also, it uses asymmetric (public-key) cryptography, which is significantly more expensive than symmetric key cryptography in terms of energy consumption. Ref. [30] utilizes PUF-generated physically-obfuscated (or secret) keys stored in two IC cards, belonging to the doctor (ED) and patient (IMD) respectively, for authentication and key-exchange between the two entities. However, the protocol requires the services of HS during every authentication session, which has several disadvantages such as high overhead at the IMD and HS as well as service disruption in the event of HS' unavailability. Additionally, both the aforementioned works need special hardware, viz. an FPGA and an ASIC, and are not amenable to implementation on COTS devices. Ref. [31] presents a survey of several generic authentication and key-exchange protocols. These protocols are designed for a two-entity ecosystem, where the entities can communicate directly with and authenticate each other. On the other hand, as shown in Fig. 2.4, the IMD ecosystem in the current work comprises of three entities, two of which (IMD and HS) do not have any direct connectivity with each other. As a result, these protocols are not directly applicable to the current ecosystem. Another generic PUF-based protocol was described in Ref. [32], which performs authentication and key-exchange between a resource-constrained prover (containing a PUF) and a resource-rich verifier without requiring the PUF's (prover's) challenge-response pairs to be stored at the verifier end. Moreover, it assumes that the verifier has direct connectivity with the trusted-entity. On the contrary, the current ecosystem is based on IMD (verifier) being resource-constrained while ED (prover) being resource-rich. IMD (verifier) also does not have direct connectivity with HS (trusted-entity), and hence, the protocol described in Ref. [32] is not applicable to the current ecosystem.

# 3. AN INTRINSICALLY RECONFIGURABLE DRAM PUF FOR DEVICE AUTHENTICATION AND RANDOM NUMBER GENERATION

Over the past few years, researchers have taken an active interest in hardware-intrinsic security mechanisms, and in particular, Physically Unclonable Functions (PUFs) [6]. PUFs have proved to be a secure, low-cost, and robust authentication measure against issues of counterfeiting and information leakage. They exploit the random physical variations inherent to any manufacturing process to generate device-specific and unclonable fingerprints. These unique fingerprints can be used as the basis for a challenge-response mechanism for device authentication as well as for random number (*e.g.*, secure key) generation.

While a large variety of PUF implementations have been proposed over the years, memory-based PUFs [11, 13, 43], in particular, are an attractive candidate due to the ubiquitous presence of memory in virtually every embedded system. Moreover, memory-based PUFs require minimal or no additional circuitry for their operation, giving them a distinct advantage over other PUF implementations. One such example of a memory-based PUF, which we focus on in this chapter, is based on Dynamic Random Access Memory (DRAM). DRAM is used as the main memory in a large number of modern embedded systems (as illustrated in Fig. 3.1) due to its high density and low cost. As is well-known, DRAM cells must be refreshed periodically to preserve the stored data. This need for refresh operations also makes DRAM an attractive candidate for use as a PUF, especially for challenge-response-based authentication and random number generation.

Fig. 3.1.: Examples of embedded systems containing DRAM

#### 3.1 Chapter Contributions

Prior approaches to DRAM-based PUFs suffer from several shortcomings such as low speed of operation [11], non-applicability to commercial off-the-shelf (COTS) devices [12], and the need for power cycling the DRAM module [13,39]. Moreover, the near static nature of the response-generation mechanism in some of the works [11,13] makes them vulnerable to various security attacks [14]. To address these limitations, we propose a DRAM PUF based on refresh pausing that not only supports a very large number of challenge-response pairs (CRPs) through the variation of different parameters but is also *intrinsically reconfigurable*, *i.e.*, its challenge-response behavior can be substantially modified without the use of any additional circuitry. Hence, the PUF can be easily implemented in most off-the-shelf systems and provides considerable protection from various security attacks. Specifically, we make the following contributions [7,8]:

• We perform a comprehensive error characterization of DRAM modules by varying different parameters (refresh-pause interval, data patterns, and temperature) to gain a deep insight into DRAM behavior. This insight allows us to systematically select DRAM blocks that are best suited for use in a PUF.

- We propose an *intrinsically reconfigurable* DRAM PUF (D-PUF), based on refresh pausing, for device authentication and random number generation. Reconfiguration is achieved through variation of the refresh-pause interval, altering the challenge-response behavior of the PUF and making it robust against various attacks. We also use D-PUF to design a secure, low-overhead mechanism for performing device authentication. The mechanism operates robustly even in the presence of environmental and temporal variations.

- We implement D-PUF and our proposed authentication mechanism in a real system using off-the-shelf DRAM modules and evaluate it thoroughly. In particular, we demonstrate a 4.3X-6.4X reduction in authentication time, compared to previous work. Using controlled temperature and accelerated aging tests, we demonstrate the robustness of our authentication mechanism to temperature and aging effects. For a sample temperature range of 10°C to 60°C, we show that the mechanism achieves a 100% true-positive (successful authentication) rate and 0% false-positive rate. For a ten-month-old DRAM module, it also ensures a 100% true-positive rate and 0% false-positive rate.

- We implement a True Random Number Generator (TRNG) using D-PUF by exploiting the Variable Retention Time (VRT) phenomenon in DRAMs and demonstrate that the generated random numbers pass all the tests specified in the NIST Statistical Test Suite.

The remainder of this chapter is organized as follows. Section 3.2 describes the motivation behind this work. Next, Section 3.3 presents the D-PUF design while Section 3.4 describes the mechanisms for authentication and random number generation using D-PUF. Section 3.6 and Section 3.7 describe the experimental setup and present the results of our experiments, respectively. A discussion about implementation-related considerations is provided in Section 3.8. Finally, Section 3.9 concludes the chapter.

## 3.2 Motivation

Memory-based PUFs have a distinct advantage over other PUF implementations as they use components (SRAM, DRAM, etc.) that are inherent to most modern embedded systems. Hence, they require minimal or no additional circuitry for their operation and could enable energy-efficient designs for emerging IoT devices [56]. Over the past few years, SRAM-based PUFs have been widely studied and used as security primitives for various state-of-the-art systems [43, 44, 47, 54]. However, these PUFs suffer from several shortcomings such as limited entropy, the requirement of power cycling, high cost, etc., and are therefore limited to applications that require a very few number of CRPs or random numbers. DRAM-based PUFs, with their large address space and high density, have the potential to support a large number of CRPs (or random numbers). However, current designs suffer from several shortcomings such as the requirement of power cycling [13, 40] and large refresh-pause intervals [11, 38]. Moreover, weak (memory-based) PUFs are vulnerable to various sophisticated attacks [14]. One way of guarding against such attacks is altering the challenge-response behavior of a PUF, in other words, *reconfiguring* the PUF [52–54]. However, these designs require additional hardware resource (e.q., private NVM)to achieve reconfiguration, and hence, cannot be applied to commercially available DRAM module.

## 3.3 D-PUF: An Intrinsically-reconfigurable DRAM PUF

Towards addressing the shortcomings of memory-based PUFs described earlier, we propose an *intrinsically reconfigurable* DRAM PUF (D-PUF) based on refresh pausing. As described in Chapter 2, refresh pausing is a lightweight approach towards implementing DRAM PUFs and involves stopping the refresh operations in a DRAM module for a specified interval. In DRAMs, inter-die and intra-die variations lead to highly variable bit-cell strengths distributed randomly across different modules as well as within a module. During refresh pausing, these variations cause DRAM cells to leak charge at different rates, resulting in highly random yet unique bit-errors in the data stored in the DRAM module. We exploit this randomness (entropy) to generate CRPs (for authentication) as well as random numbers from a DRAM module. Moreover, the existence of both nature of bit-flips, *i.e.*, '1'  $\rightarrow$  '0' bit-flips (true-cells) and '0'  $\rightarrow$ '1' bit-flips (anti-cells) [57], in the same module enables us to extract more entropy out of the PUF. D-PUF is also designed to be *intrinsically reconfigurable* – the choice of refresh-pause interval as the reconfiguration parameter (described later) enables alteration of the PUF behavior without the requirement of any additional resource. Hence, it can be easily applied to commercially available DRAM modules in contrast to [12,54]. It also alleviates the problem of a large refresh-pause interval, which was required in [11,38], and also performs robust authentication across a comparatively much wider operating range (temperature and aging). The refresh pausing approach also ensures that there is no need for power cycling, unlike [13,39].

In this work, we try to realize two important functions using a DRAM PUF - (i)authentication and (ii) random number generation. As described in Chapter 2, authentication refers to any process by which a trusted entity verifies the identity of another entity trying to access the former's services. We propose a secure, low-overhead mechanism that uses D-PUF and performs device authentication without the need for additional cryptographic resources, which are used in traditional encrypted-passwordbased methods. The authentication is also assisted by a low-complexity algorithm for selecting the DRAM blocks in D-PUF that ensure the minimum required entropy at the lowest refresh-pause intervals. Random number generation involves producing a sequence of numbers that cannot be predicted better than by random chance. Random numbers find uses in various cryptographic applications such as HMAC and encryption/decryption as well as in Monte Carlo simulations, statistical research, etc. These functions require D-PUF to generate a response and random number, respectively; we briefly describe the sequence of steps involved in these processes here. A random binary bitstream of a particular size, referred to as *challenge*, is first written onto a specified memory address in D-PUF, following which, the memory controller pauses the refresh operation for a pre-decided time interval, called the *refresh-pause interval*. Next, the binary bitstream is read out from the same memory address and processed for subsequent error correction using some information (helper data) already stored at the device containing the PUF. The error-corrected bitstream is then sent out as the *response*. For generating a random number, the read-out raw bitstream (without error correction) is applied to a suitable hash algorithm (*e.g.*, SHA-256), to produce a random binary sequence. Whenever needed, reconfiguration is carried out by simply changing the refresh-pause interval associated with the generation of the response or random number.

Next, we describe device authentication and random number generation using D-PUF in detail.

#### 3.4 Device Authentication using D-PUF

The device authentication mechanism in D-PUF is divided into three phases - (i) characterization phase, (ii) enrollment phase, and (iii) authentication phase. Fig. 3.5, 3.6, and 3.7 present flow diagrams of these different phases, which are explained later in detail. The dotted lines between the device (containing the PUF) and the authenticator represent the interactions between them, while the solid lines show the actions inside each of these entities. The characterization phase ensures the usage of the minimum refresh-pause interval for authentication by carrying out a coarse-grained error characterization of the DRAM module (used as the PUF) and simultaneously guarantees that it meets the minimum required entropy. During enrollment phase, the PUF responds to random challenges sent by an authenticator, generating a CRP database that is stored at the latter. It is followed by the authentication phase, where responses are generated by the PUF for one or more challenges picked from the CRP database. These responses are then compared to the ones stored in the database; if there is an exact match or the difference is within a small threshold, the device containing the PUF is authenticated. Note that by varying different pa-

Fig. 3.2.: Authentication using D-PUF

rameters associated with the generation of a response, a very large number of CRPs can be generated for carrying out challenge-response-based authentication. Hence, D-PUF closely resembles a strong PUF. Fig. 3.2 provides a high-level overview of the entire process.

Before delving into the details of the authentication mechanism, we define a few terms and briefly discuss our assumptions. We also present the formats of the challenge and response used in our design below.

## 3.4.1 Definitions and Assumptions

- Device (D): An untrusted client device that requests authentication and contains D-PUF. It is assumed to possess sufficient computational and memory resources to perform error correction and store kilobytes of binary data. An example of such a device is a smartphone.

- Reconfigurable DRAM PUF or D-PUF (P): The DRAM module that implements PUF functionality in the device D. When we mention that a response is generated by D, it should be assumed that the same is actually generated by D-PUF (P) present inside D.

Fig. 3.3.: Challenge and Response Format and CRP database

• Authenticator (A): A trusted party which authenticates the device D. A is assumed to have access to the CRP database and limited information about the characteristics of P. It possesses greater computational and memory resources than D to process and store gigabytes of data, e.g., a server.

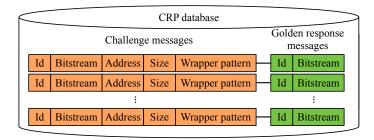

## 3.4.2 Challenge and Response Message Format

In the proposed design, challenges and responses are represented as 5-tuple and 2-tuple messages respectively, as depicted in Fig. 3.3. An entry in the CRP database comprises of a *challenge* message (CM) and a *golden response* message (GRM) (explained later in Section 3.4.4).

The response generated during authentication is referred to as a *response* message (RM). *Id* refers to the index number assigned by A to an entry in the CRP database. *Bitstream* is a random binary sequence of *size* bytes generated by A (in a CM) or D (in an RM and a GRM). Specifically, in a CM, *bitstream* is the data written onto P while in an RM and a GRM, it refers to the data read from P. Address specifies the starting memory address in P where this write or read occurs. Wrapper pattern represents a predefined binary sequence and is explained next.

**Wrapper pattern** We observed that the number, position, and nature of bit-flips in a response generated by a DRAM block in P were influenced by the peripheral data-bits surrounding the block (Section 3.7.2). These peripheral data-bits, written