Memory Access Validation Scheme

## Against

**Payload Injection Attacks**

BY

DONGKYUN AHN B.S., Yonsei University, Republic of Korea, 1998 M.S., Yonsei University, Republic of Korea, 2000

## THESIS

Submitted as partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Chicago, 2013

Chicago, Illinois

Defense Committee:

Zhichun Zhu, Chair And Advisor Ashfaq Khokhar Shantanu Dutt Wenjing Rao Venkat Venkatakrishnan, Computer Science This thesis is dedicated to my parents Kyunghong Ahn and Kyungja Kim,

without whom it would never been completed.

### ACKNOWLEDGMENTS

First and foremost, I am truly grateful to my former advisor, Dr. Gyungho Lee, for privilege of studying under his advisory. I deeply appreciate his support, dedication, patience, and unconditional support during my early period in UIC. His insightful vision on computer architecture made me a prepared computer engineer.

I would like to thank to Dr. Zhichun Zhu, for accepting me as her Ph.D student and guiding me to finish my degree. As an advisor and a professor, she gave me invaluable help during my staying in UIC.

I would also like to thank my thesis committee - Dr. Ashfaq Khokhar, Dr. Shantanu Dutt, Dr. Wenjing Rao, and Dr. V.N. Vekatakrishnan - for their resolute support and assistance. Their guidance in all areas helped me accomplish my research goals.

Lastly, I am deeply grateful to my parents. My parents made sacrifices to ensure that I get the best education and quality of living in America. Their unconditional love and support was one of the main reasons in the success of this work. I would never be able to express my gratitude to my parents in words.

DKA

# TABLE OF CONTENTS

# **CHAPTER**

## PAGE

| 1        | INTROI |                                                                    | 1  |

|----------|--------|--------------------------------------------------------------------|----|

|          | 1.1    | Motivation                                                         | 1  |

|          | 1.2    | Protection and related features                                    | 3  |

|          | 1.3    | Work focus                                                         | 4  |

|          | 1.4    | Dissertation overview                                              | 5  |

|          | 1.5    | Contribution                                                       | 7  |

| <b>2</b> | BACKG  | ROUND                                                              | 9  |

|          | 2.1    | Payload injection attack                                           | 9  |

|          | 2.1.1  | Payload injection attack overview                                  | 9  |

|          | 2.1.2  | Stack overflows                                                    | 13 |

|          | 2.1.3  | Compromising a function pointer table                              | 16 |

|          | 2.1.4  | Exploiting the format string vulnerability                         | 20 |

|          | 2.1.5  | Heap-spraying                                                      | 23 |

|          | 2.1.6  | Return-to-libc and return-oriented programming                     | 25 |

|          | 2.2    | Protection                                                         | 27 |

|          | 2.2.1  | Stack protection                                                   | 27 |

|          | 2.2.2  | Compiler-based protection                                          | 31 |

|          | 2.2.3  | Control-flow integrity                                             | 32 |

|          | 2.2.4  | Randomization in address space                                     | 32 |

|          | 2.2.5  | Non-executable protection                                          | 33 |

|          | 2.2.6  | Virtualization of Harvard architecture                             | 34 |

|          | 2.2.7  | Static analysis of foreign objects                                 | 35 |

|          | 2.2.8  | Randomization of instruction set                                   | 38 |

|          | 2.2.9  | Randomization of the system call interface                         | 39 |

|          | 2.2.10 | Information flow tracking                                          | 40 |

|          | 2.3    | Hardware-based protection and software-based protection $\ .$ .    | 41 |

|          | 2.3.1  | Required modifications                                             | 42 |

|          | 2.3.2  | Performance overhead                                               | 43 |

| 3        | PAYLOA | AD INJECTION ATTACKS                                               |    |

|          | FROM A | ARCHITECTURAL STANDPOINTS                                          | 48 |

|          | 3.1    | Shell-code injection attacks and virtual address translation       | 48 |

|          | 3.1.1  | Linear address translation in the x86 architecture $\ldots$ .      | 48 |

|          | 3.1.2  | Address translation and shell-code injection attacks $\ldots$ .    | 49 |

|          | 3.1.3  | Runtime code and address translation                               | 51 |

|          | 3.2    | Payloads as foreign objects and architectural components $\ . \ .$ | 52 |

|          |        |                                                                    |    |

# TABLE OF CONTENTS (Continued)

# **CHAPTER**

# PAGE

|   | 3.2.1   | Payload injection attacks as unexpected/unprecedented events    | 53  |

|---|---------|-----------------------------------------------------------------|-----|

|   | 3.2.2   | Cache miss handler                                              | 55  |

|   | 3.2.3   | Branch predictor                                                | 58  |

|   | 3.2.4   | Legitimate miss events                                          | 61  |

|   | 3.2.5   | Taint status data for protection                                | 63  |

|   | 3.2.5.1 | Fine granularity                                                | 64  |

|   | 3.2.5.2 | Supporting virtual memory systems                               | 66  |

|   | 3.2.5.3 | Taint propagation and block copying                             | 68  |

| 4 | TLB MO  | $\mathbf{N}$                                                    | 71  |

|   | 4.1     | Working mechanism                                               | 71  |

|   | 4.2     | Runtime codes and I/O                                           | 73  |

|   | 4.3     | Experiments                                                     | 75  |

|   | 4.3.1   | Bochs                                                           | 75  |

|   | 4.3.2   | Modifications to the TLB                                        | 76  |

|   | 4.3.3   | I/O monitoring                                                  | 76  |

|   | 4.3.4   | Áttack simulation                                               | 77  |

|   | 4.4     | Results                                                         | 78  |

|   | 4.4.1   | Modified Wilander/Riley benchmark                               | 78  |

|   | 4.4.2   | Storage overhead                                                | 80  |

|   | 4.4.3   | Performance overhead                                            | 81  |

|   | 4.5     | Discussion                                                      | 82  |

|   | 4.5.1   | Revision of paging unit                                         | 82  |

|   | 4.5.2   | Limitations                                                     | 84  |

|   | 4.5.2.1 | Coarse granularity                                              | 84  |

|   | 4.5.2.2 | Vulnerability against attacks exploiting existing machine codes | 85  |

| 5 | MEMOR   | Y-ACCESS VALIDATION                                             |     |

| 0 |         | T PAYLOAD INJECTION ATTACKS                                     |     |

|   |         | <b>FI-TASKING ENVIRONMENTS</b>                                  | 87  |

|   | 5.1     | Taint storage format                                            | 87  |

|   | 5.1.1   | Fine granularity and memory page frame                          | 88  |

|   | 5.1.2   | Matrix format for page frame numbers                            | 89  |

|   | 5.1.3   | Validation granularity and taint status information in bitmap   | 00  |

|   | 0.1.0   | format                                                          | 89  |

|   | 5.1.4   | Matrix/bitmap location                                          | 90  |

|   | 5.1.5   | Memory space requirement                                        | 92  |

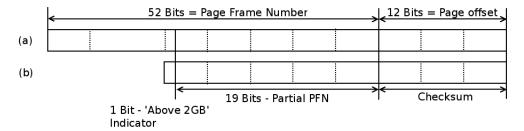

|   | 5.1.6   | Supporting 64-bit architecture processors                       | 93  |

|   | 5.2     | Memory-access validation unit                                   | 95  |

|   | 5.2.1   | Taint operation                                                 | 95  |

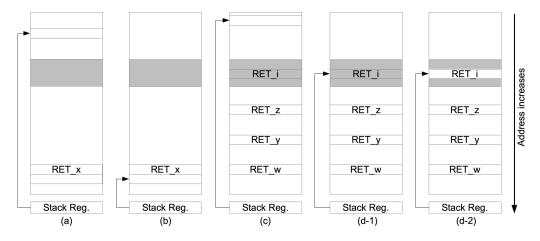

|   | 5.2.2   | Integration into memory hierarchy and the return address stack  | 96  |

|   | 5.2.3   | Block copy and taint transfer                                   | 101 |

# TABLE OF CONTENTS (Continued)

# **CHAPTER**

# PAGE

|   | 5.2.4   | Caching structure                                     | 103 |

|---|---------|-------------------------------------------------------|-----|

|   | 5.3     | System software support                               | 105 |

|   | 5.4     | False positives                                       | 106 |

|   | 5.5     | Comparison with IFT                                   | 107 |

|   | 5.5.1   | Word-size granularity and cache-line-size granularity | 107 |

|   | 5.5.2   | Augmentation of the memory system                     | 108 |

|   | 5.6     | Vulnerability and limitations                         | 109 |

|   | 5.6.1   | Vulnerability of taint information                    | 109 |

|   | 5.6.2   | Limitations                                           | 110 |

|   | 5.7     | Experiment                                            | 111 |

|   | 5.7.1   | Experimental environment                              | 111 |

|   | 5.7.2   | Effectiveness evaluation                              | 114 |

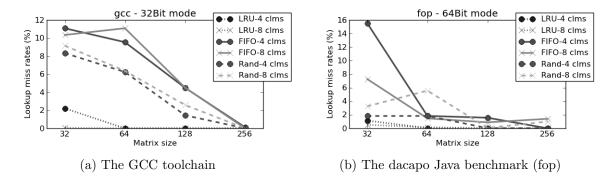

|   | 5.7.3   | Matrix structure evaluation                           | 116 |

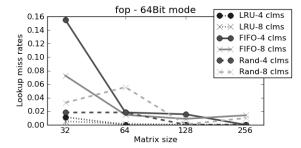

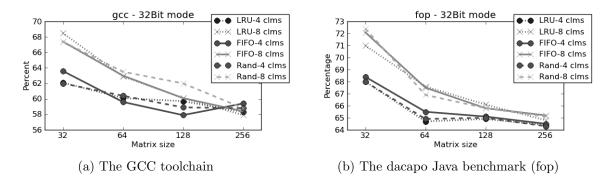

|   | 5.7.4   | Row cache and bitmap cache evaluation                 | 121 |

|   | 5.7.5   | Performance impact assessment                         | 124 |

| 6 | CONCLU  | USION                                                 | 126 |

|   | 6.1     | Summary of Thesis Work                                | 126 |

|   | 6.2     | Open issues                                           | 128 |

|   | CITED I | LITERATURE                                            | 129 |

|   | VITA    |                                                       | 135 |

# LIST OF TABLES

| TABLE |                                                | PAGE |

|-------|------------------------------------------------|------|

| Ι     | CACHE STRUCTURE                                | 55   |

| II    | VULNERABLE GUEST SYSTEMS                       | 78   |

| III   | EVALUATION OF EFFECTIVENESS AND COMPARISON     | 79   |

| IV    | VIRTUAL ADDRESS AND MATRIX/BITMAP COORDINATION | N 92 |

| V     | BASELINE ARCHITECTURE CONFIGURATION            | 112  |

| VI    | ARCHITECTURAL PARAMETERS FOR SIMULATION        | 113  |

| VII   | ARCHITECTURAL PARAMETERS FOR SIMPLESCALAR      | 115  |

| VIII  | EFFECTIVENESS EVALUATION AND COMPARISON        | 117  |

# LIST OF FIGURES

| FIGURE |                                                                     | PAGE |

|--------|---------------------------------------------------------------------|------|

| 1      | Changes in a stack frame during a stack overflow                    | 14   |

| 2      | Dynamic linking in the Linux operating system                       | 17   |

| 3      | String formatting example using the printf function                 | 20   |

| 4      | Heap spraying attack: Before and after                              | 25   |

| 5      | Changes in a stack frame protected by StackGuard                    | 29   |

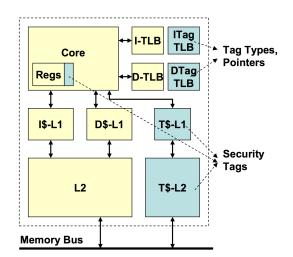

| 6      | On-chip structures to manage security tags                          | 43   |

| 7      | An example of information flow tracking for LIFT-basic $\ldots$ .   | 45   |

| 8      | Active stack region and spurious data                               | 65   |

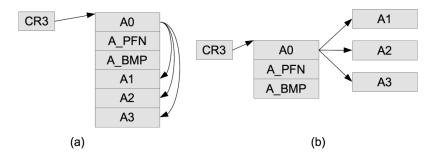

| 9      | Isolation of translation information                                | 67   |

| 10     | TLB status changing during a code injection attack                  | 72   |

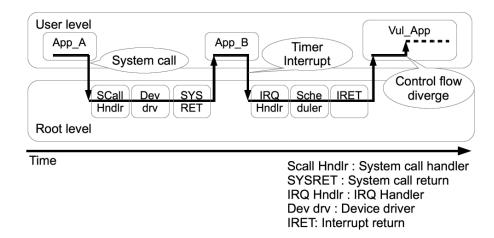

| 11     | Privilege switchings between the root and user levels $\ldots$ .    | 74   |

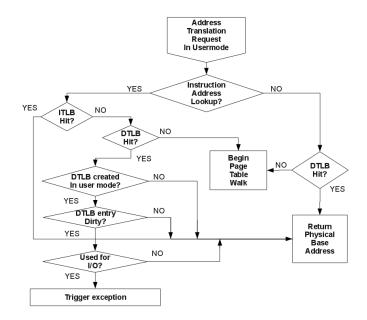

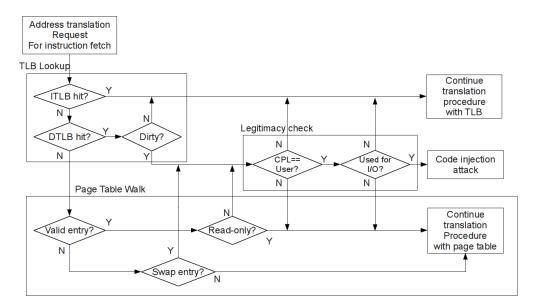

| 12     | Flow chart for TLB Mon                                              | 75   |

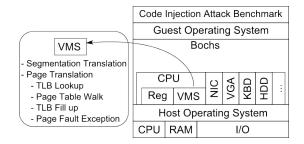

| 13     | Hierarchy of Bochs, MMU and paging unit – Virtual Memory System     | n 76 |

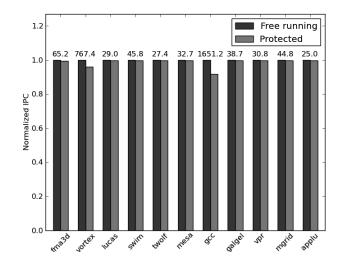

| 14     | SPEC2K benchmark results from modified SimpleScalar $\hdots$        | 81   |

| 15     | Revised version of TLB Mon                                          | 83   |

| 16     | Overview of the proposed validation scheme                          | 88   |

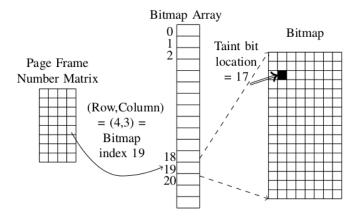

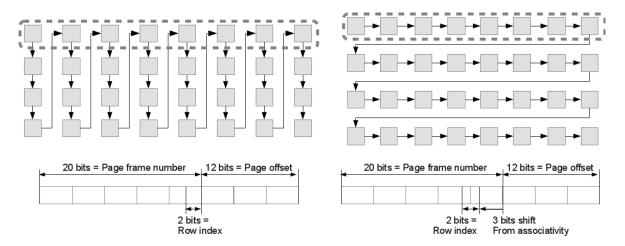

| 17     | Translation table organization augmented with taint status data set | 91   |

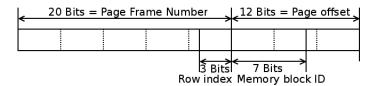

| 18     | Row index and memory block ID assignment example                    | 91   |

# LIST OF FIGURES (Continued)

# **FIGURE**

| 19 | Locating the taint status of the memory block                               | 93  |

|----|-----------------------------------------------------------------------------|-----|

| 20 | 64-bit virtual address (a) and its 32-bit PFN matrix element (b) $$ .       | 94  |

| 21 | Call chain and taint status data                                            | 99  |

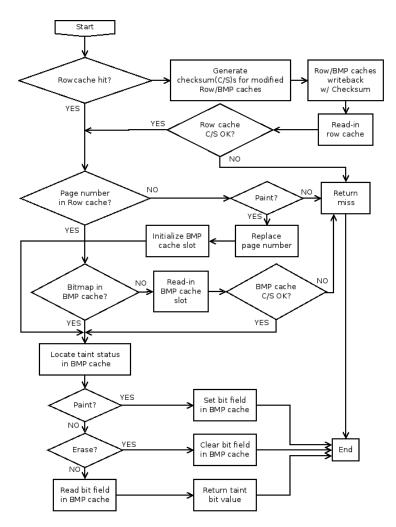

| 22 | Taint operation flow of the memory-access validation scheme $\ . \ . \ .$   | 105 |

| 23 | Payload layout and code snippets                                            | 116 |

| 24 | Row distribution for contiguous PFNs in a $4 \times 8$ PFN matrix           | 118 |

| 25 | PFN assignment distribution in each row from the GCC toolchain .            | 119 |

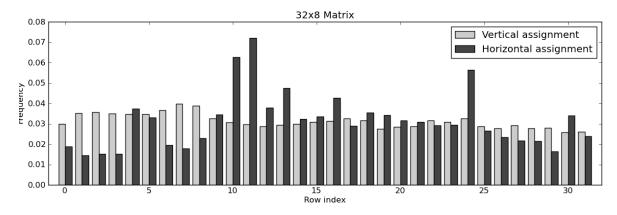

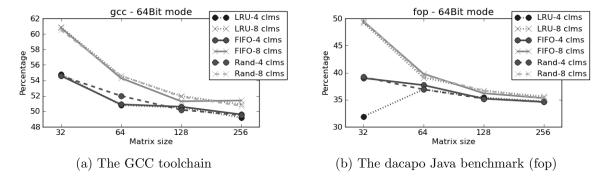

| 26 | Comparison of two row assignments for Lookup misses $\ldots \ldots \ldots$  | 119 |

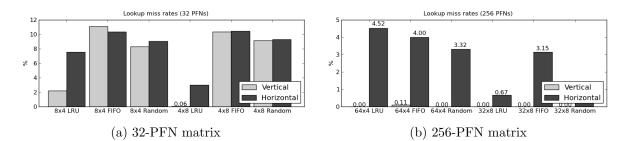

| 27 | Lookup miss rates in the 32-bit mode environment. Smaller is better.        | 120 |

| 28 | Lookup miss rates for the dacapo Java benchmark (fop) $\ \ldots \ \ldots$ . | 120 |

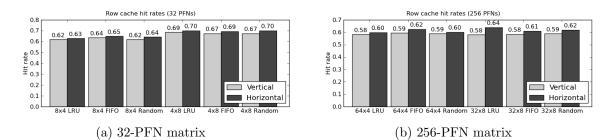

| 29 | Row cache hit rates in the 32-bit mode environment. Higher is better.       | 122 |

| 30 | Row cache hit rates in 64-bit mode environment. Higher is better            | 122 |

| 31 | Comparison of two row assignments in Row cache hit rates $\ldots$ .         | 123 |

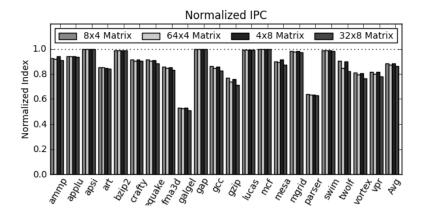

| 32 | IPC from SPEC2K benchmark                                                   | 124 |

### SUMMARY

As more individuals and organizations become more dependent on computers and the Internet to create, manage, and share their resources efficiently, computer security issues are of increasing significance in every corner of our life. Due to insecure programming environments and structural limitations at the hardware level, many vulnerabilities are still being discovered. This thesis explores various issues concerning vulnerabilities and protection measures, including attack vectors and how protection measures are designed to address security threats.

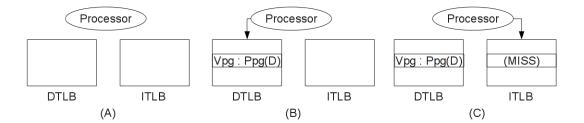

This thesis addresses threats from payload injection attacks at the architectural level by leveraging existing hardware techniques. The first work utilizes the address translation for virtual memory system. With a TLB (Translation Lookaside Buffer) that is usually split between data (DTLB) and instructions (ITLB) as found in virtual memory system of modern processors, a simple protection can be developed based on an observation that activating an injected code causes a DTLB hit under ITLB miss with dirty bit set in the hit TLB entry. To evaluate our idea, we have revised the address translation function in Bochs x86 simulator and conducted code injection attacks available over the Internet. The experimental results with two simulators show that the proposed protection can detect all the code injection attacks tested.

The second work pursues more fine-grained protection against sophisticated attacks like return-oriented-programming attacks by leveraging existing hardware techniques. Two widely adopted hardware techniques – the cache structure and the branch predictor – increase performance in modern microprocessors by exploiting expected or predicted circumstances and

### SUMMARY (Continued)

events. As malicious payloads are prone to induce unprecedented or unexpected circumstances at control flow redirection, validating those circumstances or events at the associated handlers could be utilized in countering payload injection attacks.

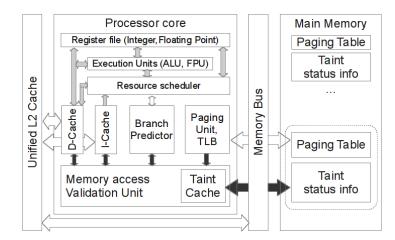

In order to utilize these components for protection, this thesis clarifies practical issues in distinguishing legitimate miss events from those caused by malicious attacks and integrating supporting mechanisms into multi-tasking environments. Based on the observation and discussion, we propose a memory-access validation scheme against payload injection attacks. This scheme consists of two parts – the validation unit and taint-status data. The validation unit handles queries from other processor components, namely the cache structure and the branch predictor, and validates suspicious control flow redirections by referring to the active taint-status data set. Experimental results with two simulators show that the proposed validation scheme is able to detect simulated payload injection attacks under negligible to moderate performance degradation.

### CHAPTER 1

### INTRODUCTION

#### 1.1 Motivation

Since their debut, computers and the Internet have become an indispensable part of the infrastructure of modern society. Most organizations including government agencies, corporations and educational institutions depend on computers and the Internet more and more in order to create, manage, and share their resources effectively. Computer security is crucial in modern society because any compromise of integrity or reliability can result in a devastating outcome, and the damage can be extremely costly – especially in a networked environment. For example, the infamous *Conficker* worm, which targets the Microsoft Windows operating system, disables several security-related services in infected systems and creates congestion on a local network by flooding packets. This worm also utilizes the networking infrastructure for its own benefit – to propagate itself to other machines online or to upgrade itself. Due to its advanced circumvention technique, this worm is unusually difficult to detect and to eradicate, and the estimated economic cost from this worm was about \$ 9.1 million in 2009 (1).

Security vulnerabilities in software allow adversaries to compromise and to take control of target systems for malicious activities like stealing classified information stored in an electronic format or coordinating distributed denial of service attacks with multiple infected systems to bring down another target system. Although most attack vectors rely on specific properties of the target systems and often are not transferable from one target platform to another, attackers are able to infect a large number of vulnerable systems because these systems frequently share software platforms such as operating systems or libraries, or each of them provides the same address space for common resources.

Some attacks try to execute their own software module on the target remotely. In an uncompromised operating system environment, only binary executables installed by the operating system or the administrator are allowed to be loaded and executed with binary loaders. However, through software vulnerabilities like buffer overflows, malicious parties are able to inject and execute their own code without the operating system's authorization. This problem becomes even more threatening if the adversaries are able to acquire the supervisor privilege of the operating system through brute-force or dictionary-based attacks. As the supervisor privilege gives unlimited access to a system's resources, an adversary with this privilege can stealthily install or inject their code and make the processor execute it without being detected by anti-malware software.

According to the National Vulnerability Database, vulnerabilities related to code injection attacks accounted for 16 percent of the total vulnerability reports in 2009. Although those vulnerabilities can be eliminated or mitigated with various detection approaches and/or patches at the software level, the overall number of vulnerabilities reported is increasing. This is because a large number of source codes are still written in weakly typed languages like C/C++, and binary executables generated from those languages are deployed every day.

#### **1.2** Protection and related features

Protection against code injection attacks can be categorized as two types – static analysis during compile time or runtime checks and prevention. Although proposed detection and protection based on these approaches are helpful in thwarting some code injection attacks, they cannot provide an ultimate solution for several reasons: (1) use of unsafe low-level programming languages for software components that require high-performance; (2) limitations in static and dynamic analysis; and (3) inherent assumptions made about modern computer systems.

In order to eliminate software vulnerabilities in programming, many high-level programming languages, like Java and C#, have adopted various safety features, which have eliminated numerous security problems. However, there are still many software packages written in unsafe low-level languages such as C/C++ or assembly languages, for several reasons: (1) compiler or library dependency on legacy software modules and libraries; (2) the high performance required for system-critical software modules such as an operating system kernel or device driver modules. Generally, writing safe and secure programs using such low-level languages is difficult and programmers are prone to introducing bugs and vulnerabilities, which are very difficult to detect during compile time due to the lack of runtime information.

For these unsafe language programming environments, static analysis and dynamic runtime checks are proposed, some of which are applied in commodity products. A modern static analyzer can find programming errors or vulnerabilities before generating a binary executable. However, their detection performance is limited due to the lack of runtime information such as target addresses for indirect branches, and they are prone to finding false positives, making them hard to use in practice. Dynamic runtime checks can partially complement the limitations of the static analysis approach – however, sophisticated algorithms to detect anomalies usually incur significant performance overheads. In addition, both approaches require prerequisite work, mainly for dealing with source codes.

Each item of software in a computer system is composed and executed based on certain assumptions established with regard to the target platform's design and implementation. For example, the x86 architecture supports four levels of privilege in its operation mode – zero to three – where the lower number has more privileges. However, most operating systems utilize only two of them – zero, which is the most privileged, and three, and it is assumed that processes running with the privilege level zero are reliable and uncompromised. Unfortunately, adversaries are able to stealthily acquire the privileged running level by exploiting these assumptions, and malicious activities performed with the hijacked privilege are permitted as if they were legitimate operations.

#### 1.3 Work focus

Based on the protection against payload injection attacks and related features, we define our research scope for these attacks and the protection against them as follows:

<u>What we do NOT propose</u>: This thesis does not propose any protection feature that prevents payload injection attacks exploiting vulnerabilities or lexical or semantic errors in high-level runtime environments such as JavaScript engines or SQL engines. Also, we do not aim to counter malicious activities that try to sneak out information through physical media such as covert channels or by wiretapping the system bus. We do not consider malicious attacks that compromise the integrity of existing software modules such as the CMOS BIOS. Finally, we are not interested in countering socially organized attacks such as distributed denial-of-service (DDoS) attacks on the target machine.

<u>What we do propose</u>: This thesis proposes a protection scheme against payload injection attacks at the processor architecture level. In this regard, a payload is a foreign object that could be executed as a viable machine code after being implanted during runtime or that is able to redirect the control flow of a process that shares the same address space as the payload itself in an unexpected way.

We are interested in leveraging existing processor components and integrating a protection scheme into multi-tasking environments. For this research, we scrutinized the general memory architecture and hardware optimization in terms of handling unexpected circumstances and foreign objects. We also investigated the resource management of multi-tasking environments so as to support existing platforms – from the architecture level to the user application level. Based on this thorough investigation, we tried to propose a protection scheme that requires neither fundamental changes in the existing processor architecture nor considerable modifications to the software level – either at the OS kernel or the application level.

#### 1.4 Dissertation overview

In order to propose a protection measure to counter payload injection attacks at the architectural level, this thesis discusses various issues regarding payload injection attacks – from vulnerabilities to countermeasures. We analyze payload injection attacks from architectural standpoints and clarify practical issues in leveraging architectural components and inherent events so as to address limitations found in software-based protections. Based on the discussion and analysis, this work develops a protection scheme against payload injection attacks at the memory architecture level and evaluates reliability, effectiveness, and performance impact of the proposed scheme.

In Chapter 2, we explore various aspects of payload injection attacks – security vulnerabilities, various attack vectors exploiting those vulnerabilities, and countermeasures against them. We discuss various aspects of these issues – the architectural standpoint, programming environments, runtime environments, etc.

Chapter 3 analyzes payload injection attacks from the architectural standpoint – especially in terms of hardware-based acceleration techniques like cache structures and discusses practical issues and requirements in exploiting these techniques for protection.

Chapter 4 proposes a protection approach against shell code injection attacks. The proposed approach exploits a TLB structure and I/O operations to detect instruction fetch attempts toward arbitrarily modified memory pages. We evaluate effectiveness and performance impact with simulators.

In Chapter 5, we propose our memory-access validation scheme based on the discussions presented in Chapter 3. For this scheme, we develop a data structure to store taint-status data and design a validation unit that answers queries from other hardware components by referring to taint-status data contained in main memory. We also propose integration approaches and a caching structure so as to alleviate the performance overhead. The experimental results show that our validation scheme is able to counter simulated payload injection attacks with a modest performance impact.

Chapter 6 concludes this thesis. We summarize this work and discuss open issues related to the proposed scheme.

### 1.5 Contribution

This thesis makes the following key contributions in preventing payload injection attacks in multi-tasking environments at the processor architectural level:

- 1. Investigation of payload-injection attacks. This thesis explores various issues for payload-injection attacks vulnerabilities, attack vectors, and countermeasures. We discuss these issues for simple types of payload-injection attack to advanced types targeting runtime environments like web browsers. This investigation analyzes payload-injection attacks not only in the software domain but also the architectural circumstances that allow malicious attacks.

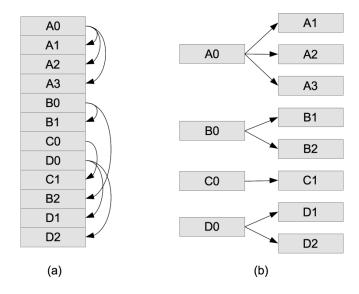

- 2. Analysis of payload-injection attacks from an architectural standpoint. This thesis analyzes payload-injection attacks from an architectural standpoint. We find that the miss handlers of the instruction cache and the return-address stack (RAS) could be utilized to counter payload-injection attacks. A protection scheme exploiting these handlers has advantages in countering payload-injection attacks because of its transparency to the software level.

- 3. Hardware-friendly data structure. This work proposes a data structure for auxiliary data that contains information on unreliable foreign objects. This data structure can be

seamlessly integrated into existing multi-tasking environments and memory architectures and guarantees constant access time to its instances.

- 4. Architectural integration approaches for memory-access validation. In order to create a memory-access validation scheme against payload-injection attacks, we developed architectural integration approaches that exploit inherent events of the processor such as cache misses. We also propose a caching structure to mitigate performance degradation from accessing instances of the proposed data structure.

- 5. Experimental validation. In order to evaluate the effectiveness and performance impact of the proposed scheme, we built simulation environments based on two simulators. We ran extensive tests on both simulators a shell code injection benchmark, the GCC compilation, and the SPEC2K benchmark.

### CHAPTER 2

### BACKGROUND

#### 2.1 Payload injection attack

#### 2.1.1 Payload injection attack overview

A payload injection attack is an attack strategy that exploits a vulnerability in a computer system to execute an arbitrary code maliciously crafted by an adversary.

In the modern computing environment, an application consists of procedures and data referred to and modified by the procedures. Each procedure is programmed to accomplish its tasks through various arithmetic operations, data movement, and other procedures. Some of the procedures in an application are loaded into the same address space when the application is prepared for execution, and others are linked to external binary(ies), called a "library," and are invoked on the fly. Regardless of whether a procedure is provided internally or externally, every procedure exchanges data with other procedures or hardware devices to accomplish what it is designed to do. During an exchange, arguments and return values are passed between procedures, and some of the exchanged values require a storage space larger than the size of a memory word – for example, 4 bytes. In order to handle this multiple-word memory requirement, a portion of consecutive memory space is allocated in the form of array and utilized for data processing/exchanging. Such memory spaces are referred to as a "buffer." While procedures in an application process data and return the result to other procedures, buffer spaces can contain various types of data – such as integers, characters, floating-point numbers, and even machine code. Meanwhile, the control flow in each procedure is dynamically changed depending on various factors, like the outcomes of conditional branches or function pointer values. In buffer use and control flow, the processor hardware blindly executes instructions pointed to by the program counter under the following assumptions: (1) the instructions are organized in a way such that the buffer spaces are accessed only for their original purpose; and (2) the control flow is always bounded within a specified address range.

However, these two assumptions can be easily violated due to software bugs caused by human error or hardware limitations – especially if a software program was composed using a weakly typed programming language like C/C++. One example is when a buffer space allocated for strings contains a machine code because of (1) a programmer's naive assumption that only alphanumeric characters or unexecutable binary sequences will be entered as input; and (2) the lack of a type-restriction enforcement on memory at the hardware level. These circumstances allow intruders to place a binary sequence of arbitrary values into a buffer space unsupervised by the operating system or runtime environment.

An example of a control flow compromise is a corruption of the control flow data – especially for indirect branches referring to a register or a memory word. Unlike a direct branch instruction, which has only two target addresses – taken or not taken determined by the result of an arithmetic comparison, an indirect branch can redirect control flow to an arbitrary location with the target address saved in a register or main memory. As the target address is determined at runtime, indirect branches provide flexibility so that programmers can redirect the control flow to different locations with one instruction. As indirect branches can divert the control flow to an arbitrary location at the machine code level, software developers try to carefully manage such memory words for these instructions while programming, and compilers may show errors or warning messages for their improper use during compile time. However, such indirect branch information can become corrupted at runtime through other programming errors such as an *out-of-bound* pointer arithmetic operation, and the control flow may be redirected to an unexpected location. For example, if an initialization procedure mistakenly overwrites a function pointer with zero, an illegal reference exception is triggered at its de-reference, as a zero value in pointer arithmetic means NULL.

In summary, payload injection attacks are accomplished through sequential intended violations in the execution of arbitrary machine codes as follows, and Steps 2 and 4 are related to the violations explained above.

- 1. An adversary crafts a malicious payload to be placed in a writable region of a victim program and figures out a vulnerability of the program, which allows the adversary to overwrite the control flow data with an arbitrary value.

- 2. Through a legitimate input operation such as a string input, the adversary places the payload in a writable memory region of the victim program.

- 3. During or after payload placement, the adversary tries to compromise vulnerable control flow data such as a return address in a stack.

4. When the corrupted control flow data is de-referenced for an indirect branch, control flow is diverted to the location chosen by the adversary.

While problematic programming practices can result in violating the assumptions and these violations provide opportunities for malicious intrusions, other features of memory systems in modern computing systems allow payload injection attacks as well.

Shared address space: In most modern computer systems, code and data referenced by the code share the same virtual address space. This property allows a payload injected as data by an adversary to be later accessed as an instruction fetch without any hardware intervention between the accesses. However, this access sequence is also followed by legitimate software loading/execution procedures in processors based on the von Neumann architecture. In order to secure the integrity of software programs running on a computer system and to prevent execution of arbitrary codes, modern operating systems are designed to execute only legitimately loaded codes and to protect these by managing various properties like the "readonly" attribute in virtual memory systems.

Flat memory model: The flat memory model refers to a memory-addressing paradigm in which the processor can linearly address all of the available memory locations without having to resort to any sort of memory segmentation. Although some architectures include a non-flat memory organization like the segmentation unit in the x86 processor, many operating systems use this non-flat memory model in a limited way – as a flat memory model. This is because other memory management mechanisms, like memory paging, can replace it effectively while simplifying the overall management. In addition, because of its hardware dependency, such a non-flat model is not considered to be a viable management scheme especially since portability is important in modern operating systems.

The following section describes attack vectors used in payload injection attacks, and the countermeasures used to guard against them.

#### 2.1.2 Stack overflows

The simplest form of a payload injection attack is to craft a malicious payload exploiting the buffer overflow vulnerability and to place the payload in a buffer allocated in the stack region.

The stack region consists of a set of stack frames, each of which is allocated for one function call at runtime. In most microprocessors, one or two registers are associated with a stack frame in use; in the x86 architecture, ESP (i.e. the stack pointer register) points to the top of the stack, and EBP points to the bottom of the current stack frame. Whenever a subroutine is called with a call instruction, the processor hardware decreases the stack pointer register and stores a return address in the memory word pointed to by the register. Then the stack frame information for the caller routine is stored in the stack, and registers related to the stack are decreased to make a new stack frame whose size is determined by the invoked subroutine. Instructions in the subroutine refer to these registers as a base for register-indirect addressing. Upon finishing the subroutine, control flow goes back to the next instruction of the call instruction by reading the return address from the stack, and the stack frame information for the caller routine is restored to related registers.

The buffer overflow vulnerability is a software bug in which an input stream whose size is larger than that of the allocated buffer space corrupts memory words next to the buffer.

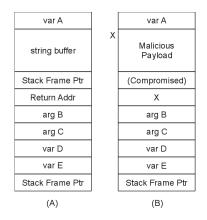

Figure 1: Changes in a stack frame during a stack overflow

(A) A vulnerable stack layout in which the return address (Return Addr) is located close to a string buffer. (B) The stack layout after a stack overflow. The string buffer is filled with a malicious payload and the return address is overwritten with the starting address of the string buffer – "X."

When programmers use a weakly typed language like C/C++ to write procedures utilizing buffers, they occasionally miss the boundary check for a data move operation. For example, the **strcpy** function copies a character string from one location to another until the "end-of-string" character, which is usually the NULL character, is encountered in the source string and it does not consider the size of the destination buffer. Therefore, if a programmer uses this function without a boundary check to copy a string from one place to another, the memory region following the destination buffer can be compromised, because this function does not consider the size of the destination. In summary, as described previously, the processor executes instructions blindly so that *out-of-size* data movement can corrupt memory words next to the buffer.

The stack region is the most frequent victim of attacks exploiting this vulnerability because without a boundary check, data written into the stack can overwrite the return address. By supplying an excessive amount of input data to an application subject to this vulnerability, an adversary can compromise a memory word containing a return address so that, when the corrupted return address is de-referenced, the control flow is redirected to another location never anticipated by the programmer. Generally speaking, there are two types of payload injection attack that exploit stack buffers – the first type puts the machine code to be executed into the payload and the other type crafts the payload with machine code addresses and parameters. The latter attack vector was devised to circumvent countermeasures against the first type. This section discusses only the first type and the latter type is discussed in Section 2.1.6 in detail.

A maliciously intended payload for simple stack overflow attacks consists of (1) a machine code that organizes arguments in the stack or registers and invokes existing procedures in the victimized system and (2) a memory word containing the starting address of the code. The distance between the starting address of the machine code and the memory word for the return address can be calculated from the source code or by exploiting other vulnerabilities like the format string, which is explained in Section 2.1.4. By placing this payload in the stack of the vulnerable application, adversaries can execute their own code without the loading process being handled by the operating system. As this attack vector directly corrupts a memory word referenced for control flow, it is often referred to as a "single-stage" buffer overflow attack as illustrated in Figure 1.

While the single-stage buffer overflow attack overwrites a return address in the stack region by overflowing directly, the multi-stage attack compromises the return address indirectly through a pointer variable located close to an input buffer in the stack region. The attack code is crafted to corrupt only a memory word used as a pointer variable next to the buffer while not touching other memory words between the pointer and the return address. By overwriting the pointer variable with the location of control flow data, the attacker can redirect the control flow to injected code when the corrupted memory word is de-referenced. In other words, the pointer is exploited as a "bridge" to compromise a target word through a buffer overflow. This attack vector is designed to circumvent countermeasures against the early form of buffer overflow attacks, which are based on a single-stage buffer overflow.

This attack form has been widely adopted in various in-the-wild attacks – such as L10n Worms, Slapper Worms, Sasser Worms (2), and Code Red (3), and Conficker (1). Although many forms of protection have been proposed, many applications are still exposed to the vulnerability exploited by this attack vector because of their programming environments – like weakly-typed language like C/C++ or assembly languages.

### 2.1.3 Compromising a function pointer table

Not only the stack region, but also other data regions can contain control flow data, and they can be exploited to execute an injected code as well. An example of such a region is one containing a function pointer table used to invoke procedures provided from libraries. Most operating systems provide various services to user-space applications – from simple ones like the current date/time to complicated ones like controlling network communication. Procedures for these services are stored in shared libraries so they can be reused, for memory space efficiency, and for the centralized management of shared resources. In order to support this feature dynamically, operating systems load and link these libraries upon receiving an invocation at

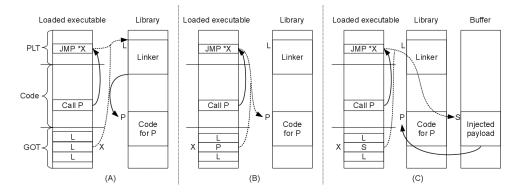

Figure 2: Dynamic linking in the Linux operating system

(A) Initial status of the memory layout when a binary executable is loaded. When control flow goes through the linker, the GOT for procedure P is updated with the runtime-decided location of its actual location – P. Therefore, the next time the same procedure is invoked, control flow goes to the procedure without going through the linker procedure, (B).

runtime, and this process is referred to as "dynamic-linking." This linking process requires a function pointer table mapping its elements to the actual addresses of the corresponding procedures. In the case of the Linux operating system, this table is called the "Global Offset Table," or the GOT. In addition to the GOT there is another table called the "Procedure Linkage Table," or the PLT, which contains a set of indirect function-call instructions referring to the GOT. While the PLT is stored in a code section that is read-only, the GOT is stored in a writable data section. A similar linking feature using indirect branches is employed in the Windows operating system family, and the corresponding table is referred to as the "Import Address Table" (IAT).

During the initial loading of a binary executable, the GOT is filled with the entry address of the dynamic linker, which is responsible for updating function pointers in the GOT - (A)

in Figure 2. When an element of the GOT is referenced by the loaded executable to invoke a procedure in a library, the dynamic linker is executed and it overwrites the element with the actual address of the requested procedure. When a previously requested procedure is invoked again, the procedure in the loaded library is executed without going through the dynamic linker – (B) in Figure 2. Although the locations of loaded libraries (P in Figure 2) are determined at runtime, a userland application can invoke functions with an indirect branch instruction that refers to the function pointer value in the GOT. It is obvious that this table should not be modified by any software modules other than the dynamic linker. However, with a sophisticated attack code, an attacker can locate the table and modify its pointer element to redirect the control flow to an injected code whenever the compromised element is de-referenced. This attack vector is adopted by code injection attacks targeting the IAT in the Windows operating system as well (4).

Not only the function pointer table for dynamic linking but also other tables containing control flow data can be exploited – for example, a virtual function table, also known as a **vtable**. This type of table is extensively utilized in object-oriented programming environments such as C++. In such an environment, various types of classes can be declared under an inheritance hierarchy. In a hierarchy, a derived class inherits methods from the base class. Some of these methods are "virtual," which means the actual procedure called for the method is determined at runtime, since it depends on the class of the method invoked. In the implementation, a function pointer table containing addresses of related procedures is associated with the instances of each class. Every object instance locates a function pointer in this table with a designated pointer (the virtual table pointer) and the proper offset contained for each instance. Through this table-pointer-instance coordination, the same method indicated by the same pointer field can be linked to different procedures at runtime.

There are two vulnerable points in this coordination – one is the virtual table pointer, and the other is the virtual function table itself. An adversary can make a fake virtual function table and compromise a virtual table pointer to point to the table so that the control flow goes to an injected code. Corruption of the virtual function table is similar to an attack compromising a function pointer table used for dynamic linking.

In general, every function pointer that can be overwritten through any kind of vulnerability can be exploited by a payload injection attack. For example, if a buffer-overflow attack corrupts a function pointer next to a buffer, the control flow is redirected to another location when it is de-referenced. Moreover, even if the target location of an indirect jump cannot be restored precisely due to randomization in the address space, an adversary can abuse a vulnerable function pointer by overwriting it with a random value so as to execute the injected code. An adversary can craft and execute an attack script that repeats payload injections containing a random value to be referenced as function pointer variable until the random value hits the starting address of the injected payload. An example of this type of attack vector is described in Section 2.1.5.

To complete an attack based on this vulnerability, an attacker may employ a second attack vector to locate and overwrite the table. One example of such coordination is the use of the format string vulnerability described in the next section. Figure 3: String formatting example using the printf function

#### 2.1.4 Exploiting the format string vulnerability

While the stack-based buffer overflow relies on the stack layout of the victim application to execute the injected code, format string exploitation utilizes a bug in the programming syntax. In the C programming language, a special directive "%" is used to format a string in string output functions, such as **printf** and **sprintf**. However, this directive can be exploited to disclose the stack layout and its elements to an output terminal like telnet, and an adversary can craft a payload that redirects the control flow to an arbitrary location where a shell code is stored with the internal information on stack usage.

Figure 3 is an example of a string output function. The first argument is a string referenced for formatting with "%" directives, and the remaining arguments are the variables associated with each ("%"-character) pair in sequence. These arguments are stored in the stack prior to invocation so that the **printf** function can refer to them. The character following the directive indicates how the data is to be displayed. For example, "%s" is a format command meaning that the string pointed to by the corresponding pointer in the stack (in this example, **pString**) is to be printed out until a NULL character is encountered. Unlike the "%s" format directive, other "%" codes are instructions to read the memory word(s) directly from the stack and to print out its value in the format indicated by the character following the "%" directive. The following list shows some examples of these formatting codes (Figure 3):

- %d decimal number

- %f floating point number

- %x hexadecimal number in lower case

- p virtual address format, equivalent to "0x%x"

While the **printf** function is parsing the format string passed as the first argument, the function fetches one value from the stack and prints out the value according to the corresponding format directive whenever a "%" directive is encountered. This operation is based on the assumption that the stack frame in use contains all of the arguments for the format string – but does not count the number of arguments provided in the source code. In other words, even if some arguments after the format string are omitted, the source code can still be compiled<sup>1</sup> and executed. This means that if the number of directives and arguments programmed in the source code do not match, the output would not be as the programmer expected – moreover, an adversary can exploit this.

Assume that a programmer writes an output function such as the following:

$<sup>^1\</sup>mathrm{Recent}$  compilers may show warning messages

#### printf(buffer); /\* buggy \*/

At first glance, it seems that this line would work without any problem – just print out the string pointed to by the **buffer** argument. However, if the string contains more than one "%" directive, this output code would reveal the data stored in an arbitrary location as well as those in the stack region because, as described above, it is assumed that all of the arguments for formatting directives are properly contained in the stack frame in use. An *out-of-bound* reading like this will certainly result in information leakage.

Exploiting this information leakage is limited and another attack vector is required to redirect the control flow to where an adversary wants. To make things worse, the same printf function has a special directive that can write an arbitrary value into any location – "%n." This directive assumes that the corresponding argument is an integer pointer and writes the number of bytes formatted so far into the memory word associated with the pointer. One may ask how an arbitrary number can be written through this directive if the number is determined by the format string. This problem can be overcome with another directive – "%au," which controls the number of bytes formatted so far. With a well-crafted format string, an adversary can gain the write privilege to any writable memory region and redirect control flow to wherever he/she wants.

The infamous wu-ftpd attack is one example, which exploited this vulnerability. Instead of typing in a legitimate input argument for the vulnerable command (SITE EXEC), the attacker used a string like the following line to find out values contained in the stack:

> SITE EXEC %x %x %x %x

When this input string is parsed, four values including the address of the ftpd process, are printed out to the shell terminal. With these values, the attacker can inject their own payload into the victim's address space and execute it by corrupting control flow data – such as a return address.

Another example of this vulnerability is demonstrated by an application programmed in the Perl language. In (5), the author mentions that with a carefully crafted input string with special directives, an adversary can make the victim computer consume a large amount of memory, modify variables arbitrarily, or alter intended outputs. It is also stated that fixing the interpreter problem will not completely eliminate the impact of the format string vulnerability but only reduce it.

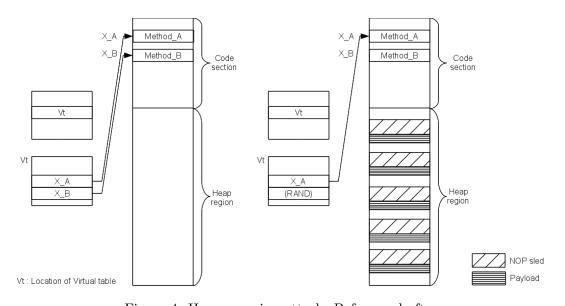

### 2.1.5 Heap-spraying

Since there are many forms of protection to prevent attacks that victimize the stack region, intruders have shifted their target to the heap region, in which objects are allocated and deallocated at runtime. Injecting and executing a machine code in the heap is more difficult than exploiting the stack. This is because the addresses of objects in the heap are less inferable and predictable than those in the stack region, and the randomization of the address space reduces the likelihood of exploitation from attacks targeting the heap. In order to overcome these limitations, attackers have developed several attack methods, one of which is heap spraying (6). Heap spraying was used occasionally in early 2000. However, it has become widespread in attacking web browsers and executing arbitrary code since 2005 – especially victimizing Internet Explorer from Microsoft. Unlike other code injection attacks, which place a malicious payload in a writable region and execute the payload by precisely locating it, the heap spraying attack spreads an object containing a malicious payload in the heap through a legitimate procedure invocation. After populating the heap region with clones of the object, the intruder corrupts a function pointer in the victim application with an arbitrary address. The attack vector which compromises a virtual function pointer is described in Section 2.1.3. If this arbitrary address happens to fall in the address ranges assigned to sprayed objects, the payload in the object is executed when the corrupted function pointer is de-referenced for control flow redirection.

It is quite obvious that the success of heap spraying relies on the probability of an address hit. In order to increase this probability, an adversary fills the object with ineffective instructions such as NOP and ends it with the malicious payload. Technically, any instruction can be included as an ineffective portion of this object as long as it does not affect the operation of the payload. A structure such as this is referred to as a NOP sled as the control flow slides into the payload when the program counter hits one of the NOPs. In addition to this structure, the attacker makes the overall spread size very large to increase the probability of a hit. For example, if the spread size is 256 MB, then there is only a 4-bit entropy in a 32-bit architecture (=  $32 - log_2(256 \times 2^{20})$ ) for attackers to predict the location of the cloned objects (7).

Heap spraying needs a victim application that allows an attacker to populate the heap region with arbitrary data without much effort. Of the many programming environments, scripting languages meet these criteria – they provide the programming interface in which users can assign objects dynamically in the heap region using a simple syntax. In particular, JavaScript

Figure 4: Heap spraying attack: Before and after if the (RAND) value hits one of the NOP sleds (45 degree hatched regions), control flow passes to the payload (horizontally hatched regions).

can simplify the steps for generating a malicious object containing a payload and spraying it. It is widely known that the JavaScript engine is employed in many GUI-based web browsers, therefore they may be exposed to this attack vector. Moreover, it has been found that not only web browsers but also other commodity software with the same parsing engine can be vulnerable to heap spraying. One noticeable "high"-risk example is the vulnerability found in the Adobe PDF viewer with the JavaScript engine enabled (8).

### 2.1.6 Return-to-libc and return-oriented programming

A return-to-libc attack is a variation of the stack overflow attack, which executes a preexisting procedure in a library without injecting a machine code into a writable region. It is designed to circumvent protection based on the non-executable property (Section 2.2.5). As explained in Section 2.1.2, a stack region is used to allocate local variables and to pass arguments to subroutines. In normal calling conventions for subprocedures, arguments are saved in the current stack frame and the target subprocedure is invoked through a call instruction. A subroutine assumes that arguments are already contained in the stack frame and they can be referenced through register-indirect addressing. Based on this convention, it is possible to exploit any pre-existing procedure without injecting a payload to be executed if the adversary is able to: (1) identify the location of the procedure(s) to be exploited; and (2) put arguments for the procedure in a stack frame of the victimized process. Basically, a payload crafted for a return-to-libc attack contains the entry point of the exploited procedure like system() and arguments for the procedure, such as "/bin/sh," and this payload is injected into the victimized stack frame via a buffer overflow. When this corrupted value is referenced for the return instruction, the control flow is diverted to the target procedure, which is usually located in a C library. Since a subroutine usually does not care how the control flow reached it, compromising a return address is good enough to execute a pre-existing procedure.

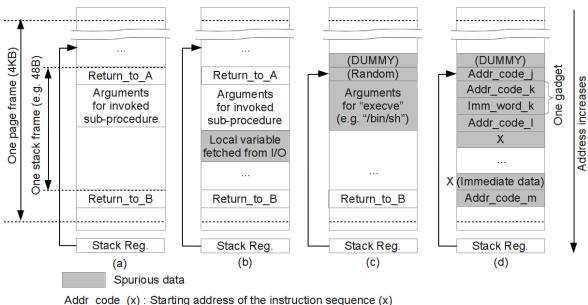

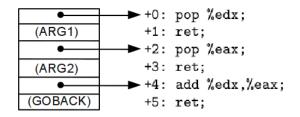

Not only at the procedure level, but also at the machine code level, existing instructions can be exploited to form a valid attack. "Return-oriented programming" (ROP) exploits control of stack frames to execute carefully selected machine codes located prior to **return** instructions (9). While **return-to-libc** attacks could be prevented with randomization-based protection like ASLR (Section 2.2.4) and rely on the content of the exploited library, return-oriented programming fundamentally addresses both limitations by collecting existing machine codes in the address space of the victimized process before an attack and executing them. In general, a payload for an ROP attack is organized with *gadgets*. Each gadget consists of pointers to instruction sequences ending with **return** and immediate data words referenced by the instructions pointed to. A gadget is crafted for a basic operation like load, store, or addition. These pointers are referenced by **returns** and immediate data words are accessed by the instructions pointed to like **pop**. By putting a collection of gadgets into a payload, an adversary is able to synthesize a viable attack vector out of raw instructions stored in the address space shared by the injected payload. As mentioned in (10), the easiest way to place gadgets into the address space of the victimized process is to overflow stack – i.e. stack overflow. When a function tries to fetch a return address from the compromised stack, the ROP attack is executed.

# 2.2 Protection

Computer security engineers have proposed numerous protection measures against various types of payload injection attacks, and some of them are widely employed in commodity software. This section discusses several protection approaches including some theoretical models.

# 2.2.1 Stack protection

As described in Section 2.1.2, the stack is the area most vulnerable to payload injection attacks so that various protection schemes have been proposed for it. This section discusses countermeasures against payload injection attacks that exploit this stack overflow vulnerability.

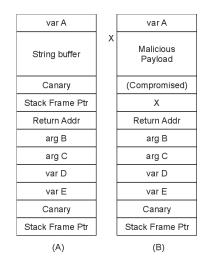

**Overflow detection:** The most straightforward solution to the buffer overflow vulnerability is to check the integrity of control flow data at its de-reference. In StackGuard (11), an additional piece of data called a "canary" is placed between a buffer and a memory word containing a return address in the stack layout in order to detect an overflow. This protection is based on the observation that "overflowing" in the stack corrupts not only a return address but also other memory words possibly located between the buffer and the memory word containing the return address. The StackGuard prevents the control flow from being diverted as follows: when a new stack frame is allocated, a canary word is inserted between a buffer and the memory word containing the return address. Before a **return** instruction is executed, an epilogue code checks the canary word to see if the protected return address is compromised or not. If the canary word has a different value from what it had at the time of stack frame allocation, an exception is triggered so that the operating system terminates the infected application or process (Figure 5). If not, program execution continues and the **return** instruction reads the return address. The canary word can have a randomized value so that a sophisticated attack trying to circumvent StackGuard using a static canary value can be thwarted.

As both the prologue code for inserting canaries and the epilogue code for verifying their integrity are generated by a compiler, no source code modification is required – only re-compilation is necessary. However, because StackGuard protects only return addresses in the stack region, other control flow data such as function pointers in the stack or heap region remain vulnerable to sophisticated attacks. In addition, a multi-stage buffer overflow attack is able to locate the return address and to overwrite it precisely without touching the canary, thereby circumventing StackGuard.

**Program counter encryption/decryption:** Although StackGuard can prevent control flow redirection by verifying the integrity of a canary next to a memory word containing the

Figure 5: Changes in a stack frame protected by StackGuard

(A) Stack layout generated by a compiler patched for StackGuard. As shown in (B), the canary value is corrupted during a payload injection attack and the overflow can be detected by software.

return address, it does not actually protect the control flow data itself and therefore circumvention techniques such as a multi-stage overflow attack are effective. Lee and Tyagi (12) introduced a protection scheme by encoding return addresses. In their work, when a **call** instruction is executed to invoke a subroutine, the return address is encrypted before being pushed onto the stack whose top is pointed to by the stack pointer register. It is decrypted before being restored to the program counter for the **return** instruction. A similar scheme was proposed in a hardware implementation by Frantzen (13) and employed in the SPARC processor. In a system protected by these randomization-based countermeasures, an adversary may be able to place their payload in the stack region and corrupt a return address. However, as the overwritten return address has not been properly encrypted, the decrypted value of the return address will point not to the injected payload but to a random location, and the injected code cannot be executed. Unfortunately, such a random jump may result in an undesirable situation – for example, the execution of another procedure located in the same address space, with arbitrary values in the stack frame in use unintentionally referenced as arguments, which could be harmful. In addition, while the return addresses in the stack can be easily identified with the stack pointer register on the fly, other control flow data cannot be protected because it is hard to identify them.

Additional stack frame allocation: Another protection method for a stack region is to save return addresses in a memory region invisible to applications. These saved addresses are reliable return addresses. This protection can be implemented in both hardware and software. In a hardware implementation by Park et al. (14), the Return Address Stack (RAS) is enhanced to be able to hold unlimited entries while a conventional RAS is implemented to store only the most recently stored return addresses with a circular queue structure. In order to store an arbitrary number of return addresses, the RAS is equipped with spill/fill procedure support for overflow/underflows in conjunction with the operating system. Additionally, sophisticated mechanisms to handle non-local jumps and miss-predicted speculative executions are included because these operations will cause false alarms under the present RAS mechanism.

StackShield (15) is proposed as a software approach to give this type of protection. With StackShield, a prologue code moves the return address to a different area when a subroutine is called, and an epilogue code restores the return address upon completing the subroutine. StackShield only protects return addresses and applications using this protection need to be recompiled.

# 2.2.2 Compiler-based protection

Compiler-based protection prevents various attacks at the source code or library level. CCured (16) by Necula transforms an unsafe C source code into a trusted one whose memory safety is guaranteed. In order to ensure safety, memory operations that may create an error, such as an out-of-bound reading, are detected and eliminated during compilation and runtime checks are inserted where such off-line analysis is insufficient. Cyclon (17) by Grossman is a dialect of C, and it is designed to preclude attacks exploiting pitfalls in C. This programming language disallows several syntactical expressions and pointer arithmetic, and replaces them with other expressions with similar or equivalent functionality. Because of these changes, a programmer may need to inspect and modify the source code of the application to be protected. ProPolice (18) by Etho is an enhanced version of StackGuard. This protection not only utilizes canaries, but also rearranges local variables and local array(s) in the stack to make it difficult to corrupt control flow data via an overflow. ProPolice has been widely adopted in Linux-based operating systems as well as the BSD operating system family. However, its protection coverage is limited within a stack, therefore other forms of protection are required in conjunction with ProPolice to guard against attack vectors exploiting other vulnerabilities. Protection performed at the library level (19)(20) substitutes vulnerable functions for safe ones so that vulnerabilities, like buffer overflows from unsafe procedures and format strings, are ineffective at the library level. Because vulnerabilities are handled after the control flow goes into the procedure contained in a library, this protection requires neither modification of source code nor recompilation of an application.

## 2.2.3 Control-flow integrity

Control-flow integrity (CFI), which was proposed by Martín et al. (21), forces software to follow a path in a *Control-Flow Graph* (CFG) determined ahead of time. The CFI approach labels vulnerable indirect branch instructions and their target locations with IDs. There are associated ID checks. Before invocation of an indirect branch, the ID check compares the ID hard-coded prior to the branch with the ID marked in the target location. This comparison verifies that the control flow redirection conforms to the CFG. If the two IDs match, program execution continues to the target location. Otherwise, the ID check invokes a thwarting procedure. Because the ID checks are written with the same instruction set as the protected program, no modification is required to either the OS kernel or the processor hardware.

Although the CFI implementation labels only machine code, nearly half of the labeled codes are referenced as data by an ID check before an instruction fetch. This is because the ID check accesses the target location as data to find the ID marked in the location before control flow redirection. Because of the memory hierarchy, at least one data cache line must serve this ID check but an ID occupies only a small portion of one cache line (4 bytes out of 32 or 64 bytes). This inefficient data cache utilization could result in high data cache miss rates.

## 2.2.4 Randomization in address space

Address space layout randomization (ASLR) makes addresses of various objects, stack frames, and procedures less predictable so that attacks based on knowledge of absolute addresses cannot compromise critical data or divert the control flow into an injected code. Except for absolute addresses, which are decided at compile time, the whole address space of an application is changed every time the application is loaded and executed. These runtime changes help in thwarting attacks that assume that a victim application's address space is static. However, such randomization can only reduce the likelihood of local exploitation – not totally eliminate threats from such exploitations. Shacham et al. (22) investigate the effectiveness of ASLR in a realistic environment, and they find that, due to the limited number of bits available for randomization in a 32-bit architecture, a simple brute-force attack derived from a standard buffer overflow attack can compromise Apache running on a Linux PaX ASLR system.

# 2.2.5 Non-executable protection

If a memory area is flagged as non-executable then instruction fetches from it are not allowed. Protection measures utilizing this property include hardware extensions or software patches, and many microprocessor vendors provide this protection as a hardware extension under different names- - "NX" for AMD, "XD" for Intel, and "XN" for ARM. In hardware-based protection, memory pages pointed to by translation entries whose "non-executable" property has been set are prohibited from being accessed for instruction fetches. This protection is based on an observation that an adversary places his/her own payload in a writable region such as a stack or heap and executes the payload by redirecting the control flow into the payload. If a process or an application tries to access memory pages with the "non-executable" property for instruction fetch, the processor triggers an exception so that the operating system can handle the violation. In order to utilize this protection, a specified bit field in the control register of the protected system has to be set, and a programmer or operating system has to explicitly declare that the protected page(s) is not-executable when a new page is allocated. This protection has been helpful in thwarting various code injection attacks.

However, this protection can be circumvented or disabled by sophisticated attacks. As discussed in Section 2.1.6, *return-to-libc* can execute pre-existing procedures without injecting a machine code, and return-oriented programming can exploit existing machine code at much more fine granularity. In the Windows operating system family, memory pages protected by this protection<sup>1</sup> can be arbitrarily changed to "executable" if the procedure controlling the corresponding attribute is invoked (1).

# 2.2.6 Virtualization of Harvard architecture

Riley et al. (23) present an architectural approach to preventing code injection attacks by virtualizing the Harvard architecture on the x86 architecture. Their approach is based on the observation that code injection attacks exploit the memory architecture of modern computers the von Neumann architecture – wherein code and data are both addressable within the same address space. Unlike the von Neumann architecture, the Harvard architecture employs a split memory model, enforced at the hardware level, for code and data; therefore it could be suitable for prevention of code injection attacks. In order to virtualize a Harvard architecture in which code and data have their own separate address spaces on the x86 architecture, this approach assigns two sets of physical memory pages for a binary executable during the loading procedure

<sup>&</sup>lt;sup>1</sup>Data Execution Prevention(DEP)

for the binary executable – one for instruction fetches and the other for data accesses. At runtime, it exploits the existing Translation Lookaside Buffer (TLB) to get a physical address for a virtual address according to whether the translation request is an instruction fetch or data access. Additionally, the authors developed this protection to have several attack response modes – break, observe, and forensic mode – so that this protection can be utilized for forensic analysis.

It was shown that this protection can prevent code injection attacks from both benchmarks and real-world examples while overall system performance is acceptable.

## 2.2.7 Static analysis of foreign objects

Basically, some payloads injected by code injection attacks can be regarded as foreign objects. Runtime environments utilize foreign objects in various ways: as temporary data locally stored for fast fetching or processing, or as a binary executable such as a plug-in component. If these objects can be or are designed to be executed verbatim, the corresponding runtime environments must prevent the arbitrary execution of unreliable foreign objects. In this section, we discuss two examples for such protection, and both of them are for web-browsing environments.

Heap-spraying detector with object interpretation: To guard against the heapspraying attack described in Section 2.1.5, Ratanaworabhan et al. (24) presented "NOZZLE," a detector for heap-spraying attacks, which monitors heap activity and reports spraying attempts as they occur. In order to detect malicious attempts to exploit the heap region for heap-spraying attacks, the authors use a two-level detection scheme: local and global. Local detection is performed at the per-object level, and global detection monitors global heap health metrics. At the per-object level, this protection performs a lightweight interpretation of heap-allocated objects, treating them as code. The interpretation includes approaches for analysis – disassembly and building a control flow graph – while focusing on detecting ineffective instruction streams like the "NOP" sled, because they are frequently employed in heap-spraying attacks. Such runtime interpretations are utilized in various applications (25)(26)(27).

Unfortunately, because of the density of the x86 instruction set, even a simple binary sequence composed of alphanumeric characters may look like executable code, so that interpreters are prone to raising false alarms for harmless character strings. In order to mitigate this problem, the global heap health metric is monitored in parallel with the per-object interpretation. As described in Section 2.1.5, an adversary tries to spray as many objects containing a malicious payload as possible to maximize the likelihood of success of the heap-spraying attack. Because the spraying results in a sharp increase in global heap usage, the heap health metric is an indicator for a possible heap-spraying attack. The authors show that this coordination between a local object-based analysis and a global heap health metric can detect a heap-spraying attack under acceptable performance degradation.

Sandbox for untrusted x86 native code: NaCl (Native Client System), introduced by Yee et al. (28), enforces several constraints on a x86 binary executable generated as a plugin component for a web browser. A static analyzer confirms that these constraints have been followed before executing it. As existing plug-in components running on web browsers are handicapped in an application field that requires computational performance, the authors proposed a plug-in-based runtime environment supporting native x86 machine code. For such a runtime environment, they proposed a software sandbox for secure execution of foreign objects. Because software modules running as plug-in components are usually provided as foreign objects, the NaCl runtime environment treats such modules as untrusted binaries and imposes several constraints on their execution rather than relying on non-technical measures for secure execution. These constraints include reliable disassembly for static analysis and 32-bit alignment of instructions for control flow integrity, etc. The static disassembler is employed as a validation component to verify whether the untrusted software module conforms to the constraints before execution. This pre-execution procedure prevents arbitrary execution of an untrusted software module and secures control flow integrity.