# Techniques for scheduling time-triggered resource-constrained embedded systems

Thesis submitted for the degree of Doctor of Philosophy at the University of Leicester

by

Ayman K. G. Gendy

Embedded Systems Laboratory Department of Engineering University of Leicester Leicester, UK

June 2009

# Techniques for scheduling time-triggered resourceconstrained embedded systems

#### Ayman K. G. Gendy

#### Abstract

It is often argued that time-triggered (TT) architectures are the most suitable basis for safety-related applications as their use tends to result in highly-predictable system behaviour. This predictability is increased when TT architectures are coupled with the use of co-operative (or "non pre-emptive") task sets.

Despite many attractive properties, such "time-triggered co-operative" (TTC) and related "time-triggered hybrid" (TTH) architectures rarely receive much attention in the research literature. One important reason for this is that these designs are seen to be "fragile": that is, small changes to the task set may require revisions to the whole schedule. Such revisions are seen as challenging and time consuming. To tackle this problem two novel algorithms (TTSA1 and TTSA2), which help to automate the process of scheduler selection and configuration, are introduced. While searching for a workable schedule, both the algorithms try to ensure that all task constraints are met, a co-operative scheduler is used whenever possible and the power consumption is kept as low as possible. The effectiveness of these algorithms is tested by means of empirical trials.

Both TTSA1 and TTSA2, like most of scheduling algorithms introduced in the literature, rely on knowledge of task worst-case execution time (WCET). Unfortunately, determining the WCET of tasks is rarely straightforward. Even in situations where accurate WCET estimates are available at design time, variations in task execution time, between its best-case execution time (BCET) and its WCET, may still affect the system predictability and/or violate task constraints. In an effort to address this problem, a set of code-balancing techniques is introduced. Using an empirical study it is demonstrated that these techniques help in reducing the variations in task execution time, and hence increase the system predictability. These goals are achieved with a reduced power-consumption overhead, compared to alternative solutions.

#### Acknowledgement

First of all, I would like to express my heartfelt gratitude to Professor Michael Pont. As my supervisor, he has provided me with invaluable guidance and constant support throughout this research project. I consider myself very fortunate for having found such an excellent supervisor. Without him, this thesis would not have been possible.

Next, I would like to thank people in Assiut University in Egypt (especially Prof. Ibrahim H., Prof. Doss M., Prof. Mahdy Y., and Prof. Sewisy A.) for their support and for awarding me the scholarship which gave me the opportunity to pursue my research at the University of Leicester.

I also would like to thank all my colleges at the embedded systems lab and TTE Systems Ltd, Ahmad A., Amir M., Athaide K., Chan K., Bautista R., Edwards T., Hanif M., Hughes Z., Imran S., Key S., Kurian S., Kyriakopoulos I., Lei D., Lakhani F., Mearns D., .Nazri A., Rizvi S., Vidler P., Wang H., Dr. Ayavoo D., Dr. Das A., Dr. Fang J., Dr. Maaita A., Dr. McEwan A., Dr. Mwelwa M., Dr. Nahas M., Dr. Ong R., Dr. Phatrapornnant T., and Dr. Short M. for both their technical and moral supports. It was privilege to work with you all.

A special acknowledge to Chan K. (ESL, Leicester) for his help in making the power measurements, Lakhani F and Wang H. for their help in getting me the papers whenever I needed them, Dr. Nahas M. (ESL, Leicester) for his help in making the measurements of the scheduler overhead, Dr. Ayavoo D. (TTE Systems Ltd) for his help in proofreading earlier version of Chapter 1 of the thesis, and Dr. Demian P. (Loughborough University) for his help in proofreading of the thesis English.

More importantly, I would like to thank my beloved wife, Mary, for her support, encouragement and patience, which I needed the most. You sacrifice your dreams and did everything you can, whether you like or not, for preparing the environment I need during the whole period of my work in this thesis. I hope that God help me in being always beside you doing whatever I can to bring happiness to your loving heart. The great thanks go to the youngest person who brought unbounded joy and happiness to my heat, my son Kyrillos. You were the light that shines in our small family and the source of smile which we need in difficult times.

Last but not least I would like to thank my mother, brother, sisters, mother in law, father in law and brothers in law for their constant support and prayers over the last few years. Thank you all for being there for me, as always. Special thanks to the soul of my father who departed while I was in middle of my work in this project. Your dream of seeing me getting my PhD degree was always in front of my eyes encouraging me especially in hard times. I dedicate this thesis to

my wife, son, mum and the soul of my father

## Table of contents

| ACKNO   | WLEDGEMENT                             | П   |

|---------|----------------------------------------|-----|

| TABLE   | OF CONTENTS                            | I   |

| LIST OI | F FIGURES                              | V   |

| LIST OI | F TABLES                               | IX  |

| LIST OI | F PUBLICATIONS                         | XII |

| LIST OI | F ABBREVIATIONS, SYMBOLS AND UNITS     | XIV |

| CHAPT   |                                        |     |

| 1.1     | INTRODUCTION                           | 1   |

| 1.2     | WHAT IS AN EMBEDDED SYSTEM?            | 2   |

| 1.3     | WHAT IS A REAL-TIME SYSTEM?            |     |

| 1.4     | DEVELOPING REAL-TIME SYSTEMS           | 4   |

| 1.5     | SCHEDULING TIME-TRIGGERED SYSTEMS      | 6   |

| 1.6     | CHALLENGES WITH SIMPLE TT ARCHITECTURE | 7   |

| 1.7     | AIMS OF THE THESIS                     | 9   |

| 1.8     | THESIS CONTRIBUTIONS                   |     |

| 1.9     | THESIS OUTLINE                         |     |

| 1.10    | CONCLUSIONS                            |     |

| CHAPT   | ER 2 SCHEDULING STRATEGIES             |     |

| 2.1     | TASK CHARACTERISTICS                   |     |

| 2.2     | TASK CONSTRAINTS                       |     |

| 2.3     | SCHEDULING CRITERIA                    |     |

| 2.4     | CYCLIC EXECUTIVES                      |     |

| 2.5     | PRIORITY SCHEDULERS                    |     |

| 2.6     | DISCUSSION                             |     |

| 2.7     | CONCLUSIONS                            |     |

| CHAPT   | ER 3 SCHEDULING ALGORITHMS             |     |

| 3.1     | THE FUNCTION OF SCHEDULING ALGORITHMS  |     |

| 3.2   | CHOOSING THE RIGHT SCHEDULING STRATEGY                              | 44 |

|-------|---------------------------------------------------------------------|----|

| 3.3   | CHOOSING THE APPROPRIATE TASK ORDER/STARTING TIME                   |    |

| 3.4   | AUTOMATIC SCHEDULE GENERATION IN REAL-TIME SYSTEMS                  |    |

| 3.5   | PREVIOUS WORK DONE IN ESL FOR AUTO CODE GENERATION FOR TT SYSTEMS   |    |

| 3.6   | DISCUSSION                                                          | 54 |

| 3.7   | CONCLUSIONS                                                         | 54 |

| CHAPT | ER 4 NECESSITY OF STABILISING TASK EXECUTION TIME                   | 56 |

| 4.1   | IMPACTS OF VARIATIONS OF TASK EXECUTION TIME                        |    |

| 4.2   | THE NEED FOR STABILISING THE TASK EXECUTION TIME                    | 59 |

| 4.3   | CHALLENGES WITH ESTIMATING THE TASK EXECUTION TIME                  | 61 |

| 4.4   | DEALING WITH EXECUTION TIME ERRORS                                  | 64 |

| 4.5   | DISCUSSION                                                          | 65 |

| 4.6   | CONCLUSIONS                                                         | 65 |

| CHAPT | ER 5 CODE-BALANCING TECHNIQUES                                      | 67 |

| 5.1   | TOWARD A FIXED EXECUTION PATH                                       | 67 |

| 5.2   | THE SINGLE PATH PROGRAMMING PARADIGM                                | 68 |

| 5.3   | THE PROPOSED CB1 TECHNIQUES                                         | 69 |

| 5.4   | PERFORMANCE OF THE CB1 TECHNIQUES                                   | 73 |

| 5.5   | DISCUSSION                                                          | 83 |

| 5.6   | CONCLUSIONS                                                         |    |

| CHAPT | ER 6 ANALYSIS OF SCHEDULER/TASK CONFIGURATION                       | 85 |

| 6.1   | A CLOSE LOOK AT TTC AND TTH ARCHITECTURES                           | 85 |

| 6.2   | THE NEED FOR APPROPRIATE CONFIGURATION OF SCHEDULER/TASK PARAMETERS | 89 |

| 6.3   | EFFECTS OF TASK OFFSET                                              |    |

| 6.4   | EFFECTS OF TICK INTERVAL                                            |    |

| 6.5   | EFFECTS OF TASK ORDER                                               |    |

| 6.6   | DISCUSSION                                                          |    |

| 6.7   | CONCLUSIONS                                                         |    |

| CHAPT | ER 7 TTSA1 ALGORITHM                                                |    |

| 7.1   | TTSA1 FOR AUTOMATICALLY CHOOSING/CONFIGURING SCHEDULER/TASK PARAMETERS | 104 |  |

|-------|------------------------------------------------------------------------|-----|--|

| 7.2   | EVALUATING THE TTSA1 ALGORITHM                                         | 112 |  |

| 7.3   | DISCUSSION                                                             | 121 |  |

| 7.4   | Conclusions                                                            | 122 |  |

| СНАРТ | ER 8 TTSA2 ALGORITHM                                                   | 123 |  |

| 8.1   | PROBLEMS WITH TTSA1 ALGORITHM                                          | 123 |  |

| 8.2   | TTSA2 ALGORITHM                                                        | 124 |  |

| 8.3   | EVALUATING THE TTSA2 ALGORITHM                                         | 128 |  |

| 8.4   | DISCUSSION                                                             |     |  |

| 8.5   | Conclusions                                                            | 134 |  |

| СНАРТ | ER 9 DISCUSSION AND CONCLUSIONS                                        | 135 |  |

| 9.1   | REASONS AND MOTIVATION OF THE THESIS WORK                              | 135 |  |

| 9.2   | A REVIEW OF THE CONTRIBUTIONS                                          | 136 |  |

| 9.3   | LIMITATIONS AND FUTURE WORK                                            | 142 |  |

| 9.4   | CONCLUSIONS                                                            | 143 |  |

| APPEN | DIX A TT ARCHITECTURES IMPLEMENTED IN ESL                              | 144 |  |

| A.1   | TTC SCHEDULER                                                          |     |  |

| A.2   | TTH SCHEDULER                                                          | 147 |  |

| A.3   | Conclusions                                                            | 148 |  |

| APPEN | DIX B TTSA1 CASE STUDY (SCHEDULER AGENT)                               | 149 |  |

| B.1   | THE BASIC SYSTEM DESCRIPTION AND FUNCTIONALITY                         |     |  |

| B.2   | THE MP-SA ARCHITECTURE                                                 |     |  |

| B.3   | THE MP-SA PERFORMANCE                                                  |     |  |

| B.4   | Conclusions                                                            |     |  |

|       |                                                                        | 1(2 |  |

| APPEN |                                                                        |     |  |

| C.1   | THE BASIC SYSTEM DESCRIPTION AND FUNCTIONALITY                         |     |  |

| C.2   | TASK SPECIFICATIONS                                                    |     |  |

| C.3   | TASK SCHEDULING ACCORDING TO ONE SEGMENT PER TASK                      |     |  |

| C.4   | TASK SCHEDULING WITH CONSIDERING MULTIPLE SEGMENTS PER TASK            | 164 |  |

| C.5  | CONCLUSIONS | <br> |

|------|-------------|------|

| REFE | RENCES      | <br> |

| FIGURE 1-1 INTEL 4004 MICROPROCESSOR AND BUSICOM 141-PF PRINTING                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------|

| CALCULATOR. THESE TWO IMAGES HAVE BEEN USED WITH PERMISSION FROM                                                                    |

| INTEL MUSEUM (INTEL, 2009)                                                                                                          |

| FIGURE 1-2 RTOS BASIC SERVICE GROUPS, REDRAWN FROM (KALINSKY, 2005) (FIGURE 1)                                                      |

|                                                                                                                                     |

| FIGURE 2-1 TYPICAL TASK PARAMETERS                                                                                                  |

| FIGURE 2-2 CYCLIC EXECUTIVE SCHEDULER FOR THE TASK SET SHOWN IN TABLE 2-124                                                         |

| FIGURE 2-3 RM SCHEDULE OF THE TASK SET SHOWN IN TABLE 2-2                                                                           |

| FIGURE 2-4 DM SCHEDULE FOR THE TASK SET SHOWN IN TABLE 2-3                                                                          |

| FIGURE 2-5 EDF SCHEDULE FOR THE TASK SET SHOWN IN TABLE 2-4                                                                         |

| FIGURE 2-6 LLF SCHEDULE FOR THE TASK SET SHOWN IN TABLE 2-5, ADAPTED FROM<br>COTTET <i>ET AL.</i> (2002)                            |

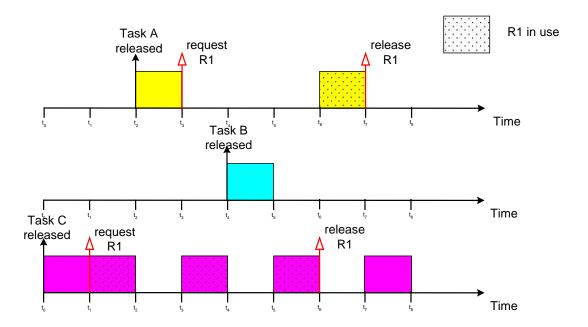

| FIGURE 2-7 ILLUSTRATION OF THE PRIORITY INVERSION PHENOMENON FOR TASKS<br>SHOWN IN TABLE 2-6, ADAPTED FROM SHA <i>ET AL.</i> (1990) |

|                                                                                                                                     |

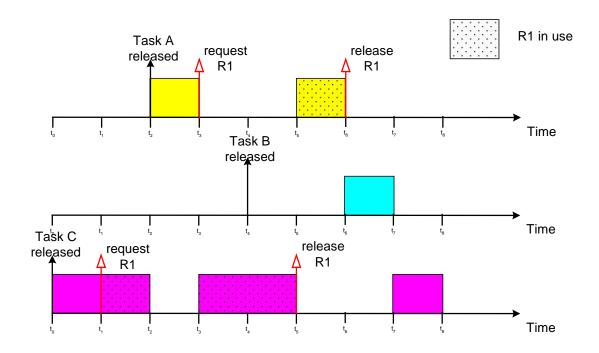

| FIGURE 2-8 ILLUSTRATION OF USING THE PRIORITY INHERITANCE PROTOCOL FOR                                                              |

| TASKS SHOWN IN TABLE 2-6, ADAPTED FROM SHA ET AL. (1990)                                                                            |

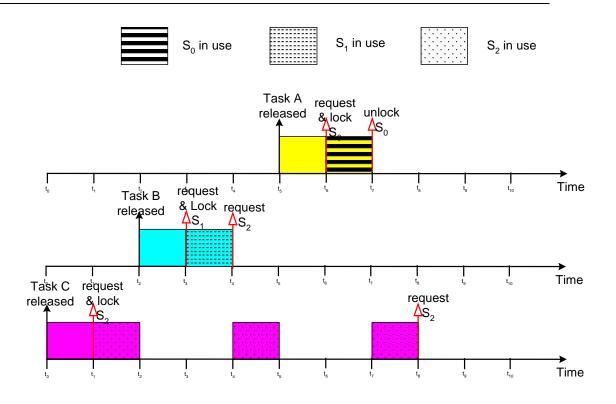

| FIGURE 2-9 ILLUSTRATION OF THE DEADLOCK PHENOMENON FOR TASKS SHOWN IN TABLE 2-7, ADAPTED FROM SHA <i>ET AL.</i> (1990)              |

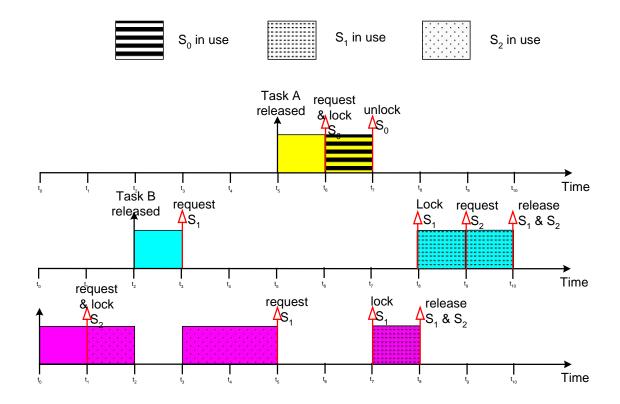

| FIGURE 2-10 ILLUSTRATION OF USING THE PRIORITY CEILING PROTOCOL FOR TASKS                                                           |

| SHOWN TABLE 2-7, ADAPTED FROM SHA ET AL. (1990)                                                                                     |

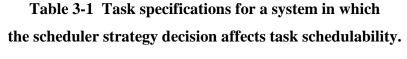

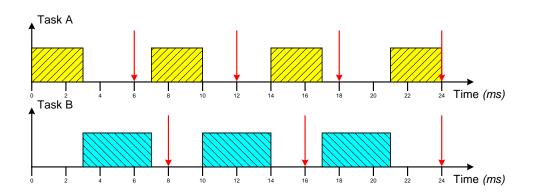

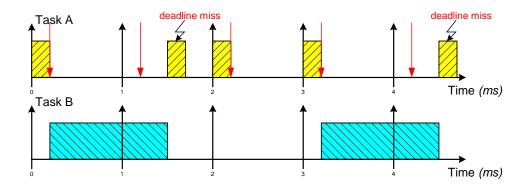

| FIGURE 3-1 INFEASIBLE RM SCHEDULER FOR TASK SHOWN IN TABLE 3-1, ADAPTED<br>FROM XU AND PARNAS (2000)45                              |

| FIGURE 3-2 FEASIBLE NON PRE-EMPTIVE EDF SCHEDULER FOR TASK SHOWN IN TABLE                                                           |

| 3-1, ADAPTED FROM XU AND PARNAS (2000)46                                                                                            |

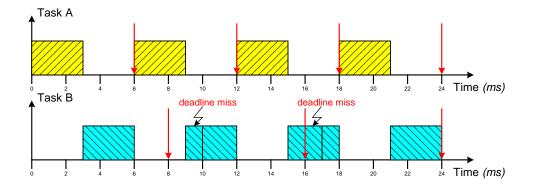

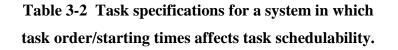

| FIGURE 3-3 INFEASIBLE FIXED PRIORITY SCHEDULER FOR TASK SET SHOWN IN TABLE 3-2, ADAPTED FROM XU AND PARNAS (2000)                   |

| FIGURE 3-4 FEASIBLE SCHEDULER FOR TASK SET SHOWN IN TABLE 3-2, ADAPTED FROM                                                         |

| XU AND PARNAS (2000)                                                                                                                |

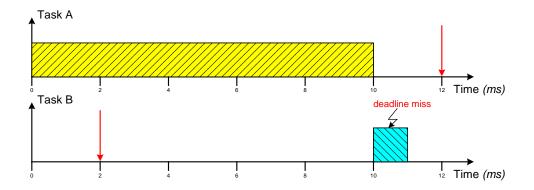

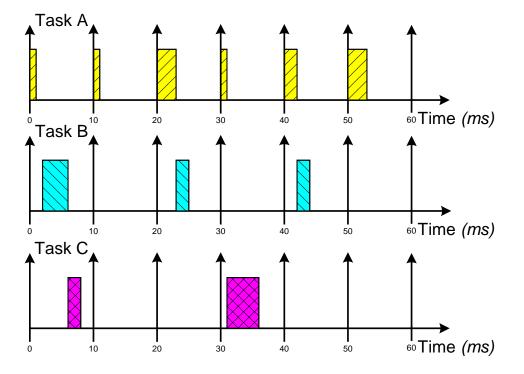

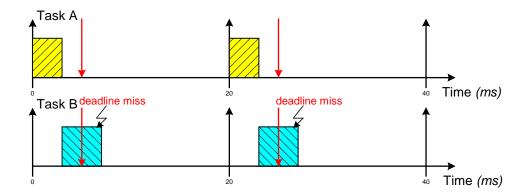

| FIGURE 4-1 TASK SCHEDULE WHEN TASKS SHOWN IN TABLE 4-1 RUN WITH THEIR                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

| BCETS5                                                                                                                                        |

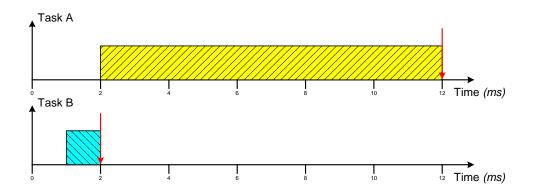

| FIGURE 4-2 TASK SCHEDULE WHEN TASKS SHOWN IN TABLE 4-1 RUN WITH THEIR WCETS                                                                   |

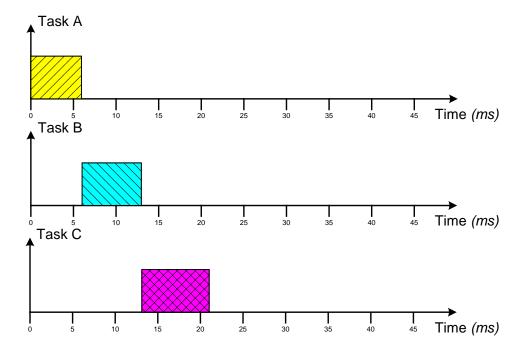

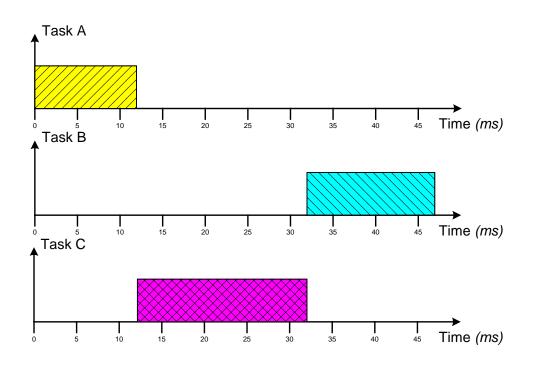

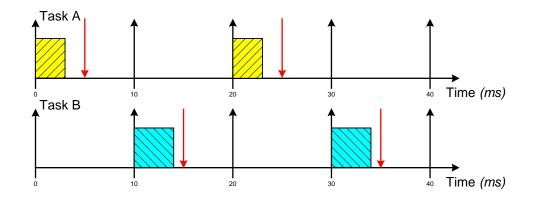

| FIGURE 4-3 TASK SCHEDULE FOR TASKS SHOWN IN TABLE 4-2                                                                                         |

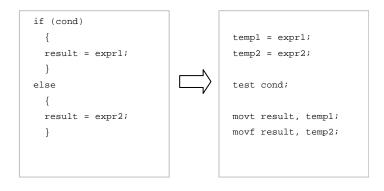

| FIGURE 5-1 CONVERTING <i>IF-THEN-ELSE</i> STRUCTURE TO SINGLE PATH, ADAPTED FROM (PUSCHNER AND BURNS, 2003)                                   |

| FIGURE 5-2 PSEUDO CODE OF A BALANCED FOR-LOOP                                                                                                 |

| FIGURE 5-3 PSEUDO CODE OF A BALANCED WHILE-LOOP USED FOR WAITING FOR INPUT                                                                    |

| FIGURE 5-4 PSEUDO CODE OF A BALANCED <i>IF-THEN-ELSE</i> STRUCTURE, ADAPTED FROM (PUSCHNER AND BURNS, 2003)                                   |

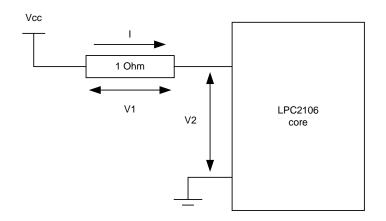

| FIGURE 5-5 THE CIRCUIT USED TO MEASURE THE SYSTEM POWER CONSUMPTION,<br>COPIED FROM NAHAS (2009)                                              |

| FIGURE 5-6 TRADITIONAL IMPLEMENTATION OF BUBBLE SORT                                                                                          |

| FIGURE 5-7 SINGLE PATH IMPLEMENTATION OF BUBBLE SORT (ADAPTED TO WORK<br>WITHOUT THE SUPPORT OF THE CONDITIONAL MOVE INSTRUCTION) (PART 1/2)7 |

| FIGURE 5-8 CB1 IMPLEMENTATION OF BUBBLE SORT (PART 1/2)7                                                                                      |

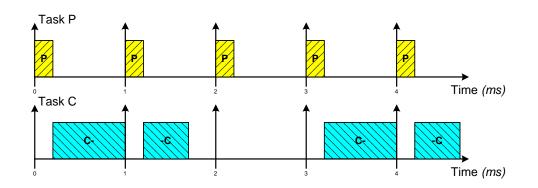

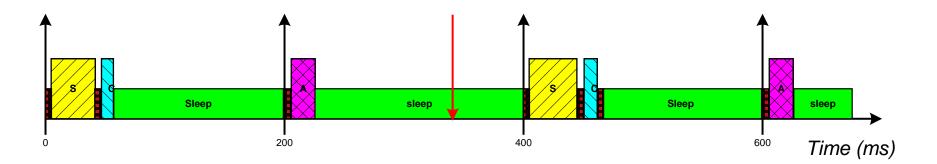

| FIGURE 6-1 ILLUSTRATING THE OPERATION OF A TYPICAL (INTERRUPT-DRIVEN) TTC<br>SCHEDULER IMPLEMENTATION                                         |

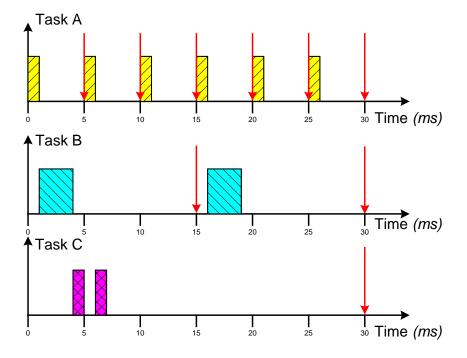

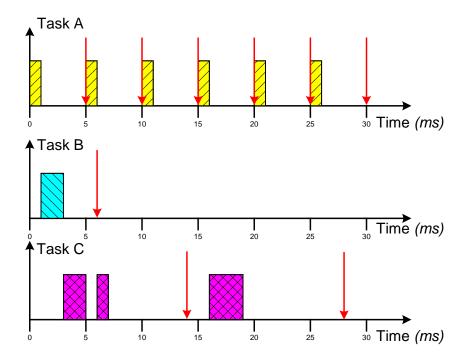

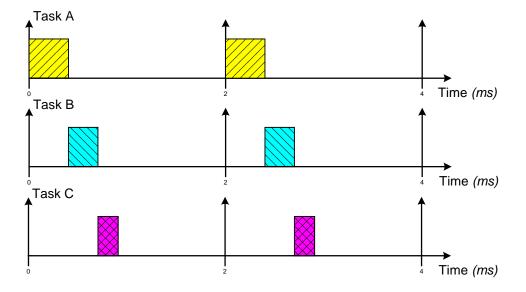

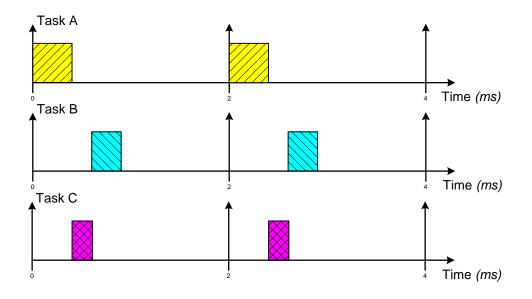

| FIGURE 6-2 ILLUSTRATION OF TTC SCHEDULE OF TASK SET SHOWN IN TABLE 6-2                                                                        |

| FIGURE 6-3 ILLUSTRATING THE OPERATION OF A TYPICAL TTH SCHEDULER<br>IMPLEMENTATION, ADAPTED FROM MAAITA AND PONT (2005B), FIGURE 1            |

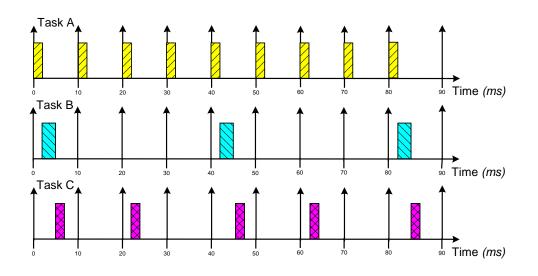

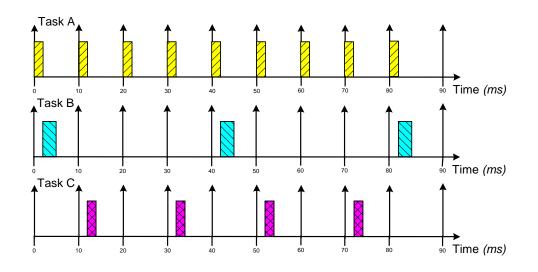

| FIGURE 6-4 TASK SCHEDULE FOR TASKS SHOWN IN TABLE 6-59                                                                                        |

| FIGURE 6-5 TASK SCHEDULE FOR TASKS SHOWN IN TABLE 6-6                                                                                         |

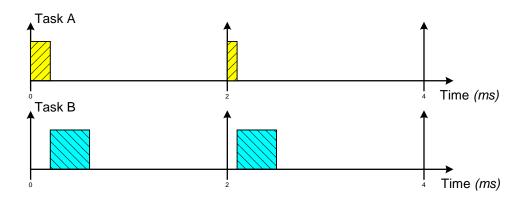

| FIGURE 6-6 TASK SCHEDULE FOR TASKS SHOWN IN TABLE 6-7 (WITH TICK INTERVAL = 2 <i>MS</i> )                                                     |

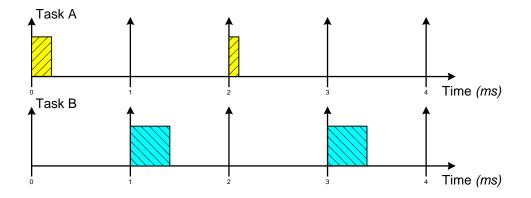

| FIGURE 6-7 TASK SCHEDULE FOR TASKS SHOWN IN TABLE 6-8 (WITH TICK INTERVAL = 1 <i>MS</i> )                                                     |

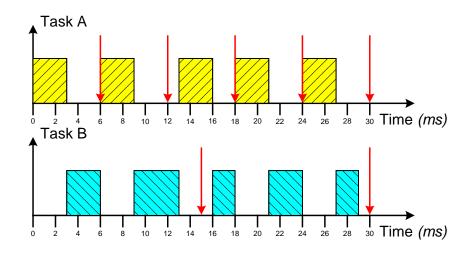

| FIGURE 6-8 TASK SCHEDULER FOR TASKS SHOWN IN TABLE 6-9 (WITH TICK INTERVAL = 2 <i>MS</i> )  |

|---------------------------------------------------------------------------------------------|

| FIGURE 6-9 TASK SCHEDULER FOR TASKS SHOWN IN TABLE 6-10 (WITH TICK INTERVAL = 1 <i>MS</i> ) |

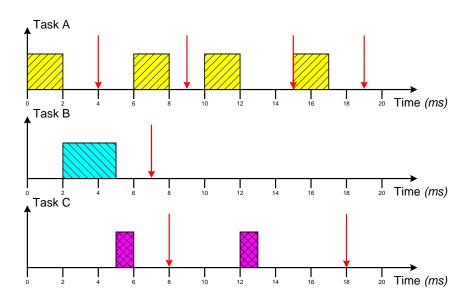

| FIGURE 6-10 INAPPROPRIATE TASK ORDERING FOR TASKS SHOWN IN TABLE 6-12                       |

| FIGURE 6-11 APPROPRIATE TASK ORDERING FOR TASKS SHOWN IN TABLE 6-12100                      |

| FIGURE 6-12 POSSIBLE SCHEDULE FOR TASKS SHOWN IN TABLE 6-13101                              |

| FIGURE 6-13 JITTER-AWARE SCHEDULE FOR TASKS SHOWN IN TABLE 6-13                             |

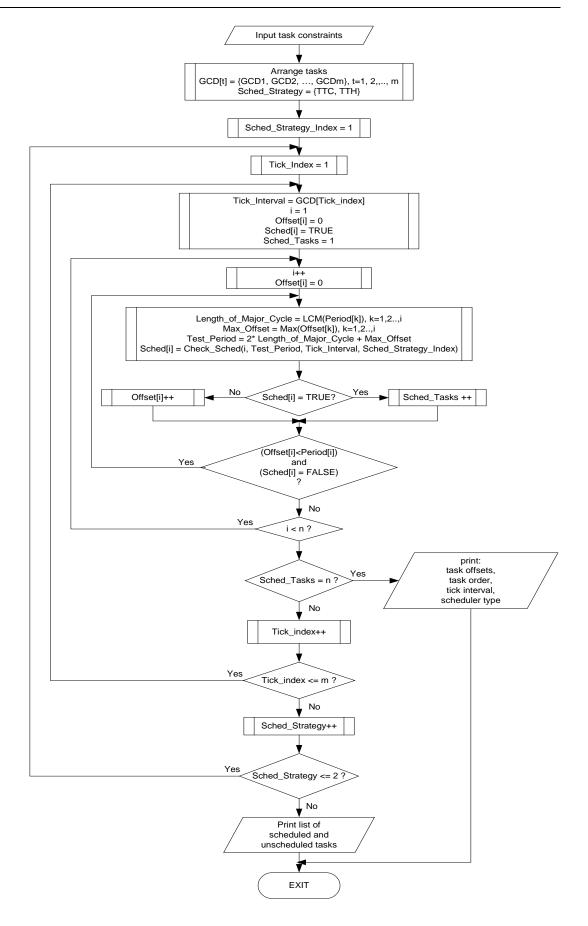

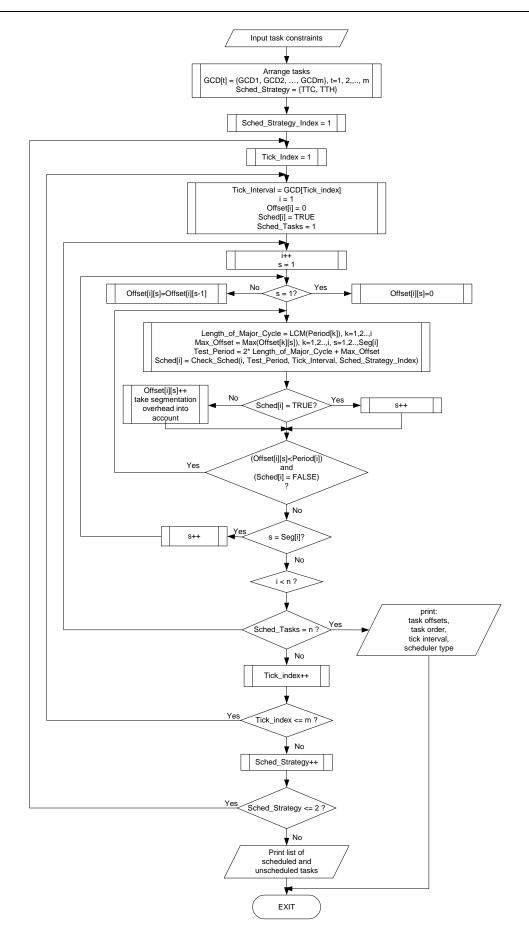

| FIGURE 7-1 FLOW CHART FOR THE TTSA1 ALGORITHM107                                            |

| FIGURE 7-2 FLOW CHART FOR THE CHECK_SCHED() FUNCTION OF TTSA1 ALGORITHM.                    |

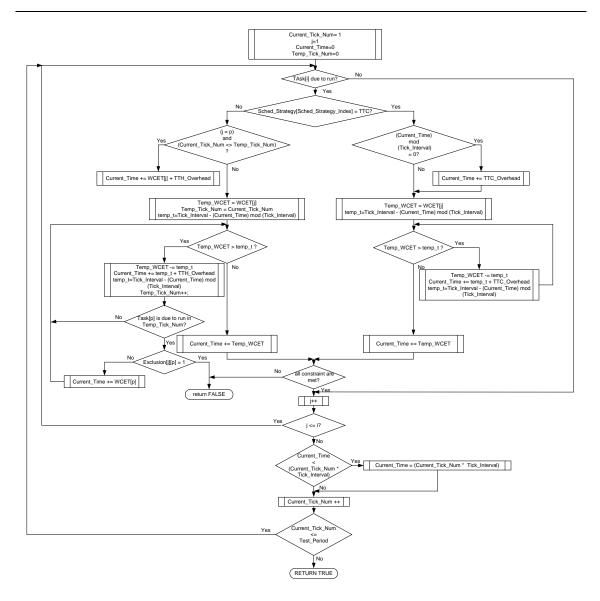

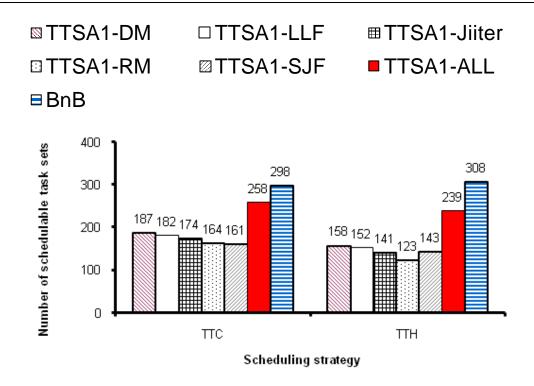

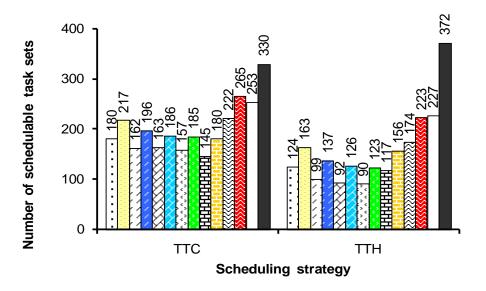

| FIGURE 7-3 NUMBER OF SCHEDULED TASK SETS (3 INTERDEPENDENT TASKS IN EACH SET)               |

| FIGURE 7-4 NUMBER OF SCHEDULED TASK SETS (4 INTERDEPENDENT TASKS IN EACH SET)               |

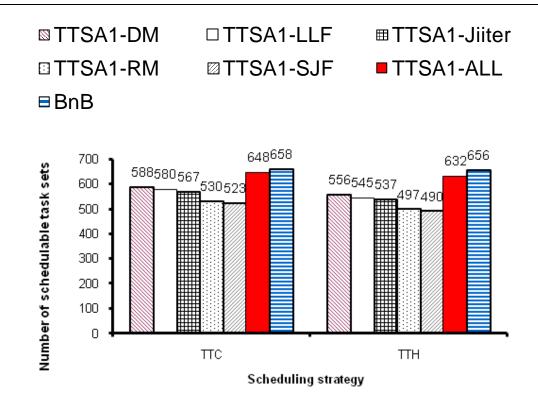

| FIGURE 7-5 NUMBER OF SCHEDULED TASK SETS (5 INTERDEPENDENT TASKS IN EACH SET)               |

| FIGURE 7-6 NUMBER OF SCHEDULED TASK SETS (50 INTERDEPENDENT TASKS IN EACH SET)              |

| FIGURE 8-1 PSEUDO CODE FOR THE TTSA2 ALGORITHM                                              |

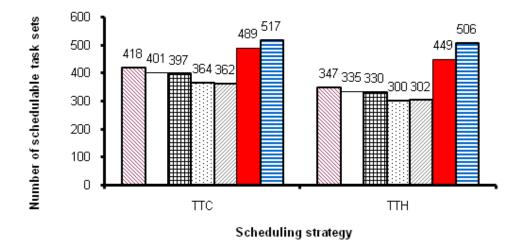

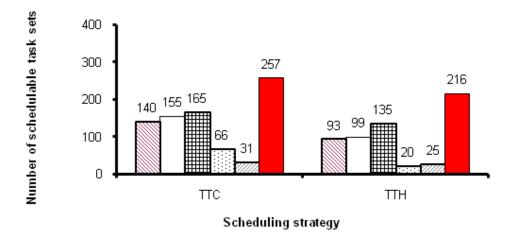

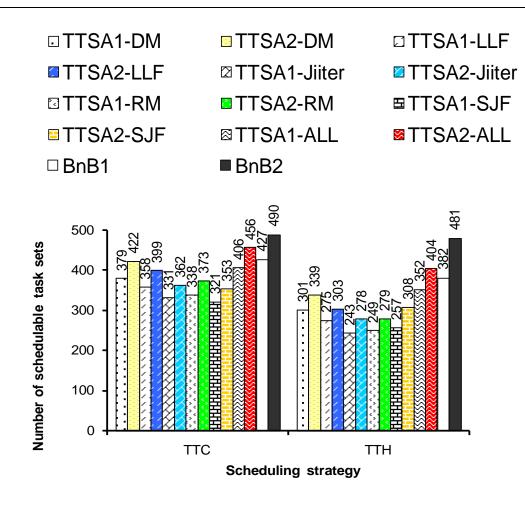

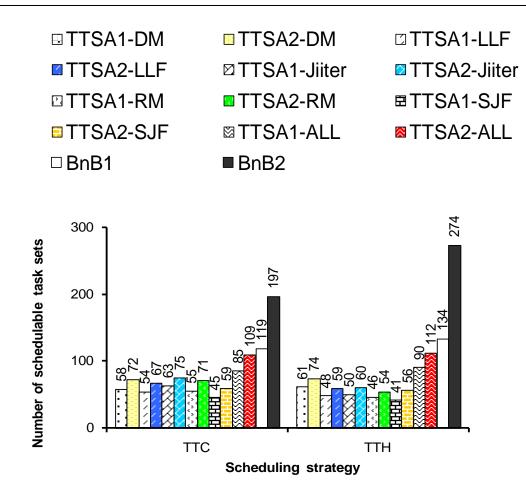

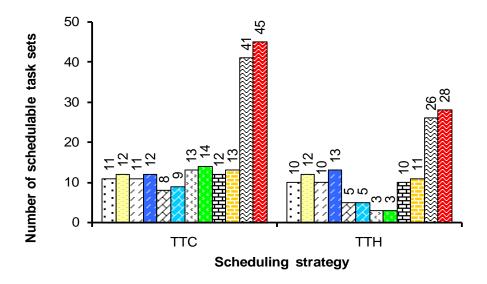

| FIGURE 8-2 NUMBER OF SCHEDULED TASK SETS (3 INTERDEPENDENT TASKS IN EACH SET)               |

| FIGURE 8-3 NUMBER OF SCHEDULED TASK SETS (4 INTERDEPENDENT TASKS IN EACH SET)               |

| FIGURE 8-4 NUMBER OF SCHEDULED TASK SETS (5 INTERDEPENDENT TASKS IN EACH SET)               |

| FIGURE 8-5 NUMBER OF SCHEDULED TASK SETS (50 INTERDEPENDENT TASKS IN EACH SET)              |

| FIGURE A-1 THE MAIN FUNCTION OF A TTC SCHEDULER WHICH EXECUTES THREE          |

|-------------------------------------------------------------------------------|

| PERIODIC TASKS, ADAPTED FROM KURIAN AND PONT (2007)145                        |

| FIGURE A-2 THE DISPATCH FUNCTION OF A TTC SCHEDULER, ADAPTED FROM KURIAN      |

| AND PONT (2007)                                                               |

| FIGURE A-3 THE TICK ISR FUNCTION OF A TTC SCHEDULER, COPIED FROM KURIAN AND   |

| PONT (2007)146                                                                |

| FIGURE A-4 THE TICK ISR FUNCTION OF A TTH, ADAPTED FROM (PONT, 2001)          |

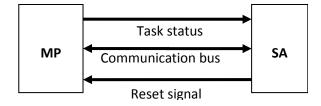

| FIGURE B-1 AN OVERVIEW OF THE MP-SA ARCHITECTURE150                           |

| FIGURE B-2 THE MP-SA HARDWARE                                                 |

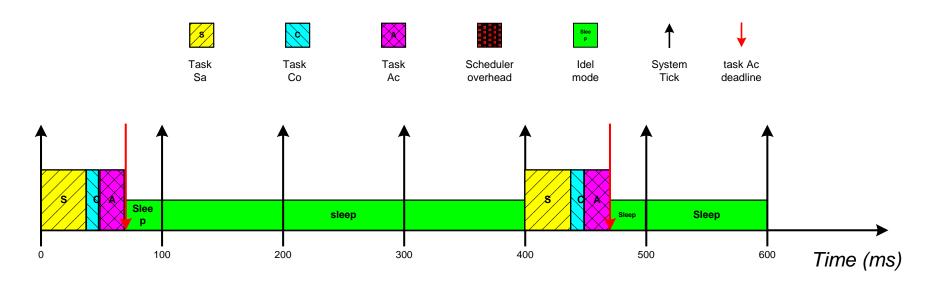

| FIGURE B-3 A SIMPLE SCHEDULE BASED ON THE ESTIMATED BCET AND WCET WITH        |

| 100 <i>MS</i> TICK INTERVAL                                                   |

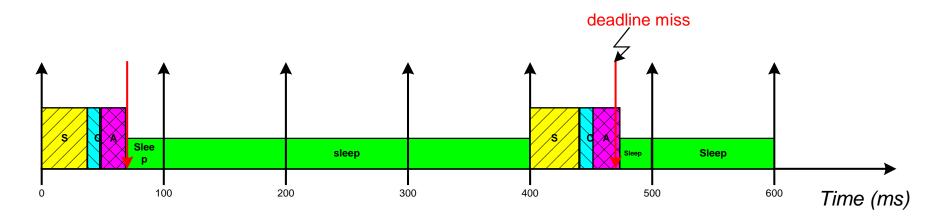

| FIGURE B-4 EFFECT OF INACCURATE ESTIMATIONS OF BCET AND WCET ON TASK          |

| BEHAVIOUR                                                                     |

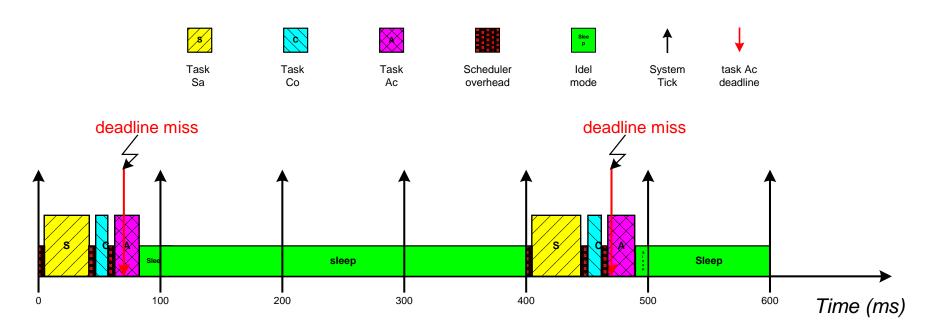

| FIGURE B-5 EFFECT OF SCHEDULER OVERHEAD ON TASK BEHAVIOUR158                  |

| FIGURE B-6 TASK BEHAVIOUR WITH THE SCHEDULER PRODUCED BY THE MP-SA            |

| ARCHITECTURE                                                                  |

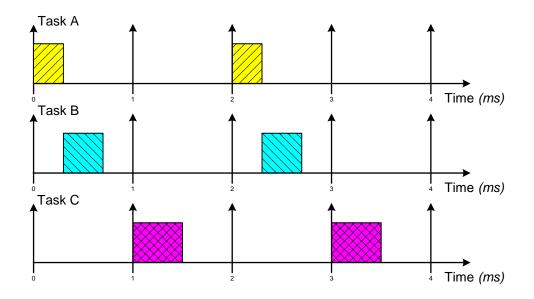

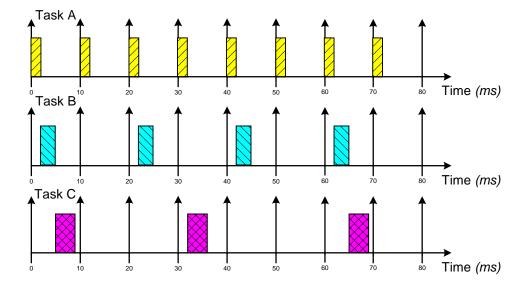

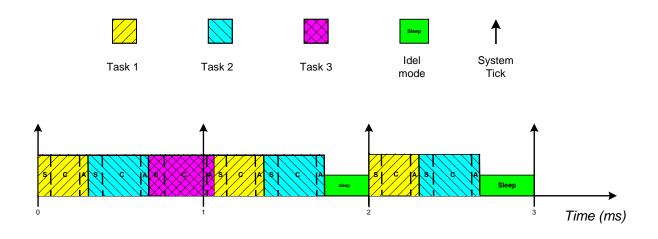

| FIGURE C-1 ILLUSTRATING OF THE FIRST 3 TICKS FOR THE TASKS SHOWN IN TABLE C-1 |

| AND TABLE C-2 SCHEDULED BY TTC WITHOUT CONSIDERING TASK                       |

| SEGMENTATION165                                                               |

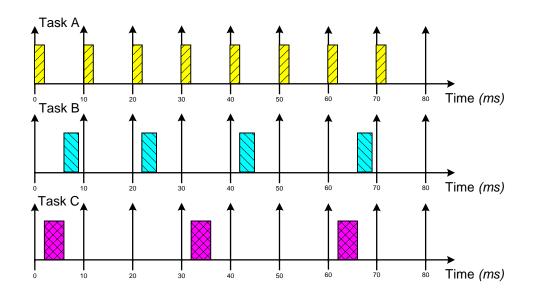

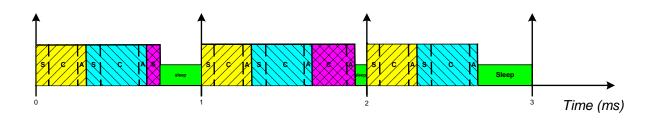

| FIGURE C-2 ILLUSTRATING OF THE FIRST 3 TICKS FOR THE TASKS SHOWN IN TABLE C-1 |

| AND TABLE C-2 SCHEDULED BY TTC WITH CONSIDERING TASK SEGMENTATION             |

| (TTSA2 ALGORITHM)                                                             |

| TABLE 2-1 TASK SPECIFICATIONS FOR A SYSTEM RUNS WITH SIMPLE CYCLIC                                                            |

|-------------------------------------------------------------------------------------------------------------------------------|

| EXECUTIVE SCHEDULER                                                                                                           |

| TABLE 2-2 TASK SPECIFICATIONS FOR A SYSTEM SCHEDULED BY RM SCHEDULER27                                                        |

| TABLE 2-3 TASK SPECIFICATIONS FOR A SYSTEM SCHEDULED BY DM SCHEDULER29                                                        |

| TABLE 2-4 TASK SPECIFICATIONS FOR A SYSTEM SCHEDULED BY EDF SCHEDULER30                                                       |

| TABLE 2-5 TASK SPECIFICATIONS FOR A SYSTEM SCHEDULED BY LLF SCHEDULER32                                                       |

| TABLE 2-6 TASK SPECIFICATIONS FOR A SYSTEM WHICH MAY ENCOUNTER PRIORITY         INVERSION                                     |

| TABLE 2-7 TASK SPECIFICATIONS FOR A SYSTEM WHICH MAY SUFFER FROM         DEADLOCK                                             |

| TABLE 3-1 TASK SPECIFICATIONS FOR A SYSTEM IN WHICH THE SCHEDULER STRATEGY         DECISION AFFECTS TASK SCHEDULABILITY       |

| TABLE 3-2 TASK SPECIFICATIONS FOR A SYSTEM IN WHICH TASK ORDER/STARTING         TIMES AFFECTS TASK SCHEDULABILITY.         47 |

| TABLE 4-1 AN EXAMPLE THAT SHOW THE EFFECT OF VARIATIONS OF EXECUTION TIME         ON TASK ORDER.                              |

| TABLE 4-2 AN EXAMPLE THAT SHOW THE EFFECT OF VARIATIONS OF TASK EXECUTION         TIME ON JITTER.                             |

| TABLE 5-1 MINIMUM, MAXIMUM, (MAXIMUM – MINIMUM), AND PERCENTAGE OF                                                            |

| VARIATIONS (W.R.T. THE MAXIMUM) IN TASK EXECUTION TIME RESULTED FROM                                                          |

| DIFFERENT IMPLEMENTATIONS OF BUBBLE SORT                                                                                      |

| TABLE 5-2 MAXIMUM JITTER AND AVERAGE POWER CONSUMPTION RESULTED FROM         DIFFERENT IMPLEMENTATIONS OF BUBBLE SORT         |

|                                                                                                                               |

| TABLE 5-3 MINIMUM, MAXIMUM, (MAXIMUM – MINIMUM), AND PERCENTAGE OF                                                            |

| VARIATIONS (W.R.T. THE MAXIMUM) IN TASK EXECUTION TIME RESULTED FROM<br>DIFFERENT IMPLEMENTATIONS OF FIBONACCI                |

| TABLE 5-4 MAXIMUM JITTER AND AVERAGE POWER CONSUMPTION RESULTED FROM                                                          |

| DIFFERENT IMPLEMENTATIONS OF FIBONACCI                                                                                        |

|                                                                                                                               |

| TABLE 5-5 MINIMUM, MAXIMUM, (MAXIMUM – MINIMUM), AND PERCENTAGE OF                                                      |

|-------------------------------------------------------------------------------------------------------------------------|

| VARIATIONS (W.R.T. THE MAXIMUM) IN TASK EXECUTION TIME RESULTED FROM                                                    |

| DIFFERENT IMPLEMENTATIONS OF MATRIX MULTIPLICATION                                                                      |

| TABLE 5-6 MAXIMUM JITTER AND AVERAGE POWER CONSUMPTION RESULTED FROM                                                    |

| DIFFERENT IMPLEMENTATIONS OF MATRIX MULTIPLICATION.                                                                     |

|                                                                                                                         |

| TABLE 6-1 EXAMPLE OF TASK SPECIFICATIONS SCHEDULED BY TTC                                                               |

| TABLE 6-2 EXAMPLE OF TASK SPECIFICATIONS WHICH CANNOT BE SCHEDULED BY TTC.                                              |

|                                                                                                                         |

| TADLE ( 2, TASK SPECIFICATIONS FOR A SYSTEM IN WITCH TASK OFFICER ADE                                                   |

| TABLE 6-3 TASK SPECIFICATIONS FOR A SYSTEM IN WHICH TASK OFFSETS ARE         INAPPROPRIATE (TASK C MISSED ITS DEADLINE) |

| INALLKOLKIATE (TASK C WISSED ITS DEADLINE)                                                                              |

| TABLE 6-4 TASK SPECIFICATIONS FOR A SYSTEM IN WHICH TASK OFFSETS ARE                                                    |

| APPROPRIATE. (ALL TASKS MET THEIR DEADLINES)                                                                            |

| TABLE 6-5 TASK SPECIFICATIONS FOR A SYSTEM IN WHICH TASK OFFSETS CAUSE HIGH                                             |

| JITTER91                                                                                                                |

|                                                                                                                         |

| TABLE 6-6 TASK SPECIFICATIONS FOR A SYSTEM IN WHICH TASK OFFSETS CAUSE LOW                                              |

| JITTER                                                                                                                  |

| TABLE 6-7 TASK SPECIFICATIONS FOR A SYSTEM IN WHICH TICK INTERVAL IS                                                    |

| INAPPROPRIATE (TASK B MISSED ITS DEADLINE)94                                                                            |

| TABLE 6-8 TASK SPECIFICATIONS FOR A SYSTEM IN WHICH TICK INTERVAL IS                                                    |

| APPROPRIATE (ALL TASKS MET THEIR DEADLINES)                                                                             |

|                                                                                                                         |

| TABLE 6-9       TASK SPECIFICATIONS FOR A SYSTEM WITH AN INAPPROPRIATE TICK                                             |

| INTERVAL (TASK B SUFFERS FROM JITTER)                                                                                   |

| TABLE 6-10 TASK SPECIFICATIONS FOR A SYSTEM WITH AN APPROPRIATE TICK                                                    |

| INTERVAL (ALL TASKS HAVE LOW JITTER; APPROXIMATELY ZERO)96                                                              |

| TABLE 6.11 AVED ACE DOWED CONSUMPTION (MW) USING DIFFEDENT TICK INTEDVALS                                               |

| TABLE 6-11 AVERAGE POWER CONSUMPTION (MW) USING DIFFERENT TICK INTERVALS.         97                                    |

|                                                                                                                         |

| TABLE 6-12         TASK SPECIFICATIONS FOR A SYSTEM WHERE AN INAPPROPRIATE TASK                                         |

| ORDERING AFFECTS SCHEDULABILITY                                                                                         |

| TABLE 6-13 TASK SPECIFICATIONS FOR A SYSTEM WHERE AN INAPPROPRIATE TASK                                                 |

| ORDERING AFFECTS JITTER                                                                                                 |

| TABLE 7-1 | SAMPLE OF TASK SPECIFICATIONS AND CONSTRAINTS (SET OF 3 TASKS)11      | .6 |

|-----------|-----------------------------------------------------------------------|----|

| TABLE 7-2 | NUMBER OF TRIAL AND THE TOTAL TIME11                                  | 8  |

|           | TASK SPECIFICATIONS FOR A TASK SET THAT CANNOT BE SCHEDULED WITH TH12 |    |

|           | TASK SPECIFICATIONS FOR A TASK SET THAT CAN BE SCHEDULED WITH         | 24 |

| TABLE 8-3 | NUMBER OF TRIALS AND THE TOTAL TIME                                   | ;1 |

| TABLE B-1 | TASK SPECIFICATIONS15                                                 | ;6 |

| TABLE B-2 | EXTENDED TASKS' SPECIFICATIONS16                                      | 50 |

| TABLE C-1 | TASK SPECIFICATIONS FOR THE APPLICATION EXAMPLE16                     | 53 |

| TABLE C-2 | TASK EXCLUSION RELATIONS FOR THE APPLICATION EXAMPLE16                | 54 |

#### List of Publications

A number of papers were published during the course of the work described in this thesis. These are listed below (in reverse chronological order). Please note that the contents of some of these papers have been adapted for presentation in this thesis: where applicable, a footnote at the beginning of a chapter indicates that material from one or more papers has been included.

- Gendy, A. and Pont, M.J. (2008a) "Automatically configuring time-triggered schedulers for use with resource-constrained, single-processor embedded systems," IEEE Transactions on Industrial Informatics, vol. 4, no.1, 37 - 46

- Gendy, A. and Pont, M.J. (2008b) "Automating the processes of selecting an appropriate scheduling algorithm and configuring the scheduler implementation for time-triggered embedded systems," Lecture Notes in Computer Science, Computer Safety, Reliability, and Security, Volume 5219/2008, Springer Berlin / Heidelberg, 27th International Conference on Computer Safety, Reliability and Security, SAFECOMP 2008, 22-25 September 2008, Newcastle upon Tyne, UK , 440-453.

- Gendy, A. and Pont, M.J. (2007) "*Towards a generic 'single-path programming'* solution with reduced power consumption", Proceedings of the ASME 2007 International Design Engineering Technical Conferences & Computers and Information in Engineering Conference (IDETC/CIE 2007), September 4-7, 2007, Las Vegas, Nevada, USA

- Gendy, A., Dong, L. and Pont, M.J. (2007) "Improving the performance of timetriggered embedded systems by means of a scheduler agent", Proceedings of the ASME 2007 International Design Engineering Technical Conferences & Computers

and Information in Engineering Conference (IDETC/CIE 2007), September 4-7, 2007, Las Vegas, Nevada, USA.

Gendy, A. and Pont, M.J. (2007) "Power-aware software design for resourceconstrained embedded systems," Poster presentation at the Festival of Postgraduate Research, 29 July 2007, University of Leicester, Leicester, UK.

Gendy, A. and Pont, M.J. (2006) "Selecting and implementing a custom scheduler for a reliable embedded application," Poster presentation at the IET Postgraduate Workshop on Embedded Systems, 11<sup>th</sup> October 2006 (NEC, Birmingham, in conjunction with the Embedded Systems Show), and Festival of Postgraduate Research, 13 June 2006, University of Leicester, Leicester, UK.

\_\_\_\_\_

- Gendy, A. and Pont, M.J. (in preparation) "Analysis of scheduler/task configuration in time-triggered embedded systems".

- Das, A., Lakhani, F., Gendy, A., and Pont, M.J. (accepted) "*Two simple patterns to support the development of reliable, real-time embedded systems*", EUROPLOP 2009 14th European Conference On Pattern Languages Of Program, July 08, 2009 July 12, 2009, Irsee, Germany.

# List of Abbreviations, Symbols and Units

#### Abbreviations

| BCET  | Best-Case Execution Time                    |

|-------|---------------------------------------------|

| CB1   | Code-Balancing Techniques 1                 |

| CPU   | Central Processing Unit                     |

| DM    | Deadline Monotonic                          |

| DVS   | Dynamic Voltage Scaling                     |

| ECG   | Electrocardiogram                           |

| EDF   | Earliest Deadline First                     |

| EMI   | Electromagnetic Interference                |

| ESL   | Embedded Systems Laboratory                 |

| ET    | Event-Triggered                             |

| GCD   | Greatest Common Divisor                     |

| I/O   | Input / Output                              |

| ISR   | Interrupt Service Routine                   |

| LCM   | Least Common Multiple                       |

| LLF   | Least Laxity First                          |

| MP    | Main Processor                              |

| PTTES | Pattern for Time-Triggered Embedded Systems |

| PC    | Personal Computer                           |

| RM    | Rate Monotonic                              |

| RTOS              | Real-Time Operating System              |

|-------------------|-----------------------------------------|

| SA                | Scheduling Agent                        |

| SA <sub>1</sub>   | Segment 1 of Task A                     |

| SL                | Super Loop                              |

| Time( <i>x</i> ), | Time spent in performing "x" iterations |

| TT                | Time-Triggered                          |

| TTC               | Time–Triggered Co-operative             |

| TTH               | Time–Triggered Hybrid                   |

| TTSA1             | Time–Triggered Scheduling Algorithm 1   |

| TTSA2             | Time–Triggered Scheduling Algorithm 2   |

| WCET              | Worst-Case Execution Time               |

|                   |                                         |

### Symbols

\_

| $AbsJitter(T_i)$ | The absolute jitter of task $T_i$                              |

|------------------|----------------------------------------------------------------|

| $C_i$            | Execution time of task $T_i$                                   |

| $C_i^{(k)}$      | The completion time of the $k^{th}$ invocation of task $T_i$ . |

| $D_i$            | Deadline of task $T_i$                                         |

| L <sub>i</sub>   | Laxity of task $T_i$                                           |

| Ν                | Number of tasks                                                |

| $O_i$            | The offset of task $T_i$                                       |

| $P_i$         | Period of task $T_i$                                                                      |

|---------------|-------------------------------------------------------------------------------------------|

| $P_i^{(max)}$ | The maximum time intervals between successive completions (or invocation) of task $T_i$ ; |

| $P_i^{(min)}$ | The minimum time intervals between successive completions (or invocation) of task $T_i$   |

| $r_i$         | Release time of task $T_i$                                                                |

| $S_i^{(k)}$   | The start time of the $k^{th}$ invocation of task $T_i$ ;                                 |

| и             | Unitization                                                                               |

## Units

| ms | Millisecond |

|----|-------------|

| mW | Milliwatt   |

| S  | Second      |

| μs | Microsecond |

# Chapter 1 Introduction

In this introductory chapter, an overview of the work undertaken in this thesis is introduced and the importance of this area is discussed.<sup>1</sup>

#### 1.1 Introduction

We live in a fast-changing world; new ideas are converted to practical products, which reach consumers over a short period of time. For example while it took about 47 years for the major inventions of the 19<sup>th</sup> century, like telegraph and photography, before their commercial use, the time span is shortened to about 33 years for most of the 20<sup>th</sup> century inventions; such as telephone and electric railroad, and it shrank even more, to be less than 20 years, for recent inventions, time span was approximately 13 years in case of the cellular telephone (Moore and Simon, 2000).

While the above phenomenon, fast time-to-market, is welcome and preferred, other considerations, such as increasing the reliability and reducing the cost of the product, have to be taken into account. Meeting all goals together is a very difficult task, for example it is concluded that meeting the "faster, better, and cheaper" strategy which was adopted by NASA in the early 1990s, need a lot of hard work and careful design which follow thorough on details, otherwise failure is likely to be the result (Musser, 1995; Gregory, 1996; David, 2000). One of the design considerations which can affect the system reliability is the design of the scheduler, that part of the system which decides when each task in the system should run or should use a resource (Zurawski, 2005). The scheduling problem which caused multiple system resets in the NASA Mars Pathfinder (Reeves, 1997) is a well known example of that kind of problem which may arise from scheduling design errors.

<sup>&</sup>lt;sup>1</sup> Parts of this chapter have been published previously in Gendy and Pont (2008a)

The focus of this thesis is on the design of schedulers which can be used in low-cost safety-related embedded-systems.

#### 1.2 What is an embedded system?

Embedded systems can be defined as "*information processing systems that are embedded into a larger product and that are normally not visible to the user*" (Marwedel, 2006). This means that, unlike desktop computer systems, embedded systems have more limited interactions with users and have limited resources (such as small size, low processing power, and small memory) which are dequate to complete their specific operation in the product where they reside.

The first appearance of such systems can be dated back to year 1971, the year in which the first microprocessor, the 4004, was produced by Intel to be used in a series of calculators produced by the Japanese company Busicom (Leventhal, 1979; Barr, 1999; Ganssle and Barr, 2003), as shown in Figure 1-1.

Intel 4004 microprocessor

Busicom 141-PF printing calculator

Figure 1-1 Intel 4004 microprocessor and Busicom 141-PF printing calculator. These two images have been used with permission from Intel Museum (Intel, 2009).

Over the years a great deal of work has been done in the development of the microprocessor which was going in two different trends. The first trend was based on building microprocessors to be used in general purpose desktop systems, including PC's and servers. The other trend was based on developing a special purpose microprocessor, typically called a microcontroller, to be used in embedded applications.

The main difference between a microprocessor and a microcontroller is that a microprocessor contains only a central processing unit (CPU) whereas a microcontroller contains a CPU in addition to memory and input/output (I/O) on the chip (Arnold, 2000).

The vast majority of processors sold every year go to the embedded market. For example in 2005 the total number of embedded processors sold was estimated to exceed 3 billion, compared to 200 million desktop computers and 10 million servers (John and David, 2007). This is a result of the increased demand for new devices, which normally include embedded microprocessor, to be used in every aspect of our modern lifestyle. Examples range from the simple devices used in home appliances (such as microwave ovens, mobile phones, washing machines), to the more sophisticated devices used in the medical sector (such as the mobile ECG), or the automotive industry (for example the Mercedes S-class has 63 microprocessors in it and 1999 BMW 7-series has 65) (Turley, 1999).

#### 1.3 What is a real-time system?

Many embedded systems are also real-time systems. In real-time systems the execution of each function (or task) is constrained by a set of temporal requirements, such as task deadline, the time before which the task should finish its execution (Liu and Layland, 1973; Xu and Parnas, 1993; Tindell, 1994; Sandström and Norström, 2002; Buttazzo *et al.*, 2005). Thus real-time systems can be defined as "*computing systems that must react within precise time constraints to events in the environment*" (Buttazzo, 2005a). This means that the key factor that defines a real-time system is that it produces the correct output within the predefined time limit (Cheng, 2002; Laplant, 2004). Note that – contrary to common usage – this does not necessarily imply either that the system must be fast (Stankovic, 1988) or that the response time of the system must be short (Laplant, 2004; Buttazzo, 2005a), as the required response time depends on the application at hand.

According to Laplant (2004) and Buttazzo *et al.* (2005) real-time systems are usually classified into 3 categories (depending on the criticality of the tasks they perform): hard, firm, and soft real-time systems. They showed that in soft real-time systems the system keeps working at low level of performance in case of failure to meet response-time

constraints, for example: automated teller machine. Whereas in firm real-time systems only a limited number of missed deadlines are allowed, but missing more than this lead to complete and catastrophic system failure, for example: an embedded navigation controller for autonomous robot weed killer. Finally in hard real-time systems a critical and complete system failure can result if a single deadline is missed, example: avionics weapons. To cope with these timing constraints careful designs (both in terms of hardware and software) must be employed in the development process of such applications.

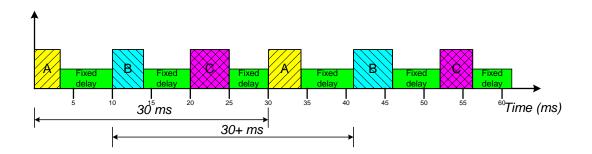

#### 1.4 Developing real-time systems

It can be inferred from the previous section that developers creating software for use in real-time systems face a very different set of challenges from those creating the majority of "desktop" applications. For example the time interval within which the desktop system should respond to a command may vary significantly without causing a major problem whereas even small levels of variation in task stating time, formally called " release jitter", (milliseconds or much less) in safety-related systems may prove life threatening in (for example) an industrial, automotive or medical system. Hence general desktop software architectures (e.g. desktop operating systems) are not suitable for safety-critical applications (Pont, 2001; Cheng, 2002; Buttazzo *et al.*, 2005; Marwedel, 2006).

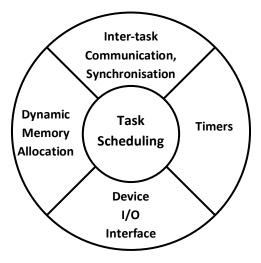

Figure 1-2 shows the main services provided by the kernel of a real-time operating system, RTOS, (Kalinsky, 2005). One of the main components of any RTOS is the task scheduler (Cheng, 2002; Kalinsky, 2005; Marwedel, 2006); moreover "*a scheduler can be viewed as a simple operating system that allows tasks to be called periodically or (less commonly) on a one-shot basis*" (Pont, 2001).

Figure 1-2 RTOS basic service groups, redrawn from (Kalinsky, 2005) (Figure 1).

Depending on the type of the application a wide range of software architecture can be used, from a simple scheduler to a complex full RTOS. However, it is desirable to keep system complexity as low as possible (Pont, 2001) as it may affect both the system reliability and cost. For example cost estimates of embedded software (from commencement to shipping) are quoted around US\$15-30 per line of code, this increases up to \$100 in military defence systems and to approximately \$1,000 for highly critical applications, such as the Space Shuttle (Atkinson *et al.*, 2005). The increased system complexity may result in additional demand for hardware resources (such as memory and CPU processing power) and make the debugging process more difficult. For example making a tiny change, changing just three lines of code, when fixing a bug, in the several-million-line signalling program used in the local telephone systems in California and along the Eastern seaboard caused a breakdown in the system in 1991 (Joch and Sharp, 1995).

There are two common approaches used in scheduling real-time embedded systems: event-triggered (ET) schedulers and time-triggered (TT) schedulers. In ET architectures, tasks are invoked as a response to events represented by external interrupts (Albert, 2004; Scheler and Schröder-Preikschat, 2006), whereas in TT architectures tasks are invoked periodically under the control of a timer (Ludemann, 1983; Volz and Mudge, 1987; Ward, 1991; Kopetz, 1997; Pont, 2001). The ET architecture may be used in systems which have many aperiodic events whereas the TT architecture is the preferred choice for safety-related systems in which the task characteristics are known a priori (Kopetz, 1997; Domaratsky and Perevozchikov, 2000; Pont, 2001; Albert, 2004; Scheler and Schröder-Preikschat, 2006). The work in this thesis focuses on TT architectures.

For resource-constrained embedded systems, which have a very limited memory and CPU performance, a simple "time-triggered co-operative" (TTC) – a form of cyclic executive – scheduler (Baker and Shaw, 1988; Burns, 1995; Kopetz, 1997; Huang *et al.*, 2003; Gangoiti *et al.*, 2005), "*which has low run-time overhead*" (Huang *et al.*, 2003), is often used. Furthermore for safety-related applications which have hard real-time constraints, such as low jitter requirements, the TTC architectures demonstrate very low levels of task jitter (Locke, 1992), and can maintain their low-jitter characteristics even when techniques such as dynamic voltage scaling (DVS) are employed to reduce system power consumption (Phatrapornnant and Pont, 2006).

In most TT designs, an "offline" (also known as "pre-runtime", or "static") schedule is said to be the best choice (Xu and Parnas, 2000; Pont, 2001; Huang *et al.*, 2003; Xu, 2003; Gangoiti *et al.*, 2005).

#### 1.5 Scheduling time-triggered systems

The specific implementation options which are considered here are a time-triggered cooperative (TTC) scheduler (a form of cyclic executive: e.g. Shaw (2001)), and a timetriggered "hybrid" (TTH) scheduler. Such architectures are employed frequently in low-cost control systems (e.g. automotive control: (Ayavoo *et al.*, 2005; Ayavoo, 2006)) and in condition-monitoring / fault diagnosis systems (e.g. Schlindwein *et al.* (1988)). A brief overview of these schedulers will be discussed in the following subsections.

#### 1.5.1 Time-triggered cooperative scheduler (TTC)

The TTC implementation discussed in this work is based on the idea of executing each task in predefined time intervals which are derived from a scheduler tick. The scheduler tick is usually signalled by an interrupt associated with the (periodic) overflow of a hardware timer. At each tick the status of each task is updated and tasks which are due to run are dispatched. Then the processor is usually set to an "idle" (power saving)

mode, where it will remain until the following tick (in order to reduce the system power consumption)

#### 1.5.2 Time-triggered hybrid scheduler (TTH)

Despite some attractive features, a TTC solution is not always appropriate. For example the system cannot respond to an external critical event while executing specific task if the required response time is shorter than the worst-case execution time (WCET) of the running task plus the time required to handle the event (Allworth, 1981). In these cases a fully pre-emptive architecture such as the rate monotonic (RM) or the earliest deadline first (EDF) can be used (Liu and Layland, 1973). Such an approach provides flexibility (and possibly, portability), but it will also tend to increase the system complexity and overhead when compared to pre-run-time scheduling (Xu and Parnas, 2000; Xu, 2003).

In some designs the system responsiveness can be increased while maintaining the minimal resource requirements, by allowing a limited level of pre-emption in the system. This can be done by using what is called a "time-triggered hybrid" (TTH) scheduler (Pont, 2001; Maaita and Pont, 2005a), sometimes called a "multi-rate executive with interrupts" (Kalinsky, 2001). The TTH scheduler can be seen as a RM scheduler that supports a single, short, high priority, pre-empting task, and a collection of co-operative tasks (which have equal priorities lower than that of the pre-empting task).

The pre-empting task may be used for periodic data acquisition, typically by means of an analogue-to-digital converter or similar device. Such requirements are common in, for example, control systems (Buttazzo, 2005b), and applications which involve data sampling and Fast-Fourier transforms (FFTs) or similar techniques: an example is given in the work by Schlindwein *et al.* (1988).

#### 1.6 Challenges with simple TT architecture

Two key challenges facing the developers of simple TTC and TTH designs are the schedule fragility (at design time) and the possibility of task overruns (at run time). These challenges are considered in this section.

#### 1.6.1 The fragility of TTH and TTC designs

It has been shown that – during the design process – TTC / TTH designs are "fragile": that is, small changes to the timing of particular tasks can mean that the developer has to make substantial changes to the whole schedule (e.g. Shaw (2001)). Moreover, it has been demonstrated in previous studies that the problem of testing the schedulability and determining the scheduler and task parameters for a set of tasks for such a system is NP-hard (Brucker *et al.*, 1977; Baker and Shaw, 1988; Tindell *et al.*, 1992; Xu and Parnas, 1992; Xu and Parnas, 2000; Ekelin and Jonsson, 2001; Cucu and Sorel, 2004; Baruah, 2006). Inappropriate choices of parameters may mean that a given task set cannot be scheduled at all. Where the parameter set does ensure that all tasks are scheduled, inappropriate decisions may still lead to unnecessarily high levels of task jitter and / or to increased system power consumption. The focus in this thesis is therefore on developing ways in which the process of configuring TT schedulers for use in single-processor embedded systems can be automated.

#### 1.6.2 Impact of long tasks during system execution

As discussed in the previous section, TTH architectures allow a designer to execute one or more tasks with long WCETs and also respond within a short time interval to external events. This solution can be effective, for many designs, if the WCET of every task is known at design time. Unfortunately, as many researchers have observed (Nett *et al.*, 1996; Domaratsky and Perevozchikov, 2000; Engblom and Ermedahl, 2000; Engblom and Jonsson, 2002; Gergeleit and Nett, 2002; Burguiere and Rochange, 2005; Deverge and Puaut, 2005; Kirner and Puschner, 2008), determining the WCET of tasks is rarely straightforward.

Lack of knowledge about WCETs is a problem which faces the developers of many embedded systems (not just those based on TTC / TTH designs). For example, as Gergeleit and Nett have noted: "*Nearly all known real-time scheduling approaches rely on the knowledge of WCETs for all tasks of the system.*" (Gergeleit and Nett, 2002). Nonetheless, the fact that a TTC / TTH architectures employs static scheduling (and, even in the case of TTH, a very limited degree of pre-emption) means that – in the event of a task overrun – the problem may not even be detected (let alone resolved). This may have a serious impact on the system behaviour. For example, as Buttazzo has noted: "[Co-operative] scheduling is fragile during overload situations, since a task exceeding its predicted execution time could generate (if not aborted) a domino effect on the subsequent tasks" (Buttazzo, 2005b).

As part of an effort to address these problems, the work presented here introduces a set of novel code-balancing techniques which helps to reduce variations in task execution time to a value equal to its WCET. Unlike other methods, these techniques can be adapted to be used with any hardware and have limited impact on system power consumption.

#### 1.7 Aims of the thesis

Despite the attraction of using an offline (or pre-run time) schedulers, such as the TTC and TTH schedulers described above, "*Builders of real-time systems often use priority scheduling in their systems without considering alternatives*" (Xu and Parnas, 2000). The main reason beyond the above argument can be related to the "fragility" of the offline designs of schedulers. It is generally assumed that the effort involved in such a rescheduling process will be very significant. Such arguments have been used in the past as a reason for avoiding TT architectures.

While it can be argued that the issue of TTC/TTH fragility can be exaggerated in situations where appropriate design decisions are taken, it is true that re-scheduling may be required during the development and maintenance of TTC/TTH designs. Given that such a schedule re-design may be required, the aim of this thesis is to explore techniques which can reduce the effort involved in such a process via the use of novel scheduling algorithms.

The second aim of the project is to increase the predictability of systems which use TTC/TTH designs. The proposed scheduling algorithms introduced in this thesis attempt to find a workable schedule that satisfies all task constraints. Like other scheduling algorithms, the proposed algorithms introduced here rely on the availability of accurate estimates of the upper bound of task execution time at design time. Unfortunately determining WCET values is becoming more challenging as embedded designs become more complex and make use of faster and smaller processors and "system on chip" architectures. The work introduced in this thesis introduces new

techniques which aim to reduce variations in task execution time that will in turn reduce difficulties in obtaining the task WCET. More importantly stabilising task execution time will increase the system predictability and determinism, for example the points at which each instance of the task starts, and finishes, can be known in advance.

#### 1.8 Thesis contributions

The project described in this thesis made the following contributions to this research area:

First, problems facing developers of time-triggered architecture (particularly TTC and TTH), such as the need for stabilising the task execution time and carefully choosing task / scheduler parameters are identified. Effects of variations of task execution times, on violating task constraints and / or decreasing the system reliability, are discussed and analysed. Then a set of code-balancing techniques which helps to reduce variations in the task execution time to its WCET, while avoiding excessive increase in power consumption which faces other methods, are introduced.

Second, the need to appropriately choose the right scheduling strategy and configure the task and scheduler parameters is discussed. The effects of inappropriate choices of the scheduler and / or task parameters (such as task offset, task order and tick interval) on task schedulability and system power consumption are discussed and analysed.

Finally, a proposed TTSA1 algorithm which can be used to automate the process of scheduler selection and configuration, while reducing power consumption, for TT schedulers is presented. The proposed algorithm uses a novel two-stage search technique and is intended to support the configuration of time-triggered schedulers for use with resource-constrained embedded systems which employ a single processor. The overall goal is to identify a scheduler implementation which will ensure that: (i) all task constraints are met; (ii) CPU power consumption is "as low as possible"; (iii) a fully co-operative scheduler architecture is employed whenever possible.

The performance of the proposed TTSA1 algorithm is improved by developing the TTSA2 algorithm. This algorithm tries to increase the chance of finding a suitable schedule by dividing some tasks into two, or more, segments, in cases were a suitable schedule can not be found when scheduling each task as one segment. It assumes that

the points at which a task can / cannot be pre-empted / divided into two or more tasks are known in advance.

#### 1.9 Thesis outline

Following this introductory chapter which sets up the background and aims of the current work, Chapter 2 gives an overview of the task model, task parameters and constraints which are normally used in scheduler design. It then discusses various scheduling strategies introduced in the literature.

Chapter 3 reviews previous work in scheduler design and the need for automatic schedule generation in embedded systems.

Chapter 4 discusses the problems encountered form variations in task execution times and the challenges involved in the process of estimating accurate values for task WCET.

Chapter 5 introduces a new set of code-balancing techniques which help to reduce variations in the task execution time, and hence reduce jitter and increase predictability, while avoiding the unnecessary high increase in power consumption caused by other methods.

Chapter 6 discusses the need for choosing the appropriate scheduling strategy and configuring the task and scheduler parameters. The effects of inappropriate choices are also discussed and analysed.

Chapter 7 introduces and evaluates a new heuristic scheduling algorithm "TTSA1" which helps to automate the process of scheduler selection and configuration for single-processor embedded systems. It then discusses the scheduling overhead and its effects on task schedulability. It also introduces an easy way of measuring this overhead and taking its effects into account while designing the scheduler.

In Chapter 8 an improved scheduling algorithm, TTSA2, is presented. The TTSA2 algorithm assumes that points at which a task can be divided / pre-empted (such as critical sections boundaries) are predefined. The TTSA2 uses this information to increase the chance of finding a feasible scheduler for a given task set by dividing one, or more, long tasks into two, or more, segments in case where it is not possible to schedule each task as one segment.

Finally Chapter 9 discusses the work presented in the thesis, gives the conclusions and future work.

#### 1.10 Conclusions

This chapter has presented a background about embedded systems design and emphasised on time-triggered approaches which is to be preferred in safety-related systems. Two main problems which face developers of such systems, scheduler fragility, and difficulties in having accurate estimates of WCET, have been discussed. Techniques to overcome these problems will form the main focus of this document.

# Chapter 2 Scheduling strategies

This chapter gives an overview of the task model, task parameters and constraints which are normally used in scheduler design. Then it discusses various scheduling criteria<sup>2 3</sup> introduced in the literature.

#### 2.1 Task characteristics

Embedded applications are usually implemented as a collection of communicating tasks (Shaw, 2001). In the design phase of such applications each task is used to perform certain function(s). In embedded systems in general, and in safety-related applications in particular, it is not sufficient that the required function is implemented correctly to produce the right output but it has to produce this output at the right time as well (Stankovic, 1988; Cheng, 2002; Laplant, 2004). In order to achieve this each task is assigned a set of timing parameters and constraints, such as period and deadline.

Tasks in embedded application are classified into 3 categories: periodic, aperiodic, and sporadic.

Periodic tasks are repeated or activated frequently; the time between two activations is called the task period (P) (Liu and Layland, 1973). Typical examples of such tasks include sampling and processing of data (Jeffay *et al.*, 1991).

Sporadic tasks are those tasks which are not activated regularly at fixed time intervals but rather they have minimum inter-arrival times. Sporadic tasks can be represented as periodic tasks with periods equal to the minimum inter-arrival time of the equivalent sporadic tasks (Jeffay *et al.*, 1991). A typical example of such tasks includes an alarm or the emergency shutdown of a production robot (Zurawski, 2005).

<sup>&</sup>lt;sup>2</sup> Scheduling criterion describes the basic features of the scheduler (such as TT or ET, online or offline, etc).

<sup>&</sup>lt;sup>3</sup> Scheduling strategy describes the way in which specific property (such as the task period) is assigned to each task.

Aperiodic tasks are those tasks which are activated irregularly. Their invocation time is not known in advance as they can be activated at any time. Typical examples of such tasks include operator's commands and exception handling subroutines (Lin and Tarng, 1991).

The work presented here is concerned with high reliability safety-related applications.

According to the IEC 61508 (IEC, 2005) "The term safety-related is used to describe systems that are required to perform a specific function or functions to ensure risks are kept at an accepted level.<sup>4</sup>". The IEC 61508 is an international standard concerned with safety-related electronic and/or programmable electronic systems.

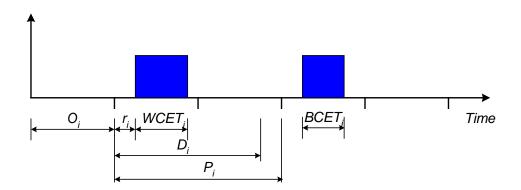

In the worked presented in this thesis it is assumed that task characteristics are known in advance and all the tasks in the system are periodic tasks (and sporadic tasks which are replaced by their equivalent periodic tasks). The following parameters are usually used to characterise each task (Liu and Layland, 1973; Tindell, 1994; Buttazzo *et al.*, 2005), and are shown in Figure 2-1.

- Period (P<sub>i</sub>): is the time interval after which task T<sub>i</sub> should be repeated, in another word it is the length of time between every two invocations.

- Offset (O<sub>i</sub>): is the time, measured from the start of the system power on, after which the first period of task T<sub>i</sub> starts.

- Release time (r<sub>i</sub>): is the time, measured from the start of the task period, after which task T<sub>i</sub> becomes ready to run. In the rest of this document, it will be assumed that all tasks have release time equal to zero; otherwise release time will be explicitly stated.

- Worst-case execution time (WCET<sub>i</sub>): is the longest time taken by the processor to execute task T<sub>i</sub> without pre-emption.

<sup>&</sup>lt;sup>4</sup> This text contains extracts from the <u>IEC Functional Safety Zone</u>. All such extracts are copyright of International Electrotechnical Commission © 2005, IEC, Geneva, Switzerland. All rights reserved. IEC has no responsibility for the placement and context in which the extracts are reproduced. This notice takes precedence over any general copyright statement.

- Best-case execution time (BCET<sub>i</sub>): is the shortest time taken by the processor to execute task T<sub>i</sub>.

- Deadline (D<sub>i</sub>): is the time before which task T<sub>i</sub> should be completed. Deadline can be measured from the start of the system power on, in which case it is called absolute deadline. Alternatively it can be measured from the start of the task period, in which case it is called relative deadline; this is illustrated in Figure 2-1.

Figure 2-1 Typical task parameters.

#### 2.2 Task constraints

As embedded systems become widespread and more complex, developers need ways to specify various application requirements. This is normally done by specifying some restrictions that govern the way in which each task runs and the way in which it interacts with other tasks. These restrictions are usually represented by specifying one or more of the task constraints described below.

#### 2.2.1 Jitter

Many real-time applications require tasks to run at specific time instants, even small variations of these times may cause problems. For example, in multimedia applications, such as CD audio or video, data must be displayed/replayed under relative timing constraints: sample K+1 must be played no later than a fixed interval (e.g., 125  $\mu$ s) once

sample *K* is played (Han *et al.*, 1996). Variations in this time will affect the playback quality.

Another example is a chemical process control system. In such systems it is important that all necessary ingredients are added in at the right times (Han *et al.*, 1996). When scheduling a moving cart to ship the ingredients to the container, it is important to have the cart come in regular intervals so that one ingredient must be added into the container within a certain time after another has been put in (Han *et al.*, 1996).

A final example is the sampling task that used to measure the height of the aircraft. Variations in the interval of executing this task will results in inaccuracy of the aircraft estimated height.

"*Output* [or input] *jitter refers to the variation between the inter-completion* [or activation] *times of successive jobs of the same task*" (Baruah *et al.*, 1999). Jitter can be caused by either hardware or software factors or both. Hardware factors include a drift in the oscillator frequency, noise, or crosstalk caused by electromagnetic interference (EMI) along a circuit or a cable pair (a further discussion are given in Phatrapornnant (2007)). On the other hand software factors include variation in task execution time, task pre-emption, or inappropriate design of the scheduler (Ayavoo *et al.*, 2007; Short and Pont, 2007; Hughes and Pont, 2008). The current work considers only the jitter which results from software factors.

According to Baruah *et al* (1999) the absolute jitter of task  $T_i$  "AbsJitter( $T_i$ )" is defined as:

AbsJitter

$$(T_i) \stackrel{\text{def}}{=} \max(P_i^{(max)} - P_i, P_i - P_i^{(min)})$$

Equation 2-1

where:

$$P_i^{(min)} \stackrel{\text{def}}{=} \min_{k \ge 0} \{ C_i^{(k+1)} - C_i^{(k)} \}$$

Equation 2-2

or

$$P_i^{(min)} \stackrel{\text{def}}{=} \min_{k \ge 0} \{ S_i^{(k+1)} - S_i^{(k)} \};$$

Equation 2-3

and

$$P_i^{(max)} \stackrel{\text{def}}{=} \max_{k \ge 0} \{ C_i^{(k+1)} - C_i^{(k)} \}$$

Equation 2-4

or

$$P_i^{(max)} \stackrel{\text{def}}{=} \max_{k \ge 0} \{S_i^{(k+1)} - S_i^{(k)}\};$$

Equation 2-5

$P_i^{(min)}$  denotes the minimum time intervals between successive completions (or invocation) of task T<sub>i</sub>;

$P_i^{(max)}$  denotes the maximum time intervals between successive completions (or invocation) of task T<sub>i</sub>;

$S_i^{(k)}$  denotes the start time of the k<sup>th</sup> invocation of task T<sub>i</sub>;

$C_i^{(k)}$  denotes the completion time of the k<sup>th</sup> invocation of task T<sub>i</sub>.

For simplicity of notation the "AbsJitter( $T_i$ )" will be simply donated as "Jitter( $T_i$ )" in the remainder of this document.

# 2.2.2 Precedence

Precedence constraints are used to specify the execution order between two tasks (Sandström and Norström, 2002). For example in control application it is required that the sampling process (sampling task) is done first and that it is followed by calculating the control algorithm (control task) and finally the actuation process (actuation task) is run at the end. So the sampling task should precede the control task which in turn should precede the actuation task.

If it is required that task  $T_i$  precedes task  $T_j$ , then, in any tick, task  $T_j$  is allowed to start its execution only after task  $T_i$  completes its execution, i.e. for any *k*:

$$C_i^{(k)} \le S_i^{(k)}$$

Equation 2-6

where: *k* is the  $k^{\text{th}}$  invocation of task  $T_i$  and task  $T_j$ .

## 2.2.3 Exclusion

Exclusion constraints are used to maintain data consistency and control access to shared resources (Buttazzo, 2005a). For example if two tasks, task  $T_i$  and task  $T_{j,i}$ , share one (or more) variable(s), in order to prevent simultaneous updating process of the shared variable(s) by the two tasks an exclusion relation is specified between them. This means that task  $T_i$  is not allowed to pre-empt task  $T_j$  and vice versa; i.e. if task  $T_i$  starts its execution before task  $T_j$  then task  $T_j$  is not allowed to start is execution before task  $T_i$  excludes task  $T_j$  this means that:

if

$$S_i^{(k)} < S_j^{(k)} \Rightarrow C_i^{(k)} \le S_j^{(k)}$$

Equation 2-7

and

if

$$S_j^{(k)} < S_i^{(k)} \Rightarrow C_j^{(k)} \le S_i^{(k)}$$

Equation 2-8

## 2.2.4 Distance

The distance constraint is defined as the minimum time interval between the completion of one task and the start of another task (Sandström and Norström, 2002). A reason for this could be the delays in the communication hardware between two communicating tasks, or the limitations in the processing speed of the environment that the tasks interact with (Ekelin and Jonsson, 1999).

If the distance between task  $T_i$  and task  $T_j$  is required to be Distance(*i*,*j*) this means that:

$$S_j^{(k)} - C_i^{(k)} \ge Distance(i, j)$$

Equation 2-9

## 2.2.5 Latency

The latency relation between any two tasks can be defined as the maximum duration of time between the start of one task and the completion of another task (Sandström and Norström, 2002). For example in control applications it may be required that the time

interval between stating the sampling task to the completion of the actuation task does not exceed a predefined value.

If the latency between task  $T_i$  and task task  $T_j$  is required to be Latency(*i*,*j*) this means that:

$$C_i^{(k)} - S_i^{(k)} \le Latency(i, j)$$

Equation 2-10

# 2.3 Scheduling criteria

As explained in the previous sections, embedded applications are normally developed as a collection of tasks which should run under certain constraints to ensure that the system generates the correct output within the required time interval.

The time and order in which each task should be activated can be configured through the use of an appropriate scheduler. A feasible schedule is that in which all task constraints are met, in which case the set of tasks is called a "schedulable" task set. The scheduling algorithm which is able to find a feasible schedule for any schedulable task set is called an "optimal scheduling algorithm" (Buttazzo, 2005a). In another words an optimal scheduling algorithm can find a feasible (not necessary the best) schedule for a given task set if any other scheduler can, i.e. this optimality is not mean related to the quality of the schedule produced by the optimal scheduler but it is related to its ability to find a feasible schedule.

The following subsections discuss various scheduling criteria.

## 2.3.1 Event-triggered and time-triggered scheduling

The event-triggered and time-triggered scheduling differs in the way in which tasks are called. If tasks are invoked as a response to the occurrence of events represented by external interrupts then the scheduler is event-triggered (ET), whereas tasks in time-triggered (TT) architectures are invoked in a predefined time intervals under the control of timer (Kopetz, 1993; Kopetz, 1997; Albert, 2004).

The question of whether to use the ET or TT architecture has been debated and discussed intensively in the literature (Kopetz, 1991; Kopetz, 1993; Kopetz, 1997;

Domaratsky and Perevozchikov, 2000; Pont, 2001; Albert, 2004; Scheler and Schröder-Preikschat, 2006).

According to Albert: "In general, reality is neither black nor white but rather gray. Thus it depends on the application whether a time-triggered or event-triggered behavior is more suitable" (Albert, 2004). The ET approach may prove cost effective in cases where the system must handle many aperiodic and sporadic events (Kopetz, 1993; Albert, 2004; Scheler and Schröder-Preikschat, 2006), since the conversion of such events to periodic events may reduce the system utilisation. On the other hand timetriggered systems are considered as the preferred choice for supporting safety-related applications (Kopetz, 1997; Domaratsky and Perevozchikov, 2000; Pont, 2001; Scheler and Schröder-Preikschat, 2006). The work in this document focuses on systems with a TT architecture.

## 2.3.2 Pre-emptive and non pre-emptive (co-operative) scheduling

In pre-emptive schedulers a high priority task can pre-empt a lower priority one if the higher priority task becomes ready to run while the lower priority task is still running (Liu and Layland, 1973; Pont, 2001). The context of the pre-empted task (the lower priority task) is saved to enable it later to continue its execution from the point at which it is pre-empted; this context is loaded when the pre-empting task (the higher priority task) finishes its execution. The disadvantages of the pre-emptive scheduler are the imposed overhead necessary for performing this context switching and the necessity for developing mechanisms to manage access to shared resources, so it is desirable to keep the context switching (or the number of pre-emptions) as fewer as possible (Jeffay *et al.*, 1991; Joseph, 1996). On the other hand the main advantage of the pre-emptive scheduling strategy is its responsiveness: when a high priority task becomes ready to run it will immediately gain control of the CPU by pre-empting the current running task (Labrosse, 2002).

By contrast, in non pre-emptive (also called co-operative) schedulers, task(s) is executed to completion without being pre-empted (Pont, 2001; Baruah, 2006). The main drawback of this strategy is its latency to responding to important events: a higher priority task will have to wait until the current running task finishes its execution (Labrosse, 2002). This problem can be solved by dividing long task(s) into two or more shorter tasks (Baker and Shaw, 1988; Locke, 1992; Pont, 2001). The non pre-emptive scheduling has the advantage of requiring low overhead and simple design (as it guarantees exclusive access to shared resources and it has low context switch overhead, the context switch only happen when the task finishes its execution) (Jeffay *et al.*, 1991; Labrosse, 2002). Another advantage is that the interrupt latency is typically low (Labrosse, 2002).

# 2.3.3 Static priority and dynamic priority scheduling

In priority scheduling each task is assigned a specific priority and the schedule is generated based on these priorities (Buttazzo, 2005b). Task priority can be either fixed or dynamic. In the case of static (or fixed) task priority scheduling the priority of each task is decided at design stage and does not change afterward. An example of this scheduler is the rate monotonic (RM) scheduler in which the priority of each task is assigned based on the task period; the shorter the task period the higher its priority (Liu and Layland, 1973). By contrast, in dynamic priority scheduling the priority of each task is dynamically assigned and can be changed at runtime (Buttazzo, 2005b). An example of such scheduler is the earliest deadline first (EDF) scheduler in which the priority of each task depends on its absolute deadline, the sooner the task deadline, with respect to other tasks' deadlines, the higher the task priority (Liu and Layland, 1973).