# Study of Thermal-induced Threshold Switching Devices for Selector Applications

Submitted in partial fulfillment of the requirement for

The degree of

Doctoral of Philosophy

in

Materials Science and Engineering

## Dasheng Li

B.S., Materials Science and Engineering, Beijing University of TechnologyM.S., Materials Science, Carnegie Mellon University

Carnegie Mellon University

Pittsburgh, PA

August 2018

© Dasheng Li, 2018 All Rights Reserved

## Acknowledgements

I would like to firstly thank my advisor, Prof. Marek Skowronski, for offering me the opportunity to work in his group and providing enormous guidance through my Ph.D. research. I would also like to thank Prof. James Bain, who I have kept bothering with all kinds of questions about nanofabrication and finite element simulation. I had limited experience on doing scientific experiments on my own when I joined Carnegie Mellon University and these two professors taught me from the beginning, how to think, how to design the experiments and how to properly do the experiments, which are the precious experience and skills that benefits me for my entire life. I cannot fulfill that much during my Ph.D. without their patient support and endless help. It has been a great journey with them and words are powerless to express my gratitude. Special thanks to my Ph.D. committee members: Prof. Paul Salvador (CMU), Prof. Lisa Porter (CMU) and Prof. Wei Lu (UMich). Thanks for their valuable comments and feedbacks to my research and this dissertation.

There are many people and colleagues that helped me during the last 4 years. Thanks to Dr. Yi Luo, who gave me tremendous guidance on nanofabrication. Thanks to all the senior students I have worked with, Dr. Abhishek Sharma, Dr. Jonghan Kwon, Dr. Greg Slovin and Dr. Min Xu. They taught me all the experimental procedures for electrical testing and fabrication, and their work provided the foundations to my research. Also thanks my current colleagues, Darshil Gala, Yuanzhi Ma, Phoebe Yeoh, Jonathan Goodwill and Yunus Kesim for their help during my research. I would like to express my gratitude to the CMU Nanofab staff members, Dr. Matt Moneck, Norman Gottorn, James Rosvanis, Mason Risley and Mark Weiler for their help with cleanroom equipment. In addition, I would like to thank Xiaoting Zhong, Minyoung Jeong, Yang

Liu, Yining He, Wenjia Song, Ik Soo Kwon, Yu Lin, Jason Gao, Yu-Ting Hsu, Dai Tang and all the friends I have met at Pittsburgh. Thanks for spending time with me to explore the city and enjoy our time here.

Lastly and most importantly, I would like to thank my family for their love and support on me. It is the first time that I have been away from them for such a long period of time and I miss them all the time. I know they are always there for me, encouraging me to grow and to be a better person.

The founding sources for this work are: FAME and LEAST, two of six centers of STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA; NSF Grant DMR 1409068; Data Systems Storage Center at CMU. Also, I acknowledge the support from Neil and Jo Bushnell Fellowship, and acknowledge the use of Materials Characterization Facility at Carnegie Mellon University supported by grant MCF-677785.

## **Abstract**

As the demand for big data applications and faster computation increases, there is an ever-growing need for memory devices with high performance, low cost, and large storage density. Emerging Non-Volatile Memory (NVM) devices such as Phase Change Memory (PCM), Resistive Random Access Memory (RRAM), and Spin-Transfer-Torque Magnetic Random Access Memory (STT-MRAM) are promising candidates for the Storage Class Memory (SCM), which was proposed to be a new class of memory devices to fill the gap between Dynamic Random-Access Memory (DRAM) and storage memory. One of the advantages of NVM is the simple two-terminal device structure, allowing for the crossbar memory array with smallest 4F<sup>2</sup> (F being the lithography feature size) footprint possible. However, such structure needs an access device at each crosspoint in order to reduce the so called "sneak path" effect. The CMOS transistor could serve as an access device but it requires 12 F<sup>2</sup> area. Therefore, the transistor needs to be replaced by a two-terminal selector device that could be stacked on top of the memory element. Threshold switching devices appear to be the best candidate for selectors due to their extreme nonlinearity of *I-V* characteristic. However, the mechanism responsible for the threshold switching has not been well understood in many materials systems. This study focused on understanding the switching mechanism and its characterization in binary transition metal oxide-based devices.

To understand the threshold switching behavior, I have started with VO<sub>2</sub>-based two-terminal planar devices. I developed an electrothermal model based on Joule heating to simulate the quasi-DC device *I-V* and transient response of the device under short pulses at various stage temperatures. The electrothermal model fully reproduced the *I-V* of VO<sub>2</sub> devices in both OFF-state

and ON-state, which allowed to follow the formation and evolution of the conductive filament within the device. The simulated dynamics of threshold switching agreed well with the experimentally measured data across 6 orders of magnitude. The good agreement between simulation and experimental results indicated temperature induced insulator to metal transition in VO<sub>2</sub>-based devices with no evidence of electronically-induced effects. Therefore, the threshold switching behavior in VO<sub>2</sub>-based devices can be explained by a more general Joule heating induced thermal runaway model.

Furthermore, the electrothermal model was applied to  $TaO_x$ -based threshold switches and successfully reproduced the S-shape threshold switching I-V characteristic due to thermal runaway mechanism. To experimentally discriminate the thermal-induced switching from other proposed mechanisms, I used Scanning Thermal Microscopy (SThM) and Scanning Joule Expansion Microscopy (SJEM), two scanning probe thermometry techniques to characterize the temperature profile and thermal expansion profile on the top surface of the  $TaO_x$ -based devices. During the measurements, the devices were biased at several voltages below and up to the threshold voltage ( $V_{TH}$ ). The measurement showed that the temperature increase of 80 K was reached at  $V_{TH}$  to cause the thermal runaway leading to threshold switching behavior. The measurement results experimentally supported the Joule heating induced thermal runaway as the mechanism of threshold switching in  $TaO_x$ -based devices.

By confirming the validity of the thermal-induced threshold switching behavior, I completed a comprehensive simulation study using the electrothermal model on the scaling behavior of three transition metal oxide (VO<sub>2</sub>, TaO<sub>x</sub> and NbO<sub>2</sub>) based selector devices with a vertical crossbar

structure. The device characteristic was simulated as a function of device lateral size, oxide thickness, and stage temperature. The device performance, such as *I-V* characteristic, leakage current, filament size, and temperature in the ON-state were simulated and compared between devices with different dimensions and different materials. The benchmarking of one selector/one resistor (1S1R) cell using the scaled device characteristics with a set of parameters of a generic memory element was also evaluated. Further, the ideal material properties for selector application was calculated based on the figures of merit of the device performance.

# **Table of contents**

| Abstractv |                                                                   |       |

|-----------|-------------------------------------------------------------------|-------|

| L         | List of tables                                                    | lesxi |

| L         | List of figures                                                   | xii   |

| 1         | Introduction                                                      | 1     |

|           | 1.1 Background                                                    | 1     |

|           | 1.2 Resistive Random Access Memory                                | 3     |

|           | 1.2.1 Basic operation of RRAM                                     | 4     |

|           | 1.2.2 Classification of RRAM                                      | 4     |

|           | 1.3 Crossbar array                                                | 8     |

|           | 1.3.1 Array configuration                                         | 8     |

|           | 1.3.2 Sneak path current                                          | 9     |

|           | 1.4 Selector devices                                              | 11    |

|           | 1.4.1 General requirements                                        | 11    |

|           | 1.4.2 Classification of selector devices                          | 14    |

|           | 1.4.3 Switching mechanism of threshold switches                   | 21    |

|           | 1.5 Thesis objective and outline                                  | 26    |

| 2         | Electrothermal model of threshold switching of VO <sub>2</sub> -b | oased |

| d         | levices                                                           | 29    |

|           | 2.1 Introduction                                                  | 29    |

|    | 2.2   | Two-terminal VO <sub>2</sub> -based devices32                          |

|----|-------|------------------------------------------------------------------------|

|    | 2.3   | Modeling methodology33                                                 |

|    | 2.4   | Understanding the mechanism of IMT in VO <sub>2</sub> -based devices35 |

|    | 2.5   | Filamentary behavior in the ON-state41                                 |

|    | 2.6   | Summary46                                                              |

| 3  | Sca   | nning probe thermometry of TaO <sub>x</sub> -based threshold switching |

| de | evice | -s47                                                                   |

|    | 3.1   | Introduction47                                                         |

|    | 3.2   | Fabrication of TaO <sub>x</sub> -based devices49                       |

|    | 3.3   | Electrothermal simulation of TaO <sub>x</sub> -based devices53         |

|    | 3.4   | Scanning probe thermometry measurements setup and calibration56        |

|    | 3     | .4.1 SThM measurement setup and calibration                            |

|    | 3     | .4.2 SJEM measurement setup                                            |

|    | 3.5   | SThM and SJEM measurement results61                                    |

|    | 3.6   | Discussion69                                                           |

|    | 3.7   | Summary72                                                              |

| 4  | Sca   | ling behavior of thermal-induced threshold switching devices           |

|    | 73    |                                                                        |

|    | 4.1   | Introduction                                                           |

|    | 4.2   | Device structure and computation setup74                               |

|   | 4.3  | Scaling trends of <i>I-V</i> characteristic         | 78  |

|---|------|-----------------------------------------------------|-----|

|   | 4.4  | Scaling trend of current density and temperature    | 81  |

|   | 4.5  | Effect of oxide thickness on $V_{TH}$               | 85  |

|   | 4.6  | Effect of sink temperature on device characteristic | 86  |

|   | 4.7  | Benchmarking of thermal-induced selector devices    | 88  |

|   | 4.8  | Discussion                                          | 92  |

|   | 4.9  | Summary                                             | 94  |

| 5 | Sur  | nmary and Future work                               | 96  |

|   | 5.1  | Conclusion                                          | 96  |

|   | 5.2  | Future work                                         | 99  |

| A | ppeı | ndix A. Electrical testing setup                    | 101 |

| R | efer | e <b>n</b> ce                                       | 103 |

## List of tables

| Table 1.1 Memory hierarchy in a computer system.                                                   | 2  |

|----------------------------------------------------------------------------------------------------|----|

| <b>Table 2.1</b> The material properties used in the simulation of VO <sub>2</sub> -based devices. | 35 |

| <b>Table 3.1</b> The material properties used in the simulation of TaO <sub>x</sub> -based devices | 55 |

| <b>Table 4.1</b> The material properties used in the simulation of device scaling behavior.        | 78 |

| Table 4.2 List of parameters of interest for 1S1R cell and selector devices for device             |    |

| benchmarking analysis.                                                                             | 92 |

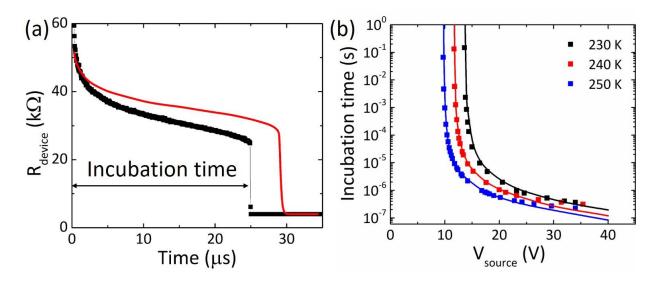

# **List of figures**

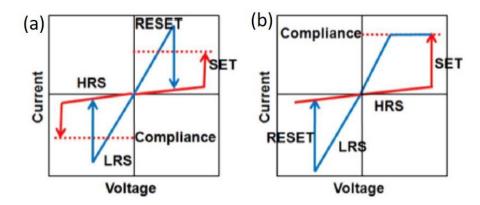

| <b>Figure 1.1</b> Typical DC switching <i>I-V</i> of RRAM devices. (a) Unipolar switching and (b) bipolar                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| switching. Reprinted from reference [10]                                                                                                                         |

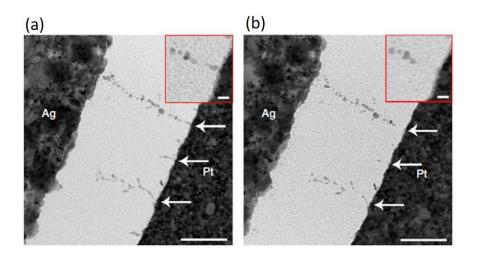

| Figure 1.2 (a) TEM image of SiO <sub>2</sub> based CBRAM after forming. (b) TEM image of the same                                                                |

| device in (a) after RESET. Reprinted from reference [27]                                                                                                         |

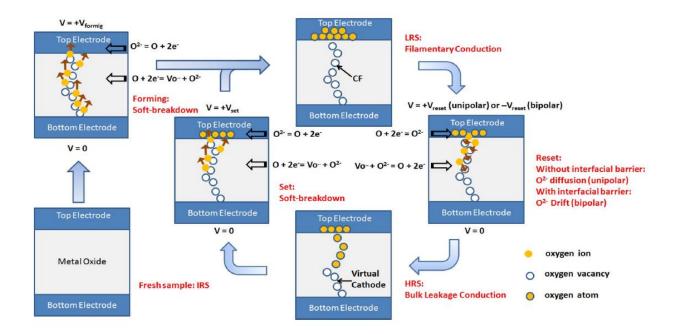

| Figure 1.3 Illustration of the switching process in VCM based RRAM. Reprinted from reference                                                                     |

| [10]8                                                                                                                                                            |

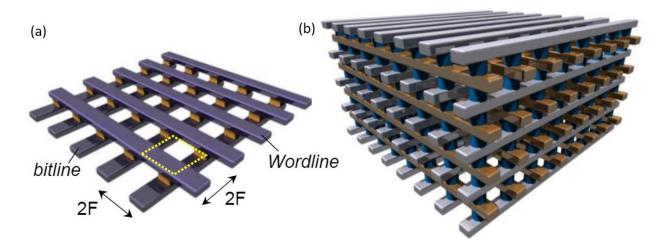

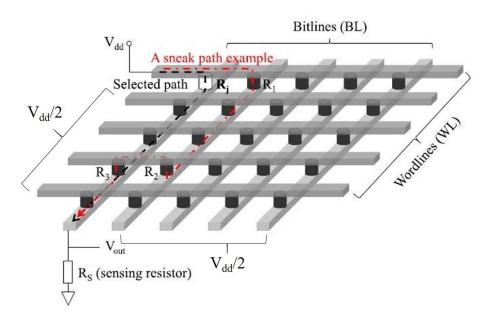

| Figure 1.4 Illustration of (a) 2D cross-point array, and (b) 3D cross-point array. Reprinted from                                                                |

| reference [38]9                                                                                                                                                  |

| Figure 1.5 Illustration of sneak path current in a cross-point array. Reprinted from reference                                                                   |

| [39]                                                                                                                                                             |

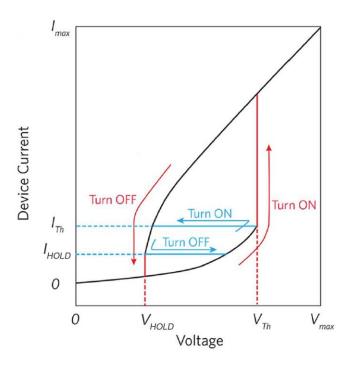

| <b>Figure 1.6</b> The typical <i>I-V</i> characteristic of ovonic threshold switches. Reprinted from reference                                                   |

| [61]                                                                                                                                                             |

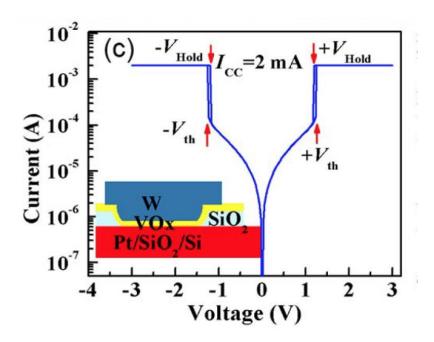

| <b>Figure 1.7</b> <i>I-V</i> characteristic of W/VO <sub>2</sub> /Pt selector device. Reprinted from reference [69] 17                                           |

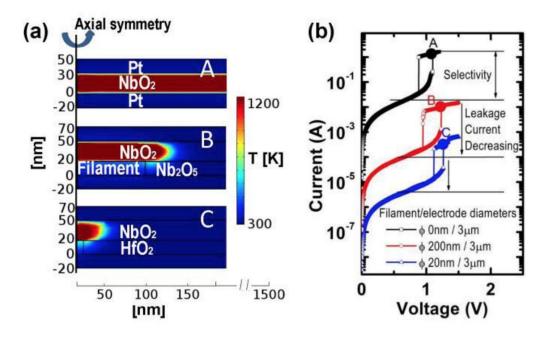

| <b>Figure 1.8</b> Calculated (a) temperature distributions and (b) <i>I–V</i> characteristics for three devices:                                                 |

| Pt/NbO <sub>2</sub> /Pt, Pt/NbO <sub>2</sub> /Nb <sub>2</sub> O <sub>5</sub> /Pt and Pt/NbO <sub>2</sub> /HfO <sub>2</sub> /Pt. Reprinted from reference [72] 18 |

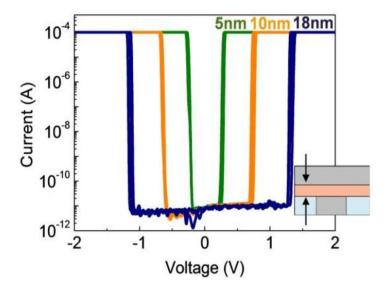

| <b>Figure 1.9</b> <i>I-V</i> characteristic of FAST selector with different thickness of functional layer.                                                       |

| Reprinted from reference [57]                                                                                                                                    |

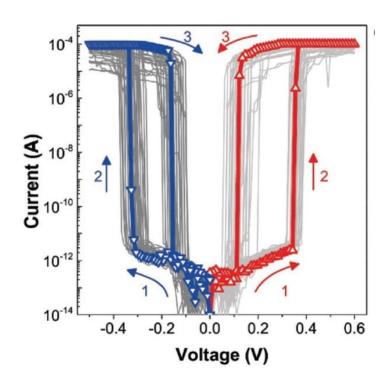

| Figure 1.10 <i>I-V</i> characteristic of Ag/HfO <sub>x</sub> /Ag based selector. Reprinted from reference [58] 20                                                |

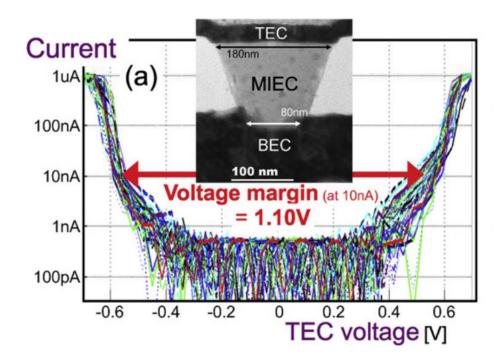

| <b>Figure 1.11</b> <i>I-V</i> characteristic of MIEC selector. Reprinted from reference [59]                                                                     |

| <b>Figure 1.12</b> Measured and calculated <i>I-V</i> characteristic of amorphous Ge <sub>2</sub> Se <sub>2</sub> Te <sub>5</sub> devices.                       |

| Reprinted from reference [84]                                                                                                                                    |

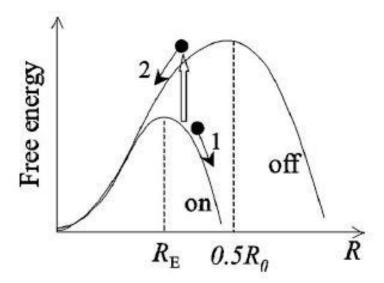

| <b>Figure 1.13</b> The free energy of the nucleus vs its radius for the cases of on and off electric field.      |

|------------------------------------------------------------------------------------------------------------------|

| Arrows 1 and 2 represent the filament radial growth and decay when the field is off,                             |

| respectively. Reprinted from reference [86]                                                                      |

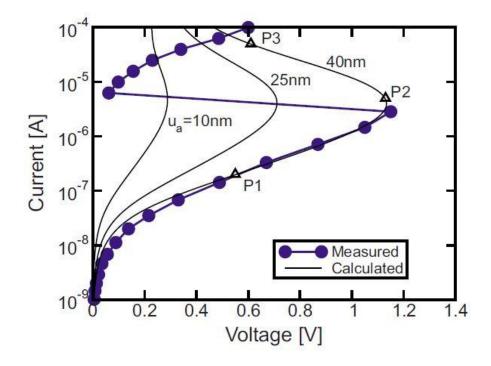

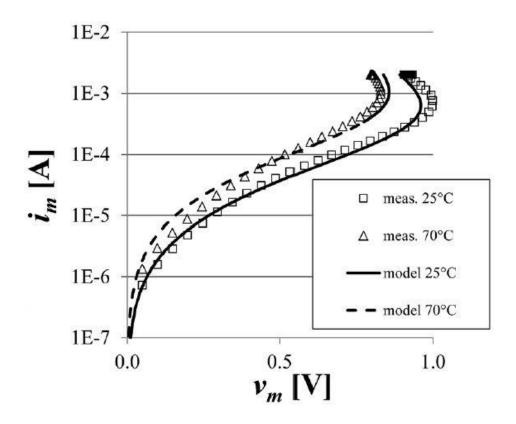

| <b>Figure 1.14</b> Measured and calculated NbO <sub>2</sub> device <i>I-V</i> . Reprinted from reference [90]    |

| <b>Figure 2.1</b> <i>I-V</i> characteristic of VO <sub>2</sub> devices. Reprinted from reference [104]           |

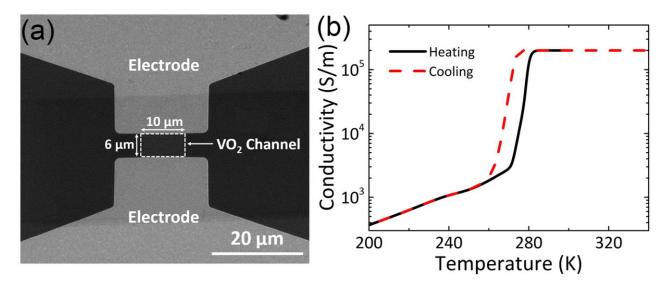

| Figure 2.2 (a) SEM image showing VO <sub>2</sub> device layout and (b) plot of the electrical conductivity       |

| of VO <sub>2</sub> as a function of stage temperature. The black and red lines are, respectively, the            |

| heating and cooling curves for the conductivity                                                                  |

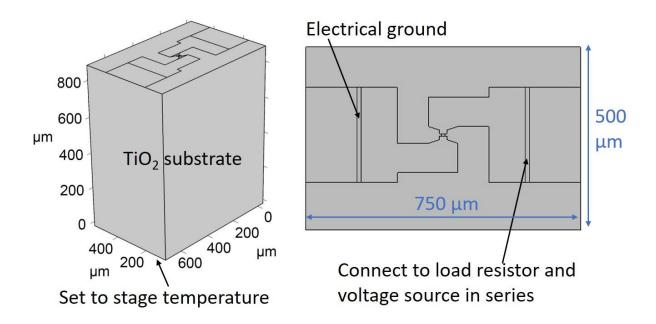

| Figure 2.3 VO <sub>2</sub> device geometry used in the simulation model. Left: the entire device geometry,       |

| with the $TiO_2$ substrate of 750 $\mu m$ length, 500 $\mu m$ width and 900 $\mu m$ thickness. Right: plan       |

| view of the top of the geometry                                                                                  |

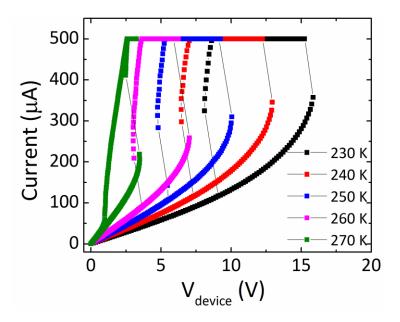

| <b>Figure 2.4</b> DC <i>I-V</i> characteristic of the VO <sub>2</sub> devices at different stage temperatures 36 |

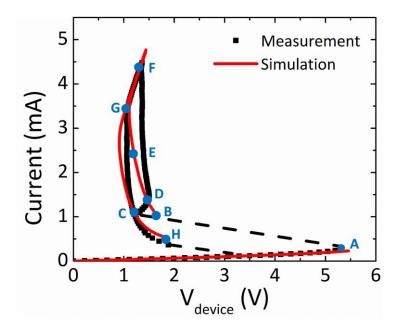

| <b>Figure 2.5</b> (a) Experimental quasi-DC <i>I-V</i> characteristic at 240 K stage temperature (black          |

| squares) and the simulated one using $\sigma(T)$ in Figure 2.2. (b) The simulated device                         |

| temperature profile at $V_{TH}$ at stage temperature of 240 K                                                    |

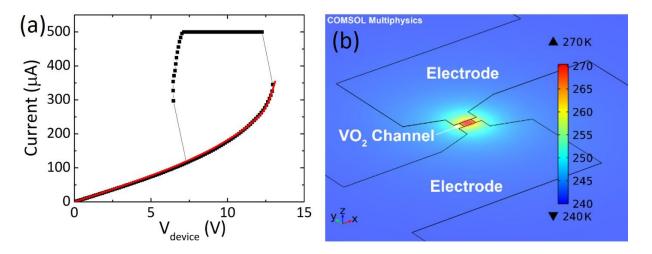

| Figure 2.6 (a) The device resistance as a function of time at 240 K stage temperature and source                 |

| voltage = 13.2 V. Black squares represent experimental points and red line as simulation                         |

| result. (b) Incubation time observed from experimental measurement (dots) and simulation                         |

| results (solid lines) as a function of source voltage at various stage temperatures                              |

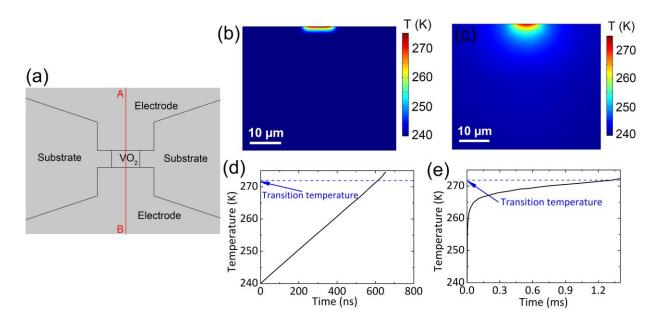

| Figure 2.7 (a) The top view of the device structure used in COMSOL simulation. The                               |

| temperature distribution along the vertical slice through the structure (the A-B line in (a)) at                 |

| the time that the temperature reaches transition temperature during source voltage of (b)                        |

| $27.2 \text{ V}$ and (c) $12 \text{ V}$ . Corresponding simulated maximum temperature rise in the $VO_2$               |

|------------------------------------------------------------------------------------------------------------------------|

| channel with time under source voltages of (d) 27.2 V and (e) 12 V                                                     |

| <b>Figure 2.8</b> Experimental and simulated <i>I-V</i> characteristic at 260 K                                        |

| Figure 2.9 The current density profile of the device during ON-state, corresponding to (a) point                       |

| at the beginning of the ON-state (point B in Figure 2.8), (b) point at the current of 2.4 mA                           |

| (point E in Figure 2.8) and (c) point at which the slope of <i>I-V</i> in the ON-state changes to                      |

| positive (G in Figure 2.8)                                                                                             |

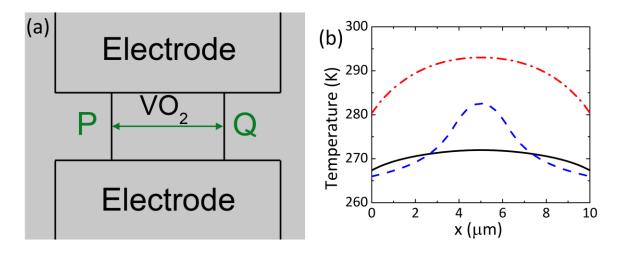

| Figure 2.10 (a) The top view of the device structure, with the 6 $\mu m$ by 10 $\mu m$ VO <sub>2</sub> channel         |

| between two metal electrodes. (b) The temperature distribution along the center of the $VO_2$                          |

| channel (P-Q line with arrows showed in (a)) corresponding to point right before the                                   |

| threshold switching (black line, point A in Figure 2.8), point at the beginning of the ON-                             |

| state (blue dashed line, point B in Figure 2.8) and the point at the entire VO <sub>2</sub> channel                    |

| transitioned to metallic phase (red dash-dot line, point G in Figure 2.8), respectively 45                             |

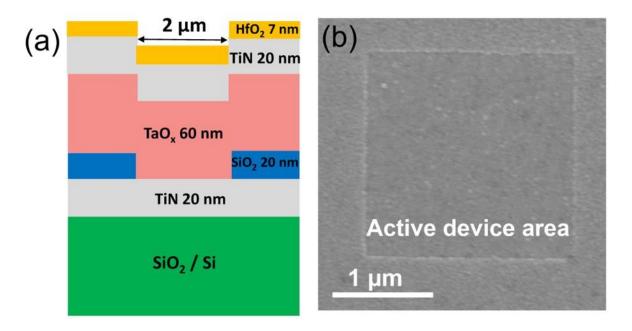

| Figure 3.1 (a) Schematic cross-section of the devices used in this work. (Note that the horizontal                     |

| and vertical scale are different to better highlight the device vertical structure). (b) Scanning                      |

| Electron Microscopy image (top electrode) of the 2 $\mu m \times 2~\mu m$ active device area 51                        |

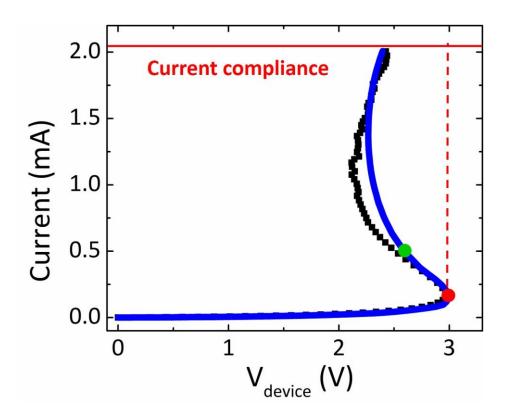

| Figure 3.2 Experimentally measured (black dots) and simulated (blue line) threshold switching                          |

| $\emph{I-V}$ curves of TaO <sub>x</sub> -based devices. The red dot corresponding to the current level at 162 $\mu$ A. |

| The green dot marks the current level at $500\mu\text{A}$ . The red dashed line corresponding to the                   |

| device I-V with vertical snap which would occur if the device were connected with a low                                |

| resistance load                                                                                                        |

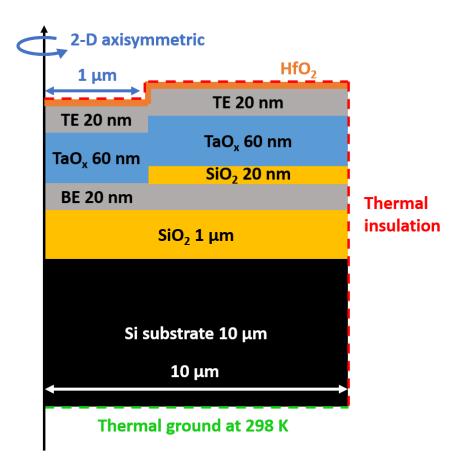

| <b>Figure 3.3</b> The 2D axisymmetric device structure used in the simulation                                          |

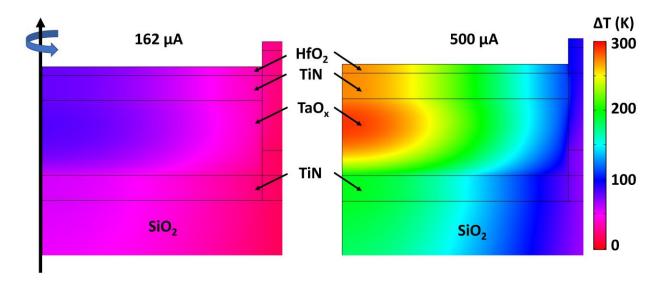

| <b>Figure 3.4</b> Cross-section of the simulated device temperature distributions at $162 \mu A$ (left) and         |

|---------------------------------------------------------------------------------------------------------------------|

| $500\mu\text{A}$ (right). Note that the horizontal scales in the cross-section plots were shrunk (0.3 :             |

| 1) compared to the vertical ones to better highlight temperature variations in the vertical                         |

| direction. The color scale represents the temperature increase with respect to the ambient                          |

| temperature at 298 K                                                                                                |

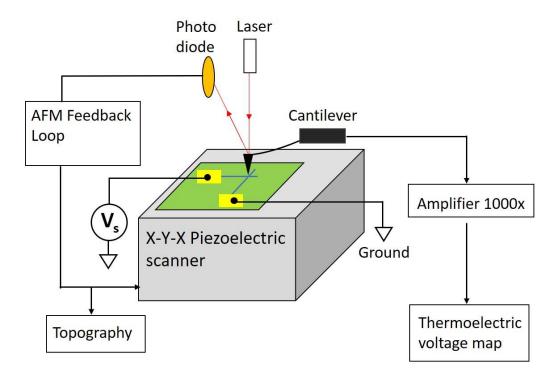

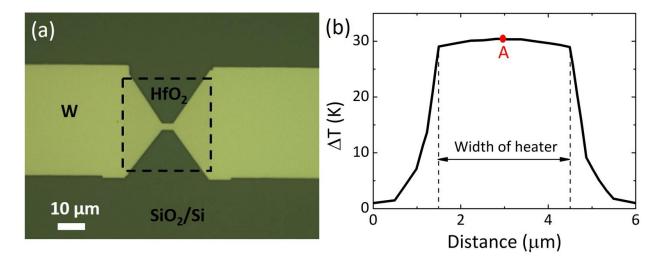

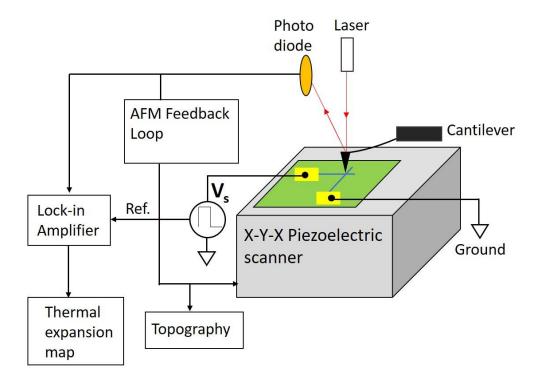

| Figure 3.5 Scanning thermal microscopy measurement setup                                                            |

| <b>Figure 3.6</b> (a) The optical image of tungsten heater structure. The heater has a size of 3 $\mu$ m $\times$ 5 |

| $\mu m$ , located in the middle of the dashed black line. The area within the dashed black line is                  |

| covered by the HfO <sub>2</sub> passivation layer. (b) Simulated temperature increase profile of the                |

| heater structure under DC current at 15 mA                                                                          |

| Figure 3.7 Scanning joule expansion microscopy measurement setup                                                    |

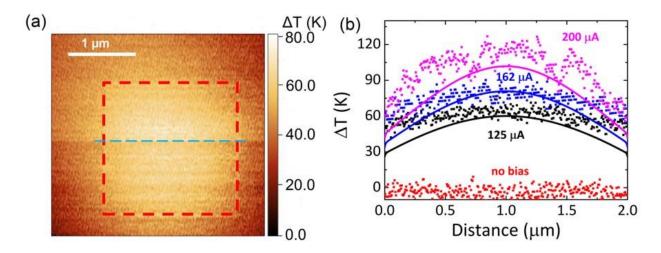

| Figure 3.8 (a) SThM temperature map of a $TaO_x$ switching device under bias at 162 $\mu$ A. The red                |

| dashed box highlights the device active area. The blue dashed line marks the position of the                        |

| measured temperature profiles. (b) Measured (dots) and simulated (lines) temperature line                           |

| profiles across the TaO <sub>x</sub> device at different current levels                                             |

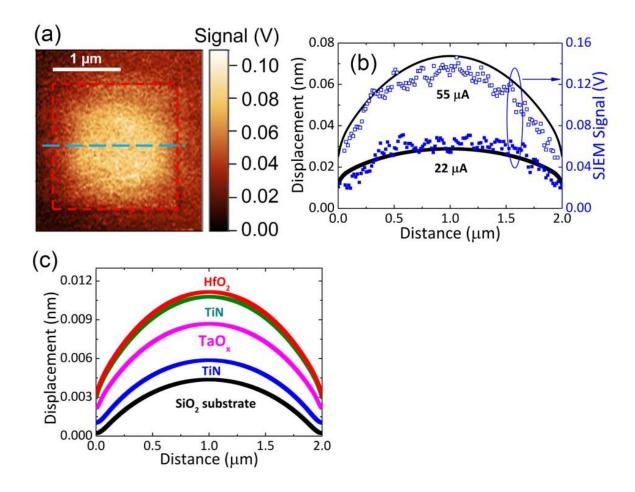

| Figure 3.9 (a) SJEM mapping of the active device area at current of 22 μA. The red dashed box                       |

| highlights the device active area. The blue dashed line marks the position of the measured                          |

| SJEM profiles. (b) The simulated thermal expansion line profiles on the device top surface                          |

| (black lines) are compared to the SJEM data (blue dots) obtained at 22 $\mu A$ and 55 $\mu A$ . (c)                 |

| Simulated thermal expansion on top of each layer at 22 $\mu A$ . The difference between two                         |

| lines in the plot is the expansion value of the layer that is higher in the device stack (see                       |

| Figure 3.1a for reference).                                                                                         |

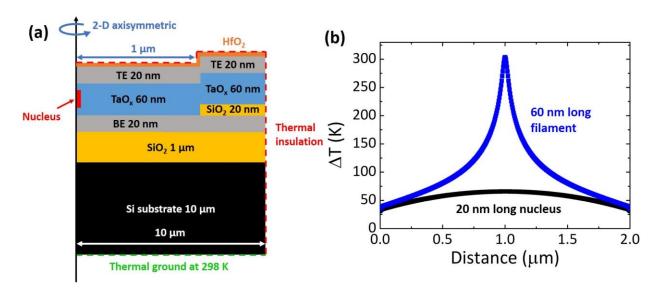

| Figure 3.10 (a) The device structure used in the electrothermal simulation with a nucleation of                                                   |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---|

| conducting phase within the oxide layer. (b) The temperature distribution on the top surface                                                      | ; |

| of the device when the nucleus is 20 nm long (black line) and 60 nm long (blue line) 6                                                            | 8 |

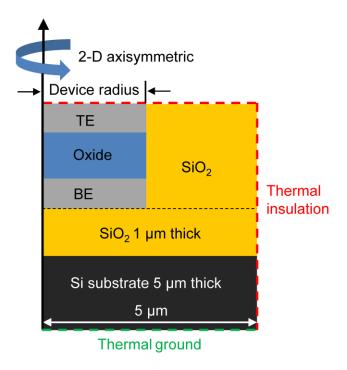

| Figure 4.1 Schematic diagram of a selector structure used in the simulations (note: drawing is                                                    |   |

| not to scale). TE and BE corresponding to top electrode and bottom electrode, respectively.                                                       |   |

|                                                                                                                                                   | 5 |

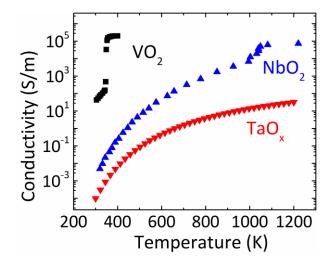

| Figure 4.2 Low field electrical conductivity of VO <sub>2</sub> , NbO <sub>2</sub> , and TaO <sub>x</sub> as a function of                        |   |

| temperature used in this simulation                                                                                                               | 6 |

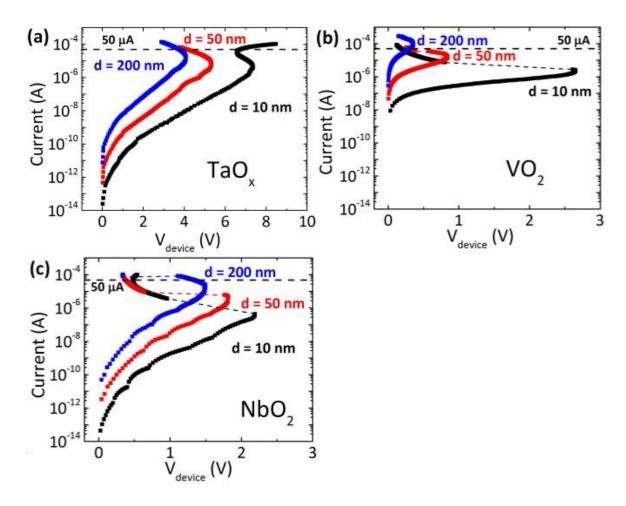

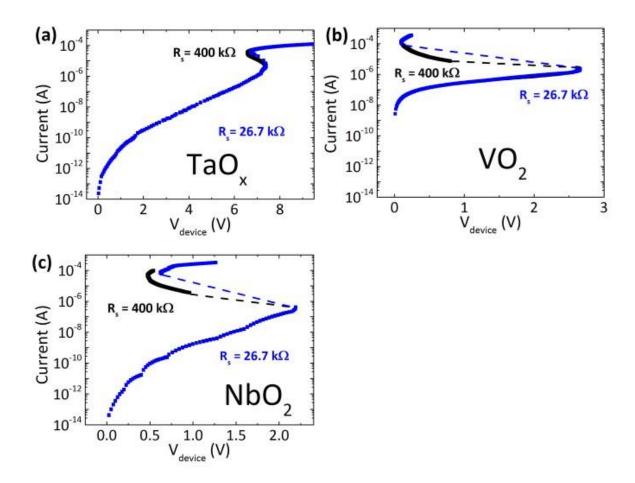

| <b>Figure 4.3</b> <i>I-V</i> characteristics of (a) TaO <sub>x</sub> (b) VO <sub>2</sub> and (c) NbO <sub>2</sub> -based selector devices with 10 |   |

| nm thick functional oxide as a function of device diameter (from 10 nm to 200 nm) 80                                                              | 0 |

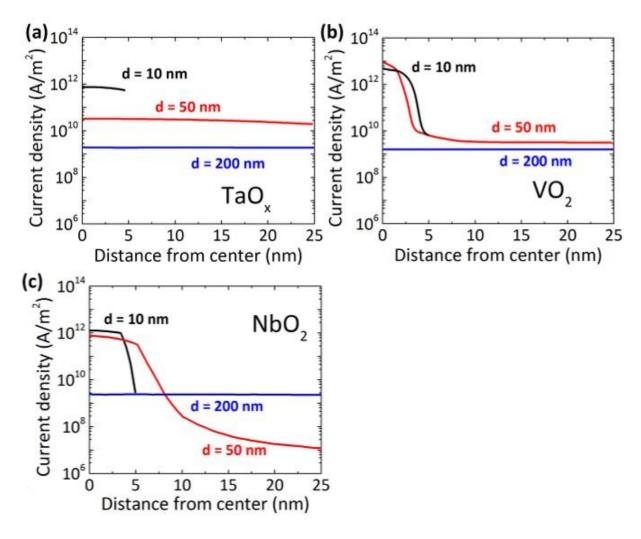

| Figure 4.4 Radial current density profile for (a) TaO <sub>x</sub> , (b) VO <sub>2</sub> and (c) NbO <sub>2</sub> -based selector                 |   |

| devices at 50 µA.                                                                                                                                 | 3 |

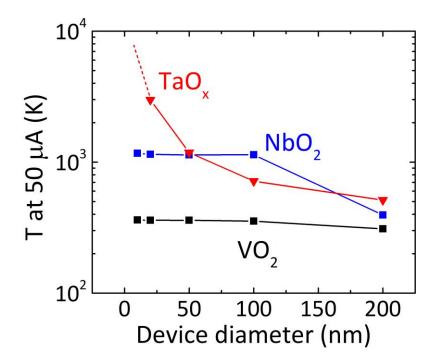

| <b>Figure 4.5</b> The highest temperature within the device at 50 $\mu$ A                                                                         | 5 |

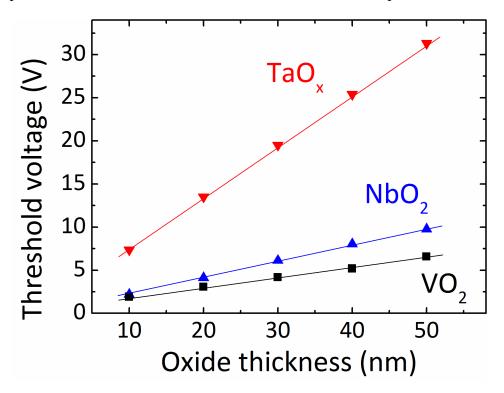

| Figure 4.6 Threshold voltage as a function of oxide layer thickness for three types of selector                                                   |   |

| devices                                                                                                                                           | 6 |

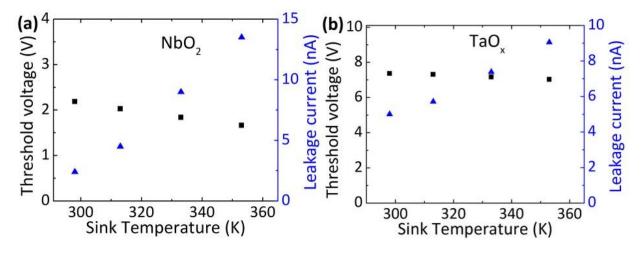

| <b>Figure 4.7</b> The effect of sink temperature on NbO <sub>2</sub> (a) and (b) TaO <sub>x</sub> device characteristics.                         |   |

| Values of simulated threshold voltage are marked by black squares, that of leakage current                                                        |   |

| by blue triangles                                                                                                                                 | 7 |

| Figure 4.8 <i>I-V</i> characteristics of TaO <sub>x</sub> (a), VO <sub>2</sub> (b) and NbO <sub>2</sub> (c) selector devices with load            |   |

| resistance of 400 kO and 26.7 kO.                                                                                                                 | 1 |

## 1 Introduction

## 1.1 Background

The Von Neumann model has been proposed for more than 70 years and it is still an accepted architecture used in modern digital computer. 1 In Von Neumann architecture, the computer consists of four parts: (1) a central processing unit (CPU), including a control unit and an arithmetic logic unit; (2) a memory unit, containing a main memory and an external storage memory (3) an input device and (4) an output device. The memory unit is used to temporarily or permanently store the data and instructions needed to complete tasks, which is an essential part for operating the computer. There is more than one component in the memory unit, forming the memory hierarchy based on the access time of each component, shown in Table 1.1.<sup>2</sup> The cache usually uses static random access memory (SRAM), with a six-transistor per bit cell structure and is located very close to the CPU, having the fastest access time (1-10 CPU cycles) but the smallest capacity due to the low density. The second component in the hierarchy is dynamic random access memory (DRAM), which uses one transistor/one capacitor per bit cell structure. The smaller cell area gives larger capacity than SRAM, but the physically more distant location increases the access time to 10<sup>2</sup> CPU cycles. The DRAM is a volatile memory and requires periodical reading and rewriting the stored data to preserve the information, leading to extra power consumption. The last ring in the hierarchy is the main storage memory consisting of the magnetic hard drive and/or the NAND Flash memory (produced after 2009). The main storage memory is located farthest from CPU, showing the slowest access time (>10<sup>4</sup> CPU cycles) but the highest capacity due to the smallest bit cell area.

**Table 1.1** Memory hierarchy in a computer system.

| CPU Cycles                        | Device | Comment                      |

|-----------------------------------|--------|------------------------------|

| 10 <sup>7</sup> - 10 <sup>8</sup> | Disk   | Nonvolatile, slow and        |

| 10 - 10                           | DISK   | inexpensive                  |

| 10 <sup>4</sup> -10 <sup>6</sup>  | FLASH  | Nonvolatile, fast and        |

|                                   |        | expensive                    |

|                                   | SCM    | Nonvolatile, fast and        |

|                                   |        | inexpensive                  |

| $10^{2}$                          | DRAM   | Volatile, fast and expensive |

| 1-10                              | Cache  | Volatile, fast and expensive |

It is obvious that there is a gap in the current memory hierarchy between DRAM and NAND Flash memory. As the increasing demand on the big data application and faster computation ability, memory devices with high performance, low cost and large storage density are always in need. The storage class memory (SCM) is therefore proposed to fill the gap with a non-volatile memory technology<sup>2,3</sup> that would have faster access time and be less expensive than NAND Flash memory. Another reason to investigate the new memory devices is that both DRAM and NAND Flash memory are charge-based devices,<sup>4</sup> which is approaching the physical scaling limit at 20 nm technology node.<sup>5</sup> The cell-to-cell uniformity and reliability are becoming worse and worse due to the small amount of charge stored in the scaled devices and the cost is increasing due to the difficult patterning process. As a result, a successor of the charge-based memory devices is needed in the near future as the technology node is still shrinking and will become less than 10 nm in 2019.<sup>6</sup>

The emerging non-volatile memory (NVM) technologies such as phase change random access memory (PCRAM),<sup>7</sup> ferroelectric RAM (FeRAM),<sup>8</sup> spin-transfer torque magnetic RAM (STT-

MRAM),<sup>9</sup> and resistive RAM (RRAM)<sup>10</sup> are considered to be promising candidates for SCM application. Among them, the STT-MRAM seems to be a good replacement of DRAM or even SRAM due to its small cell area, fast speed, low programming voltage, and long endurance.<sup>11</sup> RRAM and PCRAM are attractive as the SCM or replacement of NAND Flash memory because of the simple cell structure, short write/read time and lower programing voltage compared to NAND memory devices. <sup>12</sup> The PCM is quite mature today, having good manufacture compatibility with the silicon CMOS technology and Intel has announced the 3DXpoint<sup>TM</sup> product in 2015,<sup>13</sup> which is speculated to be based on phase change materials. However, RRAM devices are still under active research and this study mainly focuses on the selector devices used for RRAM application.

## 1.2 Resistive Random Access Memory

Resistive switching memory is a type of device that can be switched to different resistance states by application of electrical bias. For example, PCRAM is one kind of resistive switch in which the resistance of the chalcogenide material is changed between the crystalline and amorphous states.<sup>7</sup> The RRAM usually employs resistive switching devices with simple two-terminal vertical metal-insulator-metal (MIM) structure. There is a wide range of materials that have been reported to show resistive switching behavior, including metal oxides,<sup>10</sup> nitrides,<sup>14,15</sup> ternary perovskites,<sup>16</sup> and organic materials.<sup>17,18</sup> Among these materials, binary metal oxides have attracted the most interest due to their compatibility with CMOS fabrication process, simple structure and excellent device performance. Here, I will briefly review the metal oxide-based RRAM devices and explain their basic characteristic.

### 1.2.1 Basic operation of RRAM

RRAM stores the information in a form of different resistance states of the insulator layer, normally one high resistance state (HRS) and another low resistance state (LRS). Initially, the RRAM device is in a pristine resistance state after fabrication with a higher resistance than HRS. A one-time "electroforming" (or "forming") process is needed before the device can show repeatable memory switching behavior. The forming process is commonly interpreted as a soft breakdown of the oxide layer and creating a local conductive filament within the oxide layer.<sup>19</sup> The following resistive switching behavior is due to the formation and rupture of the conductive filament that connects the two electrodes. The operation of switching the device from HRS to LRS is called SET, and the operation of switching the device back to HRS is called RESET. The forming step usually requires higher voltage than the switching voltage that follows.

### 1.2.2 Classification of RRAM

According to the switching modes, the RRAM can be categorized into two groups, unipolar switching and bipolar switching. Figure 1.1 shows the typical DC *I-V* characteristic of RRAM devices. For unipolar switching (Figure 1.1a), the device can show memory switching on both polarities of the applied voltage (SET and RESET occur in the same polarity), as long as the voltage is above the switching voltage. On the other hand, for bipolar switching (Figure 1.1b), the SET and RESET occur in different polarities. Usually, the unipolar switching mode occurs in the RRAM with noble metal, such as Pt or Ru, as both top and bottom electrodes.<sup>20, 21</sup> If one electrode is replaced by TiN, Ti or Ta, which are oxidizable materials, the device exhibits bipolar

switching.<sup>22</sup> The switching mode does not simply depend on the properties of oxide material, but the combination of oxide material and the oxide/electrode interfaces.<sup>23</sup>

**Figure 1.1** Typical DC switching *I-V* of RRAM devices. (a) Unipolar switching and (b) bipolar switching. Reprinted from reference [10].

Another categorization of RRAM is based on the type of the mobile ion. The electrochemical metallization mechanism (ECM) relies on the motion of metal cations while valance change mechanism (VCM) relies on the motion of anions. <sup>24</sup> The ECM cell usually consists of an electrochemically active electrode, such as Ag and Cu, and an electrochemically inert counter electrode, such as Pt and W.<sup>25, 26</sup> The switching mechanism of ECM is well understood and is induced by the growth and dissolution of the filament consisting of metal inclusions due to the cation migration under electric field. The metallic filament has been directly observed in TEM by Yang *et al*,<sup>27</sup> and is shown in Figure 1.2. The Ag/SiO2/Pt device was fabricated on an electron transparent 15 nm thick SiN membrane, with a planar device structure instead of crossbar. In this way, authors were able to directly image the device right after fabrication and during electrical testing, without destructive cross-sectional TEM sample preparation. From the TEM images, the

device was in LRS after forming and the filament was connecting the two electrodes (Figure 1.2a). After RESET, a gap was observed between the filament and the Pt electrode (Figure 1.2b). Another point to notice is that there were several partially formed filaments observed in the device, but these filaments did not contribute to the conductivity of the device.

**Figure 1.2** (a) TEM image of SiO<sub>2</sub> based CBRAM after forming. (b) TEM image of the same device in (a) after RESET. Reprinted from reference [27].

For the VCM, the switching mechanism is still under debate due to the wide range of material systems that exhibit resistive switching behavior, therefore, a universal switching mechanism may not exist. A widely accepted model is based on the motion of oxygen vacancies in the electric field and concentration gradient with a local valence change<sup>24, 28, 29</sup> and shown in Figure 1.3. The forming process is thought to be a "soft dielectric breakdown", during which oxygen ions are displaced from their lattice sites at the anode leaving oxygen vacancies behind.<sup>10</sup> If the anode material is a noble metal, the oxygen ions are discharged as neutral nonlattice oxygen, while if it is an oxidizable material, the oxygen ions react and form an interfacial oxide layer. The charged

oxygen vacancies drift under the applied electric field toward the cathode and pile up at the interface of insulator and cathode, creating the local filament. As a result, the filament consists of oxygen-deficient material, which is electrically more conductive than the surrounding region. Therefore, the current only goes through the filament region and the tip of the filament becomes the active cathode. The forming itself is a complex process that has not been well understood. Various techniques have been used to try to image and characterize the filament, <sup>30-35</sup> such as scanning electron microscopy (SEM), transmission electron microscopy (TEM), X-ray energy dispersive spectroscopy (XEDS), conductive atomic force microscopy (CAFM), etc. However, there are still many remaining questions related to the forming, for example, what is the composition of the filament? What is the size and shape of the filament? Is the filament created purely by oxygen leaving lattice sites or by nucleation and growth of another phase within the insulating layer?

The SET process is considered to have the same mechanism with the forming process, the oxygen vacancies drift under electric field toward cathode and the conductive filament fully connects the top electrode and bottom electrode. The difference between SET and forming is that during SET operation, the device has a partially formed filament, while the insulator layer is uniform during forming, requiring a larger voltage than SET. During RESET, the oxygen ions migrate back to the insulator layer to recombine with oxygen vacancies, forming a gap between the filament and electrode, and the device returns to HRS. 36,37

**Figure 1.3** Illustration of the switching process in VCM based RRAM. Reprinted from reference [10].

## 1.3 Crossbar array

## 1.3.1 Array configuration

One of the advantages of the emerging NVM devices is the simple metal-insulator-metal (MIM) cell structure, which allows the architecture of crossbar memory array to achieve a footprint of  $4F^2$ , the smallest possible footprint (F: feature size of a technology node) as shown in Figure 1.4.<sup>38</sup> Crossbar architecture consists of perpendicular word and bit lines (Figure 1.4a), which form the bottom and top electrodes of the NVM devices, and the insulator layer is sandwiched in between at each of the crossing points. By stacking the 2D planar array into n layers of 3D structure, the memory density can be further increased to  $4F^2/n$  shown in Figure 1.4b.

**Figure 1.4** Illustration of (a) 2D cross-point array, and (b) 3D cross-point array. Reprinted from reference [38].

### 1.3.2 Sneak path current

Although the crossbar array is a potential candidate for the high-density memory application, it still suffers from several problems. One of them is the large sneak path current (explained below), where the leakage current is defined as the device current at half of the applied bias. To enable the memory array operation, the memory cell at each intersection of word and bit lines needs to have good selectivity, which is a high non-linearity in the device I-V characteristic. However, most of the reported RRAM and PCM devices have nearly ohmic behavior in both low (LRS) and high resistance states (HRS). Figure 1.5 shows a selected cell in a planar crossbar array and the example of the sneak path.<sup>39</sup> The write operation of the crossbar array is usually using V/2 bias scheme as shown here. In Figure 1.5, device  $R_j$  is selected with  $V_{dd}$  applied to the wordline and 0 V applied to the bitline. All the other unselected wordlines and bitlines are under bias at  $V_{dd}/2$ . Therefore, only  $R_j$  is under bias of  $V_{dd}$ , while the other half-selected devices along the selected wordlines and

bitlines see  $V_{dd}/2$ , and all the rest unselected devices are at zero voltage. The dashed line in black shows the desired current path through  $R_j$ , and the red dotted dash line shows an example of a sneak path consisting of three unselected memory cells ( $R_1$ ,  $R_2$  and  $R_3$ ). In a crossbar array with m wordlines and n bitlines, there are (m-1) × (n-1) possible sneak paths consisting of three unselected cells. The total current goes through the sneak paths could be in the same order of magnitude or much higher than the current going through  $R_j$ , making it difficult to differentiate whether  $R_j$  cell is in HRS or LRS (READ error). Also, due to the line resistance, the sneak path increases the line current and reduces the effective voltage across selected cell, causing an increase of  $V_{dd}$  in order to successfully switch the selected device. The sneak current problem is getting even worse with increasing array sizes due to the possibility of more sneak paths, which limits the size of NVM array.

**Figure 1.5** Illustration of sneak path current in a cross-point array. Reprinted from reference [39].

There are two possible solutions to solve the sneak path current problem. One approach is to use the memory cells with the non-linear *I-V* characteristic, referred to as the self-rectifying cells (SRC) or selector-less memory devices. <sup>40-42</sup> The SRC devices could consist of multiple oxide layers or a tunnel barrier layer as the functional layer to increase the resistance in the HRS and the non-linearity of the device *I-V*. This is a straightforward solution that does not require any changes to the existing crossbar array structure and without extra fabrication steps. However, it is very challenging to find the proper material system that can achieve all the performance requirements for NVM devices, such as long endurance, high cyclability, low cell-to-cell variation, low switching voltage and current, etc.

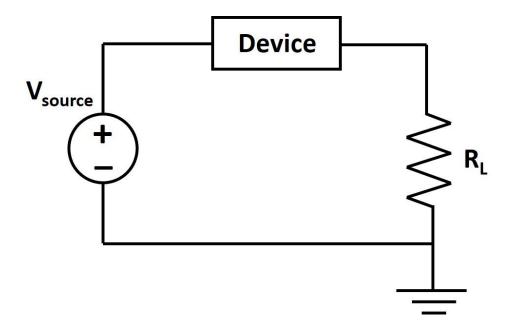

The other solution is to introduce another element with highly non-linear *I-V* characteristic into the memory cell stack, which is called a selector device. In this way, the two-terminal selector is connected in series with the memory cell at each cross point in the memory array forming one selector/one resistor (1S1R) structure. The high resistance of the selector device at low bias greatly suppresses the leakage current of the half-selected memory cells and reduces the sneak path current of the entire crossbar array.

### 1.4 Selector devices

## 1.4.1 General requirements

In order to be considered as a selector device, there are five general requirements that the devices need to meet.

(1) The selector should be a two-terminal device. Generally, the transistor can be used as a selector,

as it exhibits highly nonlinear *I-V* characteristic. The transistors, however, consume a large area with the typical 12F<sup>2</sup> footprint of the one transistor/one resistor cell.<sup>43</sup> In addition, the cost of using transistors is also much higher due to the much more complicated fabrication processes than using simple metal-insulator-metal devices.

- (2) The selector should have highly non-linear *I-V* characteristic. This is the most critical requirement for selector devices. In a memory array, there are many more unselected cells than selected ones, therefore, the selector devices should have a high resistance at low bias in the OFF-state to suppress the leakage current as much as possible, and to achieve acceptable power consumption and circuit performance. The acceptable leakage current decreases with the increasing memory array size. On the other hand, the selector device should drive enough current through the memory cell during SET and RESET operations. For example, to drive the 30 μA RESET switching, <sup>44</sup> the 10 nm diameter selector should have the ON-state current density of 30 MA/cm<sup>2</sup>. The requirement for the ON-state current density depends on the memory cell, therefore, the expected value of non-linearity for the selector device is different for different memory applications, but the ON/OFF current ratio of 10<sup>6</sup> is desired. <sup>45</sup>

- (3) The selector should have the highly non-linear *I-V* in both polarities. As mentioned above in Section 1.2.2, RRAM devices show both unipolar and bipolar switching modes depending on the material systems. However, most of the reported bipolar switching devices have better performance than unipolar devices, in terms of longer endurance, better cycling reliability, and lower switching power. As a result, ideally the selector device should also operate in bipolar mode for RRAM memory applications. Unipolar selector devices, such as diodes, can be used in the

unipolar PCM applications.

- (4) The operation voltage of a selector should be compatible with the memory cell. In the 1S1R cell, the selector device is much more resistive in the OFF-state than the memory cell, and most of the applied voltage drops on the selector device. The switching voltage of the selector devices should enable low leakage current in both half-selected and unselected cells. The critical point in this requirement is the selector device voltage after the switching, as most of the applied voltage falls on the memory cell at this time. The voltage difference of the selector device before and after the switching should be smaller than the SET and RESET voltage of the memory cell. If not, once the selector device switches on, the memory cell would switch immediately, leading to the failure of read operation and undesired switching event. The desired switching voltage of selector devices depends on electrical property of the paired memory cell and it is better that the switching voltage can be tuned by changing the material properties during fabrication, such as film thickness and material composition, in order to accommodate the voltage requirement from memory cell.

- (5) All the other device performance merits should be as good as or better than the memory cell. Since the selector device should not be the component limiting the performance of the entire crossbar array, the device properties should be better than those of the memory cell including reliability, endurance, switching speed, yield, and device-to-device variation. Also, the selector device should use materials that are compatible with traditional CMOS fabrication process. It would be better if the materials are back-end-of-line compatible in order to put the NVM array physically as close to the CPU as possible, meaning maximum fabrication temperature below 400 °C and thermally and electrically stable around 400 °C for 2 hours.<sup>45</sup>

### 1.4.2 Classification of selector devices

Currently, researchers are exploring different types and materials for selector devices, <sup>45-47</sup> such as Si-based PN diodes, <sup>48,49</sup> oxide-based diodes, <sup>50-54</sup> threshold switches <sup>55-58</sup> and Mixed Ionic-Electron Conduction (MIEC). <sup>59</sup> Among these devices, threshold switches are considered as the most promising candidate due to simple structure, CMOS process compatibility, and good electrical performance. Here, I will discuss different types of threshold switching devices.

#### 1.4.2.1 Threshold switches

Threshold switching devices could be ideal for selector application, as the device turns to a highly conductive ON-state from an initially high resistance OFF-state once the threshold voltage or current is reached. Several types of threshold switching devices have been proposed for application as selectors such as ovonic threshold switches, metal-insulator-transition based devices, thermal-runaway induced threshold switches, and Ag-based oxide threshold switches.

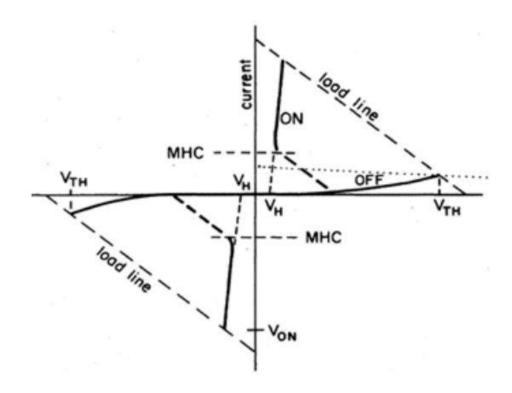

#### a) Ovonic threshold switches

Ovonic threshold switch (OTS) was first reported in thin films of amorphous chalcogenide alloys.<sup>60</sup> A typical *I-V* characteristic of OTS is shown in Figure 1.6.<sup>61</sup> The device is initially in the high resistance OFF-state and switches along the load line corresponding to the resistor connected in series with the selector to the conductive ON-state as soon as the threshold voltage is reached. With the applied voltage ramping down, the device stays in the ON-state until reaching the holding voltage, and the device switches back to the OFF-state when the voltage is further reduced. Unlike

the memory switching behavior in the chalcogenide alloys, there is no permanent conductive filament formed during the threshold switching, therefore the switching is repeatable and nondestructive. The threshold switching occurs after a delay time which can be reduced by increasing applied voltage, and a ~ns switching time can be achieved. 62 Also, the threshold voltage decreases with decreasing functional layer thickness and higher stage temperature, indicating the switching mechanism is electric field dependent. The holding voltage is independent of the thickness and temperature, but it is affected by the electrode materials. 63 Koo et al. reported binary SiTe based OTS selector devices, showing high OFF resistance ( $\sim 20 \text{ G}\Omega$  at 0.2 V), high selectivity (10<sup>6</sup>), fast switching speed (10 ns delay time) and good endurance (> 500k cycles).<sup>64</sup> Alayan et al. integrated a GeSe based OTS with HfO<sub>2</sub>-based RRAM to form 1S1R cell.<sup>65</sup> It showed a selectivity ~20 between V<sub>read</sub> and V<sub>read</sub>/2 and could withstand up to 10<sup>6</sup> reading cycles without any degradation in the 1S1R structure. Further, with the N and Sb doping in the GeSe material, the selectivity was improved to  $\sim 10^5$  due to the formation of Ge-N bonds improving the stability in the OFF-state. Currently, the OTS devices have achieved leakage current of 10<sup>-11</sup> A. ON-state current density of >1.6 MA/cm<sup>2</sup>, selectivity  $>10^6$  with endurance more than  $10^9$  cycles.<sup>66</sup>

One important issue for chalcogenide materials as selector devices is the failure due to crystallization. The same material system can be used as phase change memory devices where the chalcogenide functional layer crystallizes during forming process and stays in ON-state. The crystallization could be prevented by engineering the composition of the chalcogenide alloys.<sup>67</sup>

**Figure 1.6** The typical *I-V* characteristic of ovonic threshold switches. Reprinted from reference [61].

### b) Metal-insulator transition

Metal-insulator transition (MIT) behavior has been reported in many materials and can be induced by various stimuli, such as electric filed, temperature, light and pressure.<sup>68</sup> The electrically and thermoelectrically triggered MIT devices have become potential selector devices because of the simple MIM structure, fast switching speed, and high ON/OFF ratio. Nanoscale Pt/VO<sub>2</sub>/Pt structure can achieve ON/OFF ratio >50, <20 ns switching time, and >1 MA/cm<sup>2</sup> ON-state current density.<sup>55</sup> Zhang *et al.* fabricated W/VO<sub>2</sub>/Pt selector device and externally connected it to a HfO<sub>2</sub>-based RRAM cell. With the integration of VO<sub>2</sub> selector, the RRAM array size can be increased from 8×8 to 128×128.<sup>69</sup> However, the transition temperature of MIT of VO<sub>2</sub> is only 67 °C, making

it not suitable for any applications that can be expected to operate at temperatures above that. Recently, Rupp *et al.* reported that the Cr doped VO<sub>2</sub> can achieve a higher transition temperature than bulk VO<sub>2</sub> and the selector devices showed stable threshold switching behavior up to 90 °C,<sup>70</sup> which provided a method of engineering the material properties.

**Figure 1.7** *I-V* characteristic of W/VO<sub>2</sub>/Pt selector device. Reprinted from reference [69].

NbO<sub>2</sub> is another candidate for MIT threshold switching material, with a much higher transition temperature (1081 K) than VO<sub>2</sub>. The TiN/NbO<sub>2</sub>/W structure which was fabricated by Cha *et al.*<sup>71</sup> showed a >0.1 MA/cm<sup>2</sup> current density, ~500 selectivity and tunable threshold voltage by changing the NbO<sub>2</sub> thickness. Liu *et al.* reported that by inserting an additional Nb<sub>2</sub>O<sub>5</sub> or HfO<sub>2</sub> layer in the MIM structure, the threshold current was further reduced due to thermal confinement in the ON-state.<sup>72</sup> However, the threshold voltage of NbO<sub>2</sub> devices is larger than VO<sub>2</sub> device, and leakage current is still too high to support a large memory array, which needs further engineering

and improvement.

**Figure 1.8** Calculated (a) temperature distributions and (b) *I–V* characteristics for three devices: Pt/NbO<sub>2</sub>/Pt, Pt/NbO<sub>2</sub>/Nb<sub>2</sub>O<sub>5</sub>/Pt and Pt/NbO<sub>2</sub>/HfO<sub>2</sub>/Pt. Reprinted from reference [72].

### c) Field assisted superlinear threshold switches

Jo *et al.* reported a 4Mb 1S1R integration using a Field Assisted Superlinear Threshold (FAST) selector device.  $^{57,73}$  The leakage current was less than 100 pA using 100 nm × 100 nm device. With a selectivity of  $10^{10}$ , the device can drive > 1 mA in the ON state. Also, the device showed sub-50 ns operation speed, >100 M endurance, and less than 300 °C process temperature. The FAST devices show larger selectivity and faster switching speed than OTS and MIT devices, but the actual material used in this selector or a mechanism of operation has not been revealed.

**Figure 1.9** *I-V* characteristic of FAST selector with different thickness of functional layer. Reprinted from reference [57].

#### d) Diffusive memristors

Recently, two groups reported Ag/HfO<sub>x</sub> based threshold switching selector devices.<sup>58, 74</sup> The device showed a leakage current less than 10 pA, high selectivity up to 10<sup>10</sup>, and stable threshold switching up to 90 °C. The switching mechanism is due to migration of the Ag ions under electric field to form a conducting bridge between two electrodes under. HfO<sub>x</sub> is a poor Ag conductor and is unable to hold Ag ions in solution. Once the electric field is removed, the nanoscale Ag filament shrinks and relaxes back to the electrode due to Ostwald ripening.<sup>75</sup> Therefore, this type of devices has similar filament behavior as ECM but exhibits threshold switching. The switching mode can be tuned by the electrode material, as the devices show unipolar switching with only one electrode being Ag, while the device shows bipolar switching with two Ag electrodes. Several Ag/dielectric material systems have shown the threshold switching behavior, such as SiO<sub>2</sub>, <sup>76</sup> MgO<sub>x</sub>, <sup>75</sup> and TiO<sub>2</sub>, <sup>77</sup> but Ag/HfO<sub>x</sub>/Ag based devices showed the best performance.

Figure 1.10 *I-V* characteristic of Ag/HfO<sub>x</sub>/Ag based selector. Reprinted from reference [58].

#### 1.4.2.2 Mixed ionic-electron conduction devices

IBM Research reported Mixed Ionic-Electron Conduction (MIEC) selector<sup>59,78</sup> based on Cucontaining material (more than 50% copper by weight) as the functional layer (the exact composition of the materials has not been revealed), which can conduct both electronic charges and ions. At low voltage, the Schottky barriers are formed at the interface of the MIEC and the electrode, leading to a low leakage current. With the increasing voltage, the Cu ions and vacancies drift within the device, modifying the interface and leading to an increase in current. The selector itself has a switching voltage less than 1V, a leakage current < 10 pA, a large selectivity (> 10<sup>7</sup>), a high ON current density (up to 50 MA/cm²), and >10<sup>8</sup> endurance. The integration of 1S1R structure with PCRAM has also been demonstrated with 35 nm device size.<sup>79</sup> The endurance of

more than 100k cycles was achieved with RESET pulse > 200  $\mu$ A and 5 $\mu$ s long SET pulses at 90  $\mu$ A. The concerns of the MIEC devices are the agglomeration of Cu-rich region leading to the device failure and the much lower threshold voltage than most of the demonstrated memory switching devices.

**Figure 1.11** *I-V* characteristic of MIEC selector. Reprinted from reference [59].

# 1.4.3 Switching mechanism of threshold switches

Since the reporting of threshold switching behavior in 1968,<sup>60</sup> researchers have been trying to understand the mechanism behind the switching in order to not only improve the performance the devices for commercial applications but also to understand the fundamental conduction mechanism of the amorphous semiconductor materials.

Adler et al. proposed the purely electronic induced threshold switching mechanism for amorphous chalcogenide thin films. 61,80 They discarded the thermal induced switching 81 because the temperature predicted by the thermal mechanism was above the glass transition of the chalcogenide materials and this high temperature would lead to gross instability in the devices. This is contrary to the threshold switching enduring up to  $10^{14}$  ON/OFF cycles. In addition, the experimental results based on exchanging n-type and p-type Ge electrode with the same thermal property resulting in different switching characteristic strongly against the thermal model as switching mechanism.<sup>82</sup> Adler et al. argued that the current conduction involved both the electronhole generation depending on the electric field and concentration of free carriers and the Shockley Hall Reed recombination through trap levels. In low fields, most of the generated electron-hole pairs recombine through the traps. When the free carrier generation is greatly enhanced by the electric field and concentration of free carriers, all the traps that close to the band edge are filled and the recombination rate is lower than the generation rate. This, leads to a strong increase of the density of free carriers in the conduction band and an enhanced mobility as well. Therefore, the electrical conductivity of the chalcogenide increases and the device switches to the ON-state. This mechanism can explain both the I-V characteristic of the amorphous chalcogenide-based threshold switches and the delay time observed prior to the switching event in short-pulse measurements.

Ielmini *et al.* developed a model based on trap-limited conduction. <sup>83,84</sup> Amorphous chalcogenide materials have a large concentration of traps in the forbidden gap due to the disordered atomic structure of amorphous material. Therefore, the Fermi level is located in the middle of the energy gap, resulting in a relatively large activation energy and high resistivity. The sub-threshold *I-V* characteristic is described by the Poole-Frenkel conduction mechanism, where the activation

energy is reduced by the applied electric field, enhancing the electron hopping conduction and leading to an exponential increase of the device current. The electric field and temperature effect increase the trap-limited current to a comparable degree, therefore, Ielmini referred to this combined mechanism as thermally assisted hopping. The model can also be extended to the high field region and the following threshold switching event, assuming a nonequilibrium population of shallow traps and resulting in a nonuniform electric field in the negative differential resistance (NDR) region and ON-state. This model can reproduce the device *I-V* in OFF-state, the following NDR, and ON-state regions (Figure 1.12), but it may not be applicable to crystalline materials due to the assumption of a deep Fermi level and large concentration of traps.

**Figure 1.12** Measured and calculated *I-V* characteristic of amorphous Ge<sub>2</sub>Se<sub>2</sub>Te<sub>5</sub> devices. Reprinted from reference [84].

Karpov et al. proposed a field induced nucleation model for chalcogenide-based devices. 85,86 The

energy barrier for the formation of a conductive nucleus (second phase) is lowered by the electric field and accordingly, the critical size of the nucleus is smaller in the presence of the field. The presence of the conducting nucleus in the highly resistive material reduces the electrostatic energy and free energy of the device. In Karpov's model, the nucleation starts with a needle-shaped embryo, which concentrates the electric field and facilitates the growth of nucleus by adding ions at its end. Once the filament fully connects the two electrodes, the threshold switching happens as the device resistance greatly diminishes and the current only flows through the conductive filament. If the electric field is removed before the nucleus reaches the critical size, the filament dissolves and the device switches back into the high resistance OFF-state, showing the threshold switching behavior. The evidence supporting the nucleation model is that it can reproduce the delay time before the switching event in amorphous chalcogenide-based devices, which agrees well with the experimentally measured data at various stage temperatures. Further, the nucleation model was applied to other material systems, such as VO<sub>2</sub>, TaO<sub>x</sub> and NbO<sub>2</sub> based threshold switches and showed agreement with the measured delay times.

**Figure 1.13** The free energy of the nucleus vs its radius for the cases of on and off electric field. Arrows 1 and 2 represent the filament radial growth and decay when the field is off, respectively. Reprinted from reference [86].

Recently, several papers have reported a thermal runaway mechanism for threshold switches based on NbO<sub>2</sub> and TaO<sub>x</sub> devices. 90-93 The model uses Poole-Frenkel formula to describe the electrical conductivity of the oxide material with both the electric field and temperature contributing to the increase of conductivity. With the applied voltage, the current in the device leads to Joule heating and increases the device temperature. The temperature and current forms a positive feedback loop due to the conductivity vs temperature profile, where the increased temperature in turn increases the current. At certain value of the feedback gain, the temperature runs away and the device switches to the ON-state. The model suggests that the threshold switching in NbO<sub>2</sub> based devices is not due to the MIT at 1080 K, as the temperature increase in the devices at switching point is less than 150 K. 90 The evidence of this model is that it can successfully reproduce the device *I-V*

characteristic in OFF-state, NDR region and the ON-state at different stage temperatures as shown in Figure 1.14.

**Figure 1.14** Measured and calculated NbO<sub>2</sub> device *I-V*. Reprinted from reference [90].

# 1.5 Thesis objective and outline

The research on emerging NVMs has been ongoing for more than two decades and ~ns switching,  $\mu$ A programming current, and up to  $10^{12}$  endurance cycles have been demonstrated. However, until now, only PCRAM has been successfully commercialized in the form of 3D XPoint Memory introduced by Intel and Micron, although the actual material used in this technology has not been revealed. The other technologies: RRAM, STT-MRAM, and FeRAM are still in the pre-

commercialization stage. For the case of RRAM, one of the major remaining challenges is the selector device that can fit all the requirements to integrate the 1S1R cell structure in a high-density crossbar array. One of the reasons that the selector device is still missing is that researchers have not fully understood the switching mechanism of the reported threshold switches. Therefore, it is difficult to engineer and optimize the device performance from the fundamental material properties and the design of device structure. This Ph.D. work is focused on the thermal-induced binary metal oxide-based ( $VO_2$  and  $TaO_x$ ) threshold switching devices to shine light on the understanding of the switching mechanism of these devices.

In Chapter 2, an electrothermal finite element model based on Joule heating effect will be presented and is used to simulate the I-V characteristic of two-terminal planar  $VO_2$ -based threshold switches. The  $VO_2$  devices were experimentally tested at various stage temperatures to measure the device I-V and incubation time before the switching event. The comparison between the experimental data and simulation results will be presented, indicating that the thermal effect fully explains the threshold switching in  $VO_2$  devices.

In Chapter 3, the electrothermal model developed in Chapter 2 is applied to TaO<sub>x</sub>-based selector devices to reproduce the device *I-V* characteristic. The direct temperature measurements of TiN/TaO<sub>x</sub>/TiN threshold switches using the Scanning Thermal Microscopy (SThM) and Scanning Joule Expansion Microscopy (SJEM) will be presented. The measured device temperature profile is compared to the electrothermal simulation results, yielding the experimental confirmation of the thermal runaway model as the mechanism of the threshold switching in TaO<sub>x</sub>-based devices.

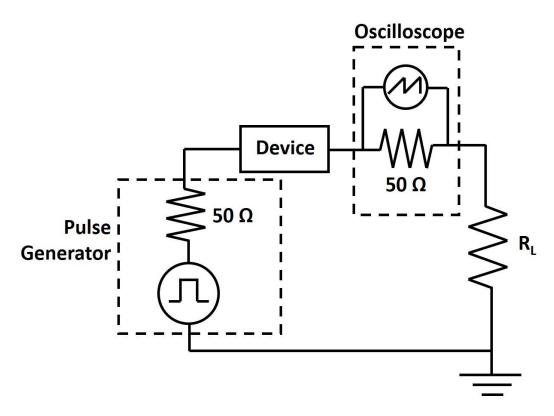

In Chapter 4, based on the understanding of the switching mechanism of VO<sub>2</sub> and TaO<sub>x</sub>-based threshold switches discussed in the previous two chapters, a comprehensive scaling study on VO<sub>2</sub>, TaO<sub>x</sub> and NbO<sub>2</sub> (already reported to have thermal-induced threshold switching) based selector devices using the electrothermal model will be presented. The size of the vertical metal-insulator-metal device structure is scaled down to 10 nm in diameter and the device performance, such as device *I-V*, current density, and temperature in the ON-state as a function of device diameter and oxide thickness are extracted from the simulations. Further, a benchmarking analysis of these scaled devices connected to a generic phase change-like memory element forming 1S1R cell structure is discussed. In the end, the ideal material properties for selector application is calculated.

Chapter 5 will summarize the main results, list the main contributions, and discuss the possible future work based on the understanding from this work.

# 2 Electrothermal model of threshold switching of VO<sub>2</sub>-based devices

### 2.1 Introduction

Vanadium dioxide (VO<sub>2</sub>) undergoes an insulator-to-metal transition (IMT) at 68 °C <sup>94</sup> corresponding with a structural phase transition from an insulating monoclinic phase to a metallic tetragonal phase. <sup>95</sup> At the transition point, the electrical resistivity of VO<sub>2</sub> changes by several orders of magnitude, making it a potential candidate for many transformative applications, such as threshold switching devices, <sup>55,96,97</sup> field effect transistors, <sup>98,99</sup> and oscillators. <sup>100-102</sup> In two terminal devices, IMT materials show a threshold switching behavior when the voltage across it exceeds a certain 'threshold' value. At this point, the resistance of the device decreases by several orders of magnitude and remains low as long as the voltage exceeds another value  $V_{HOLD}$  referred to as the "holding voltage". <sup>103</sup> At biases below  $V_{HOLD}$ , the device returns to its initial high resistance state, as shown in Figure 2.1. <sup>104</sup>

**Figure 2.1** *I-V* characteristic of VO<sub>2</sub> devices. Reprinted from reference [104].

It has been a long-standing question whether the transition from an insulator to a metal that is responsible for the resistance change is caused by the increase of the temperature above the transition point due to Joule heating, or by other effects. The difference is an important one from the point of view of applications: the electric field or carrier injection-based mechanism could open a wide range of possible ultrafast device applications.

The arguments for Joule heating-induced transition were based on DC bias or low frequency pulse measurements. Mun  $et\ al.^{105}$  measured the threshold voltage at different stage temperatures and argued that the dependence agrees with the Joule heating effect. Radu  $et\ al.^{106}$  measured the threshold voltage values as a function of electrode separation and power necessary to switch the structure to the ON-state and found that both change in agreement with the thermal model. Lee et

$al.^{107}$  applied low frequency triangular pulses to lateral structures and measured the dependence of the threshold voltage ( $V_{TH}$ ) and  $V_{HOLD}$  as a function of frequency, load resistor, and stage temperature, also obtaining good agreement with the Joule heating model. The most direct argument was presented by Zimmers  $et\,al.^{108}$  who measured the temperature of the functional layer during quasi-DC voltage sweep by monitoring the fluorescence of micron size particles deposited on the VO<sub>2</sub> layer. The temperature in all cases corresponded to the transition temperature of the IMT when the resistance drop was observed.

The evidence in support of the non-thermally induced transition ranges from simulations of the temperature distribution in devices under DC bias, which show that the device could not reach the transition temperature, 109,110 to ultrafast voltage or light pulse experiments which monitored the delay time for the transition. All fast pulse experiments indicated that the transition occurred before the device could reach the transition temperature. 96,111-113 Two groups argued that the switching time 114 or power necessary for switching 115 are independent of stage temperature which is in clear contradiction with the thermally induced transition. Concomitantly, others have produced evidence of IMT being due to carrier injection from electrodes, 116,117 by photoexcitation 118,119 or by avalanching. 120-122

In this Chapter, an electrothermal finite element model based on Joule heating effect is presented. Using VO<sub>2</sub> as a model material, the simulation results on the threshold switching device behavior is compared with the experimental data to investigate the mechanism of threshold switching in VO<sub>2</sub>-based devices.

#### 2.2 Two-terminal VO<sub>2</sub>-based devices

The two-terminal VO<sub>2</sub>-based threshold switching devices were provided by Prof. Schlom's group at Cornell University and Prof. Datta's group at University of Notre Dame.

10 nm-thick VO<sub>2</sub> thin films used in this work were grown on TiO<sub>2</sub> (001) substrates by reactive molecular-beam epitaxy in a Veeco GEN10 system. <sup>123</sup> The layer thickness was less than the critical thickness (30 nm) and films were fully strained. The two-terminal devices were fabricated with 20 nm thick Pd/80 nm thick Au metal stack electrodes and a 6  $\mu$ m (length) by 10  $\mu$ m (width) VO<sub>2</sub> channel. <sup>124</sup> A plan view SEM image of the device is shown in Figure 2.2a. The devices were tested using a variable temperature Lakeshore cryogenic probe station with a 5.5 k $\Omega$  load resistor in series during DC and pulse measurements. Figure 2.2b shows the electrical conductivity of the VO<sub>2</sub> film as a function of stage temperature measured at 0.1 V applied voltage. The transition temperature was determined to be 272 K, lower than the normal transition temperature because of the biaxial in-plane tensile strain effect. <sup>123</sup> The device characteristics showed some variation across the wafer with the resistances varying by up to a factor of two and the transition temperature changing by less than 2 degrees.

**Figure 2.2** (a) SEM image showing VO<sub>2</sub> device layout and (b) plot of the electrical conductivity of VO<sub>2</sub> as a function of stage temperature. The black and red lines are, respectively, the heating and cooling curves for the conductivity.

# 2.3 Modeling methodology

The finite element simulation of the device I-V characteristic was performed using the COMSOL Multiphysics package. The 3-dimensional device geometry used in the simulation is shown in Figure 2.3. The  $TiO_2$  substrate used in the model has a size of 750  $\mu$ m length, 500  $\mu$ m width and 900  $\mu$ m thickness (actual thickness of the substrate), in order to reproduce the thermal environment of the chip. The size of the substrate is an important parameter in the simulation model, as a small substrate would produce a different thermal resistance than the real chip, leading to a different temperature increase of the device under bias. The substrate size was chosen by conducting a series of simulations with the same applied voltage but different substrate sizes to calculate the steady-state temperature of the  $VO_2$  device. The simulation results suggested that a substrate of 500  $\mu$ m

$\times$  500  $\mu m$  area with the 900  $\mu m$  thickness is large enough to mimic the thermal environment of the real chip.

**Figure 2.3** VO<sub>2</sub> device geometry used in the simulation model. Left: the entire device geometry, with the TiO<sub>2</sub> substrate of 750 μm length, 500 μm width and 900 μm thickness. Right: plan view of the top of the geometry.

To fully reproduce the experimental measurement setup, the electrical circuit model including a load resistor is coupled with the Joule heating physics model. The input parameters of the simulation are the 3-D device geometry, materials properties (thermal conductivity, material density, specific heat, electrical conductivity) for  $VO_2$ , as well as the electrodes and the substrate materials, the experimental applied voltage, the resistance of the load resistor (5.5 k $\Omega$ ) and the stage temperature. The values of material properties are listed in Table 2.1.

**Table 2.1** The material properties used in the simulation of VO<sub>2</sub>-based devices.

| Material         | Density (kg·m <sup>-3</sup> ) | Thermal conductivity $(W \cdot m^{-1} \cdot K^{-1})$ | Electrical conductivity (S·m <sup>-1</sup> ) | Heat capacity $(J \cdot kg^{-1} \cdot K^{-1})$ | Relative permittivity |

|------------------|-------------------------------|------------------------------------------------------|----------------------------------------------|------------------------------------------------|-----------------------|

| Au               | 19300                         | 317                                                  | $4.56 \times 10^7$                           | 129                                            | 6.9                   |

| $VO_2$           | 4340                          | Insulating phase: 3.5 Metallic phase: $6^{[125]}$    | Measured<br>data                             | 690                                            | 36 <sup>[126]</sup>   |

| TiO <sub>2</sub> | 4230                          | 8                                                    | N/A                                          | 691                                            | 50                    |

The COMSOL Multiphysics package solves two coupled differential equations. The temperature distribution T(x, y, z, t) in the device is the solution of the heat flow equation:

$$\rho C_p \frac{\partial T(x, y, z, t)}{\partial t} - \kappa \Delta T(x, y, z, t) = \frac{J^2(x, y, z, t)}{\sigma(T)}$$

(2.1)