# Power/Performance Modeling and Optimization: Using and Characterizing Machine Learning Applications

Submitted in partial fulfillment of the requirements for

the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

#### Ermao Cai

B.S., Applied Physics, Shanghai Jiao Tong University

Carnegie Mellon University Pittsburgh, PA

May 2018

© 2018 Ermao Cai. All rights reserved.

#### Acknowledgements

The pursuit of PhD during the past five years has been a fruitful adventure for me, not only in my academic, but also in my personal life. I could not have achieved so much without the support from these resourceful, sincere, and brilliant people.

First and foremost, I would like to thank my advisor, Prof. Diana Marculescu. It has been an honor to have such a caring mentor, dedicated researcher, and a knowledgeable instructor to lead me over the years. When Diana first brought me to the research world, I had little experience and almost no engineering background. She trusted me, helped me, and created an unconstrained environment for me to explore and develop as a researcher. Her guidance and support made me more precise, more profound, and more creative. I sincerely hope when Diana looks back, she will think of taking me in as a right decision.

I would like to thank my committee member and collaborator, Dr. Da-Cheng Juan. Da-Cheng has set an example of excellence for a Ph.D. student. For the past five years, he not only has offered me helpful advice on tackling research problems and exploring ideas, but also has shown me how to enjoy research and life at the same time.

I would like to thank Prof. Radu Marculescu and Prof. Shawn Blanton for being my thesis committee members and providing invaluable guidance and feedback through this process.

I would like to thank my fellow researchers and collaborators: Mr. Dimitrios Stamoulis, Prof. Aarti Singh, Dr. Jinpyo Park, and Prof. Siddharth Garg for their great work, thoughts and ideas.

I would also like to thank my internship mentor: Dr. Florentin Dartu, for instructing me to solve real industrial challenges with my research skills.

My days at CMU were made enjoyable in large part due to the many friends and groups that became a part of my life. They are:

Mr. Guangshuo Liu, Mr. Zhuo Chen, Mr. Ruizhou Ding, Mr. Ting-Wu Chin, and Mr. Ahmet Fatih Inci, from EnyAC;

Mr. Bolun Li, Mr. Minghao Ruan, Dr. Sanxi Yao, Dr. Huang-Kai Peng, Dr. Renzhi Liu, and Mr. Xi He.

I would like to acknowledge the funding support received from Samsung Electronics, National Science Foundation (including Grants CCF-1314876, CCF-1514206, CNS-1128624, CNS-1331804, and CNS-1564022), and Carnegie Mellon University that has made pursuing my research possible.

Lastly, I would like to thank my family for all their love and support: my parents and my brother who have supported me in all my pursuits. And most of all, my loving and encouraging fiancée - I could not have done this without her.

#### **Abstract**

Energy and power are the main design constraints for modern high-performance computing systems. Indeed, energy efficiency plays a critical role in performance improvement or energy saving for either state-of-the-art general purpose hardware platforms, such as FinFET-based multi-core systems, or widely-adopted applications such as deep learning applications and in particular, convolutional neural networks. To achieve higher energy efficiency, power and performance models are key in enabling various predictive management algorithms or optimization techniques. To have accurate models, one needs to consider not only technology-related effects, including process variation, temperature effect inversion, and aging, but also application-related effects, such as the interaction between applications with software and hardware layers.

In this thesis, we study these effects and propose to combine machine learning techniques and domain knowledge to learn the performance, power, and energy models for high-performance computing systems. For technology-aware multi-core system design, we learn accurate performance and power models for FinFET-based multi-core systems considering various technology effects. By applying these models, we propose efficient power-performance-related management algorithms for multi-core systems to 1) increase performance under iso-power constraints; 2) reduce power while keeping the same performance; and 3) decrease aging effects with negligible power overhead for the same performance. For application-aware computing system design, we propose a hierarchical framework based on sparse polynomial regression to predict the serving power, runtime, and energy consumption of deep learning applications, including convolutional neural networks. Extensive experimental results confirm the effectiveness of our proposed models, algorithms, and framework.

# Contents

| $\mathbf{C}$ | ontents |                                                   |     |  |

|--------------|---------|---------------------------------------------------|-----|--|

| Li           | st of   | Tables                                            | Х   |  |

| Li           | st of   | Figures                                           | xii |  |

| 1            | Inti    | roduction                                         | 1   |  |

|              | 1.1     | Challenges                                        | 2   |  |

|              | 1.2     | Thesis contributions                              | 3   |  |

|              | 1.3     | Thesis organization                               | 5   |  |

| <b>2</b>     | Bac     | ekground                                          | 6   |  |

|              | 2.1     | Technology-aware computing system design          | 6   |  |

|              | 2.2     | Application-driven computing system design        | 9   |  |

| 3            | Lea     | rning for many-core system optimization           | 11  |  |

|              | 3.1     | Chapter overview                                  | 11  |  |

|              |         | 3.1.1 Chapter contributions                       | 12  |  |

|              | 3.2     | Power model and performance metrics               | 13  |  |

|              | 3.3     | Model learning process                            | 14  |  |

|              |         | 3.3.1 Learning the frequency-power relationship   | 15  |  |

|              |         | 3.3.2 Learning the utilization-power relationship | 18  |  |

|              |         | 3 3 3 Model validation                            | 20  |  |

CONTENTS vii

|   | 3.4 | Constrained optimization |                                            |    |

|---|-----|--------------------------|--------------------------------------------|----|

|   |     | 3.4.1                    | Constrained energy minimization            | 21 |

|   |     | 3.4.2                    | Constrained throughput maximization        | 22 |

|   | 3.5 | Imple                    | mentation flow                             | 23 |

|   | 3.6 | Exper                    | imental results                            | 24 |

|   |     | 3.6.1                    | Iso-performance energy optimization        | 24 |

|   |     | 3.6.2                    | Iso-power performance optimization         | 26 |

|   |     | 3.6.3                    | Impact of discrete V/F levels              | 28 |

|   |     | 3.6.4                    | Impact of core cluster size                | 29 |

|   |     | 3.6.5                    | Comparisons of bulk CMOS and FinFET        | 30 |

|   |     | 3.6.6                    | Effects of core count in FinFET CMPs       | 31 |

|   | 3.7 | Discus                   | ssion                                      | 32 |

| 4 | Ten | nerat                    | ure effect inversion in multi-core systems | 34 |

|   | 4.1 |                          | ser overview                               | 34 |

|   | 4.1 | 4.1.1                    | Chapter contributions                      | 35 |

|   | 4.2 |                          |                                            |    |

|   | 4.2 |                          | rmance and power models for TEI analysis   | 37 |

|   |     | 4.2.1                    | Performance                                | 37 |

|   |     | 4.2.2                    | Dynamic power                              | 37 |

|   |     | 4.2.3                    | Static power                               | 38 |

|   | 4.3 | Optim                    | nization methodology                       | 40 |

|   |     | 4.3.1                    | Temperature-dependent V/F pairs            | 40 |

|   |     | 4.3.2                    | TEI-induced sweet spots                    | 42 |

|   |     | 4.3.3                    | Efficient TEI-aware V/F scaling            | 44 |

|   |     |                          |                                            |    |

|   |     | 4.3.4                    | Complexity analysis                        | 48 |

|   | 4.4 |                          | Complexity analysis                        | 48 |

|   | 4.4 |                          |                                            |    |

CONTENTS viii

|   |     | 4.4.3  | Evaluation of TEI-aware algorithms                | 54 |

|---|-----|--------|---------------------------------------------------|----|

|   |     | 4.4.4  | Scalability of TEI-Turbo algorithm                | 59 |

|   |     | 4.4.5  | Scalability of TEI-LP algorithm                   | 61 |

|   | 4.5 | Discus | ssion                                             | 63 |

| 5 | Agi | ng-red | uction in multi-core systems                      | 65 |

|   | 5.1 | Chapt  | er overview                                       | 65 |

|   |     | 5.1.1  | Chapter contributions                             | 66 |

|   | 5.2 | Perfor | mance and power models                            | 67 |

|   |     | 5.2.1  | Introducing TEI- and aging-awareness              | 67 |

|   |     | 5.2.2  | Power and performance metrics                     | 68 |

|   | 5.3 | Multi- | objective optimization                            | 70 |

|   |     | 5.3.1  | Thermal, aging and power considerations           | 70 |

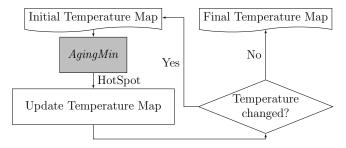

|   |     | 5.3.2  | Proposed approach: AgingMin                       | 72 |

|   |     | 5.3.3  | Accounting for thermal effects                    | 74 |

|   | 5.4 | Exper  | imental results                                   | 74 |

|   |     | 5.4.1  | Experimental setup                                | 75 |

|   |     | 5.4.2  | TEI effect on aging                               | 76 |

|   |     | 5.4.3  | Evaluation of AgingMin                            | 79 |

|   | 5.5 | Discus | ssion                                             | 80 |

| 6 | Con | voluti | onal neural network: power and latency            | 82 |

|   | 6.1 | Chapt  | er overview                                       | 82 |

|   |     | 6.1.1  | Chapter contributions                             | 83 |

|   | 6.2 | Power  | and runtime modeling                              | 84 |

|   |     | 6.2.1  | Layer-level power and runtime modeling            | 84 |

|   |     | 6.2.2  | Network-level power, runtime, and energy modeling | 87 |

|   |     | 6.2.3  | Dataset collection                                | 87 |

|   | 6.3 | Exper  | imental results                                   | 80 |

| CONTENTS | ix |

|----------|----|

|----------|----|

|                           |       | 6.3.1   | Layer-level model evaluation                                             | 89  |

|---------------------------|-------|---------|--------------------------------------------------------------------------|-----|

|                           |       | 6.3.2   | Network-level model evaluation                                           | 92  |

|                           |       | 6.3.3   | Energy-precision ratio                                                   | 97  |

|                           |       | 6.3.4   | Models on other platforms and development frameworks $\ \ldots \ \ldots$ | 98  |

|                           | 6.4   | Discus  | ssion                                                                    | 102 |

| 7                         | Rel   | ated w  | rork                                                                     | 103 |

| 8                         | Cor   | nclusio | n and future work                                                        | 107 |

| $\mathbf{B}_{\mathbf{i}}$ | bliog | graphy  |                                                                          | 110 |

# List of Tables

| 3.1 | Target architecture                                                               | 19 |

|-----|-----------------------------------------------------------------------------------|----|

| 3.2 | Validation error of the learned $\hat{P}$                                         | 20 |

| 4.1 | Validation error of the learned dynamic power                                     | 38 |

| 4.2 | Learning leakage power model                                                      | 40 |

| 4.3 | Learning temperature-dependent V/F pairs                                          | 41 |

| 4.4 | V/F levels for worst case (-25 °C)                                                | 41 |

| 4.5 | Target architecture                                                               | 49 |

| 5.1 | Target architecture                                                               | 75 |

| 5.2 | V/F level matching for $\theta$ =-25°C                                            | 75 |

| 6.1 | Target platform                                                                   | 88 |

| 6.2 | Comparison of runtime models for common CNN layers – Our proposed runtime         |    |

|     | model consistently outperforms the state-of-the-art runtime model in both root-   |    |

|     | mean-square-error (RMSE) and the Root-Mean-Square-Percentage-Error (RM-           |    |

|     | SPE)                                                                              | 90 |

| 6.3 | Power model for common CNN layers                                                 | 92 |

| 6.4 | Performance model comparison for the whole network. We can easily observe that    |    |

|     | our model always provides more accurate predictions of the total CNN runtime      |    |

|     | compared to the best published model to date (Paleo). We assess the effectiveness |    |

|     | of our model in five different state-of-the-art CNN architectures                 | 94 |

List of Tables xi

| 6.5  | Evaluating our power predictions for state-of-the-art CNN architectures                           | 96  |

|------|---------------------------------------------------------------------------------------------------|-----|

| 6.6  | Evaluating our energy predictions for state-of-the-art CNN architectures                          | 97  |

| 6.7  | EPR metric for different CNN architectures and Energy-per-Image (EPI) values.                     |     |

|      | Network choices could be different for different $\alpha$ values: Alex<br>Net for $\alpha=1,2,3,$ |     |

|      | VGG-16 for $\alpha = 4$                                                                           | 98  |

| 6.8  | Runtime and power model for all layers using TensorFlow on GTX 1070                               | 99  |

| 6.9  | Evaluation of $NeuralPower$ on CNN architectures using TensorFlow on GTX 1070.                    | 99  |

| 6.10 | Runtime and power model for all layers using Caffe on GTX 1070                                    | 100 |

| 6.11 | Evaluation of our model on CNN architectures using Caffe on GTX 1070 1                            | 100 |

| 6.12 | Runtime and power model for all layers using TensorFlow on Jetson TX1 1                           | 101 |

| 6.13 | Evaluation of NeuralPower on CNN architectures using TensorFlow on Jetson                         |     |

|      | TX1                                                                                               | 101 |

# List of Figures

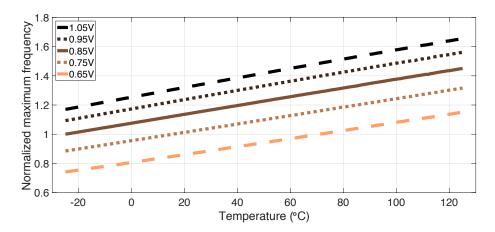

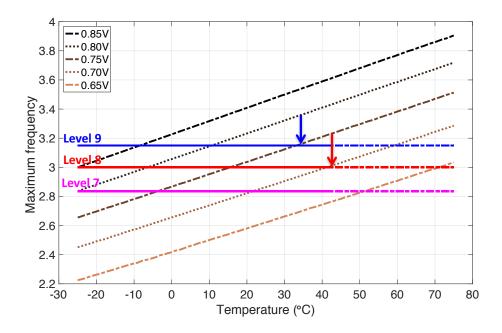

| 2.1 | Maximum operating frequency under a wide range of temperature values for        |    |

|-----|---------------------------------------------------------------------------------|----|

|     | FinFET                                                                          | 8  |

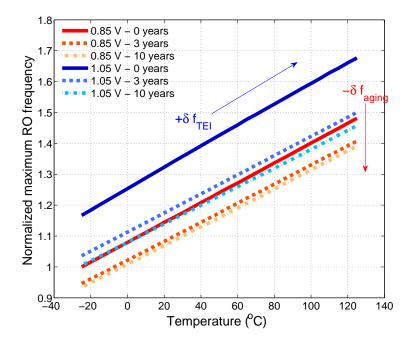

| 2.2 | Maximum operating RO frequency under the impact of TEI and aging                | S  |

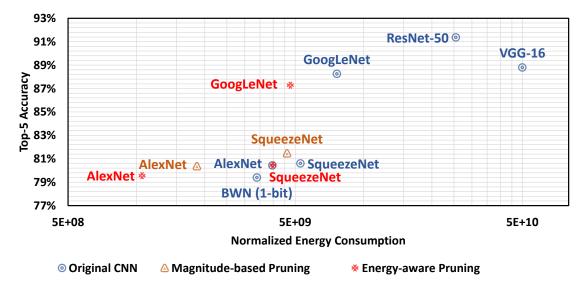

| 2.3 | Prediction accuracy versus energy consumption of popular CNN models. This       |    |

|     | figure is adopted from [91]. Some models are pruned with either magnitude-based |    |

|     | pruning [29] or energy-aware pruning [91]. For the architectures that achieve   |    |

|     | similar accuracy levels during test phase, the energy consumption can vary by   |    |

|     | close to $10\times$                                                             | 10 |

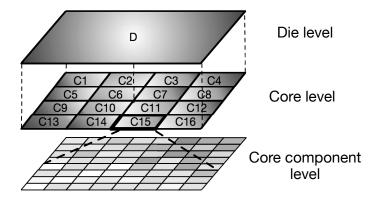

| 3.1 | Hierarchical grid-based modeling of process variations for a CMP die with 16    |    |

|     | cores. Different grey levels represent different PV values. The PV pattern used |    |

|     | here is only for illustration                                                   | 15 |

| 3.2 | Maximum frequency, dynamic power and static power with respect to process       |    |

|     | variations. All three PV parameters have a significant impact on static power.  |    |

|     | They also affect delay and dynamic power across a wide range of operating fre-  |    |

|     | quency                                                                          | 17 |

| 3.3 | Implementation flow for the proposed framework                                  | 23 |

List of Figures xiii

| 3.4 | Average energy minimization results across 10 variation maps under 100% and                   |    |

|-----|-----------------------------------------------------------------------------------------------|----|

|     | 90% throughput constraints. <b>Top</b> : $3\sigma$ (standard deviation) of process parameters |    |

|     | is $10\%$ of their nominal values. PV-ExDVFS achieves the lowest energy points,               |    |

|     | the average reduction compared with the baseline approach is $22.88\%$ for $100\%$            |    |

|     | throughput (hard) constraint and 47.13% for 90% throughput (soft) constraint.                 |    |

|     | <b>Bottom</b> : $3\sigma$ is 30%. The corresponding energy reduction of PV-ExDVFS is          |    |

|     | 31.09% for hard constraint and $59.59%$ for soft constraint                                   | 25 |

| 3.5 | Average throughput improvement results across 10 variation maps with $100\%$                  |    |

|     | and 110% power budgets. <b>Top</b> : $3\sigma$ (standard deviation) of process parameters     |    |

|     | is $10\%$ of their nominal values. PV-ExDVFS achieves the highest throughput                  |    |

|     | points, the average improvement compared with the baseline approach is $6.25\%$               |    |

|     | for $100\%$ power (hard) budget and $6.93\%$ for $90\%$ power (soft) budget. <b>Bottom</b> :  |    |

|     | $3\sigma$ is 30%. The corresponding throughput improvement of PV-ExDVFS is $11.46\%$          |    |

|     | for hard constraint and 18.17% for soft constraint                                            | 27 |

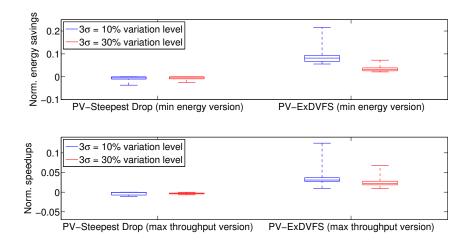

| 3.6 | Energy savings (top) and speedups (bottom) for PV-Steepest Drop [88] and PV-                  |    |

|     | ExDVFS compared with the baseline PV-MaxBIPS [40] i.e., exhaustive search                     |    |

|     | of best energy (top) and performance (bottom) configuration                                   | 29 |

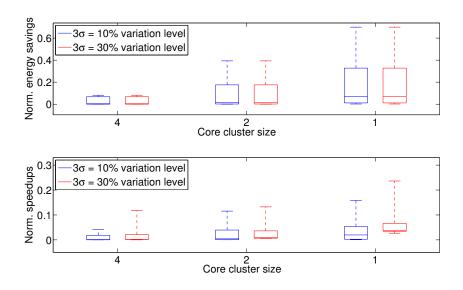

| 3.7 | Energy savings (top) and speedups (bottom) for PV-ExDVFS with different core                  |    |

|     | cluster sizes compared with the baseline (PV-ExDVFS with chip-wise V/F domain).               | 30 |

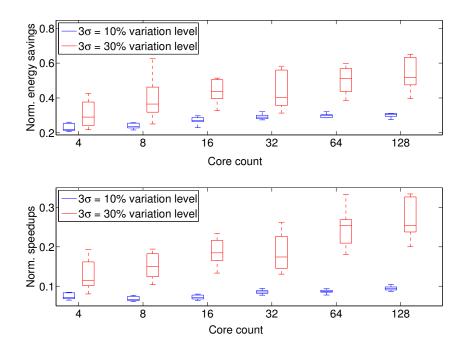

| 3.8 | Energy saving and speedup further improve as number of cores and PV level                     |    |

|     | increase. <b>Top</b> : energy savings under $100\%$ throughput constraint in mild $(10\%)$    |    |

|     | and extreme (30%) PV levels. Bottom: Speedups with $100\%$ power budget in                    |    |

|     | mild and extreme PV levels                                                                    | 31 |

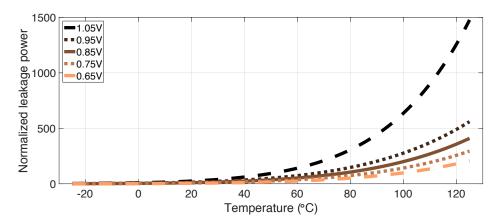

| 4.1 | Normalized leakage power under a wide range of temperature values for FinFET.                 | 39 |

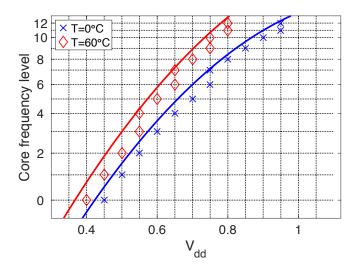

| 4.2 | Dynamic voltage frequency pairings for different temperatures                                 | 42 |

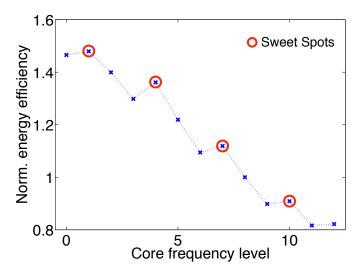

| 4.3 | Normalized energy efficiency across all frequency levels                                      | 43 |

| 4.4 | Example process of determining sweet spots.                                                   | 44 |

List of Figures xiv

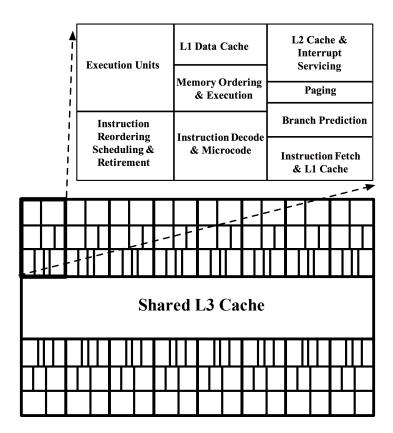

| 4.5  | Simplified floorplan for a 16-core nehalem-like [2] chip-multiprocessor with only              |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | cores and L3 cache                                                                             | 50 |

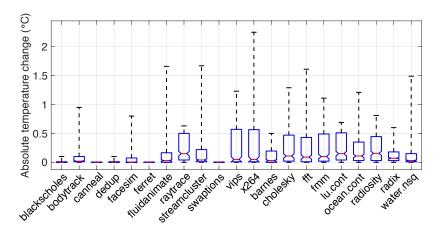

| 4.6  | The absolute temperature changes for each core during one control epoch (1 ms)                 |    |

|      | for different benchmarks                                                                       | 51 |

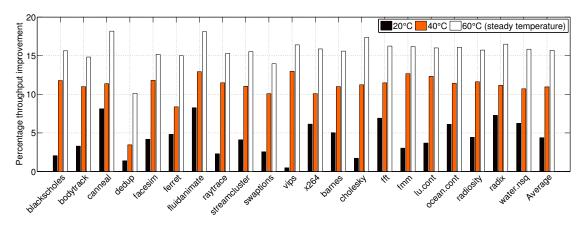

| 4.7  | Normalized throughput improvement of TEI-aware Steepest Drop algorithm over                    |    |

|      | TEI-unaware version                                                                            | 52 |

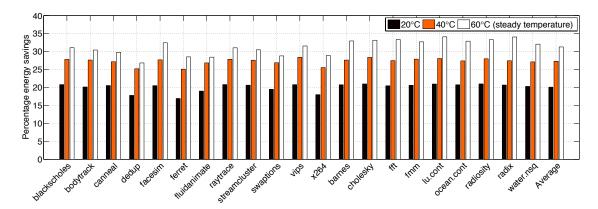

| 4.8  | Normalized energy saving of TEI-aware Steepest Rise algorithm over TEI-unaware                 |    |

|      | version                                                                                        | 53 |

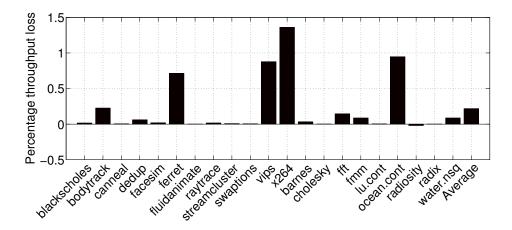

| 4.9  | Relative throughput loss of TEI-Turbo compared with TEI-aware Steepest Drop.                   | 54 |

| 4.10 | Relative runtime speedup of TEI-Turbo over TEI-aware Steepest Drop                             | 55 |

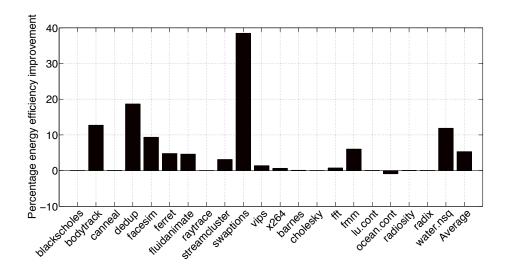

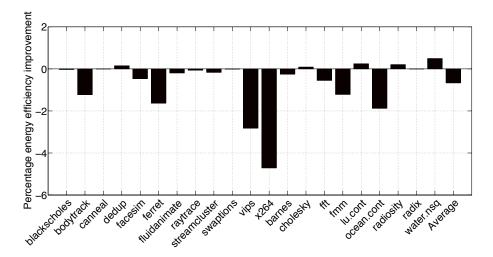

| 4.11 | Energy efficiency improvement of TEI-Turbo over TEI-aware Steepest Drop                        | 56 |

| 4.12 | Relative energy consumption for TEI-LP compared with TEI-aware Steepest Rise.                  | 57 |

| 4.13 | Relative runtime speedup of TEI-LP over TEI-aware Steepest Rise                                | 58 |

| 4.14 | Energy efficiency improvement of TEI-LP over TEI-aware Steepest Rise                           | 59 |

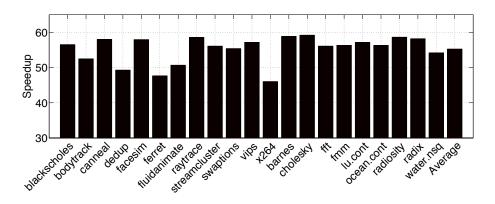

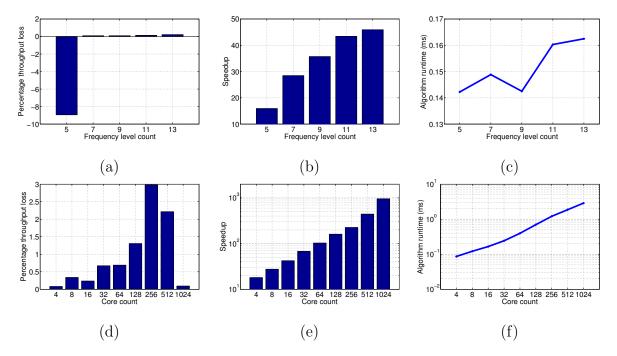

| 4.15 | Scalability of TEI-Turbo compared with TEI-aware steepest drop: (a) Through-                   |    |

|      | put loss with respect to frequency level count; (b) Speedup with respect to fre-               |    |

|      | quency level count; (c) Runtime of TEI-Turbo with respect to frequency level                   |    |

|      | count; (d) Throughput loss with respect to core count; (e) Speedup with respect                |    |

|      | to core count; (f) Runtime of TEI-Turbo with respect to core count                             | 60 |

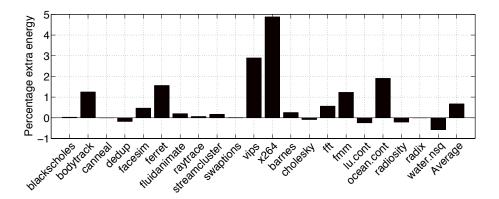

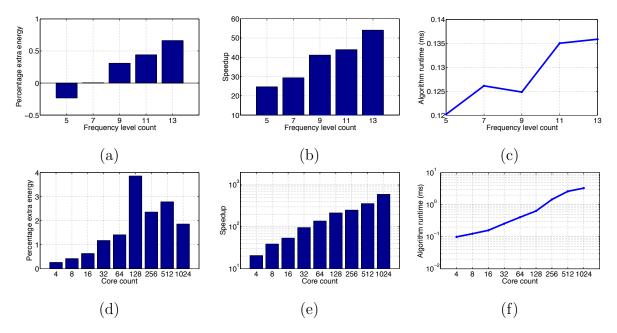

| 4.16 | Scalability of TEI-LP compared with TEI-aware steepest rise: (a) Extra energy                  |    |

|      | consumption with respect to frequency level count; (b) Speedup with respect to                 |    |

|      | frequency level count; (c) Runtime of TEI-LP with respect to frequency level                   |    |

|      | count; (d) Extra energy consumption with respect to core count; (e) Speedup                    |    |

|      | with respect to core count; (f) Runtime of TEI-LP with respect to core count. $$ .             | 62 |

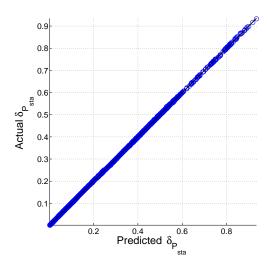

| 5.1  | Prediction accuracy of $\delta_{P_{sta}}$ (Equation 5.2): Ideally, all points should lie along |    |

|      | the diagonal.                                                                                  | 69 |

| 5.2  | Proposed flow for determining the steady state operating temperature                           | 74 |

List of Figures xv

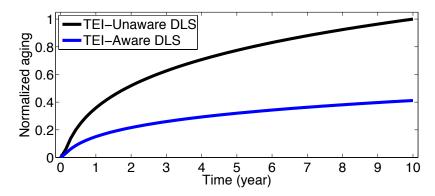

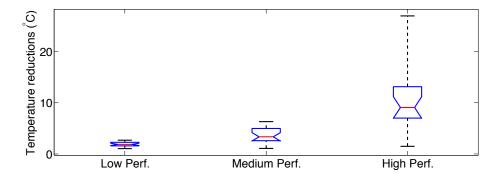

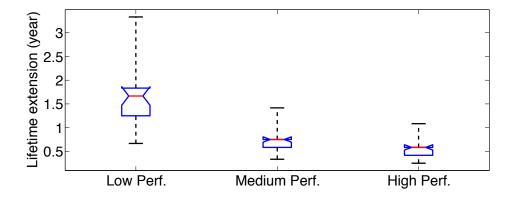

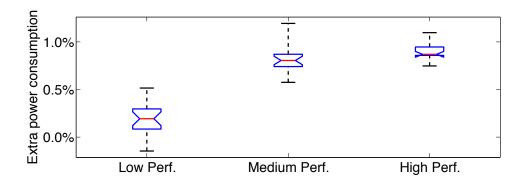

| 5.3 | Improvement of TEI-Aware over TEI-Unaware DLS for aging reduction for a            |    |

|-----|------------------------------------------------------------------------------------|----|

|     | typical application                                                                | 77 |

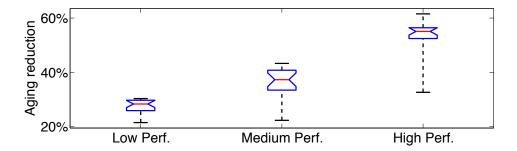

| 5.4 | Improvement of TEI-Aware over TEI-Unaware DLS for aging reduction under            |    |

|     | various performance constraints                                                    | 78 |

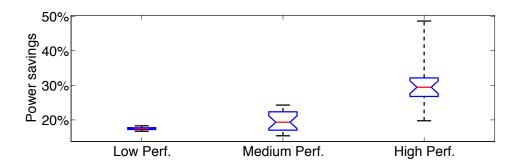

| 5.5 | Improvement of TEI-Aware over TEI-Unaware DLS for power savings under var-         |    |

|     | ious performance constraints                                                       | 78 |

| 5.6 | Improvement of TEI-Aware over TEI-Unaware DLS for temperature reduction            |    |

|     | under various performance constraints                                              | 78 |

| 5.7 | The extended lifetime of AgingMin against TEI-Aware DLS under different per-       |    |

|     | formance constraints                                                               | 80 |

| 5.8 | The extra power consumed from AgingMin against TEI-Aware DLS under dif-            |    |

|     | ferent performance constraints                                                     | 80 |

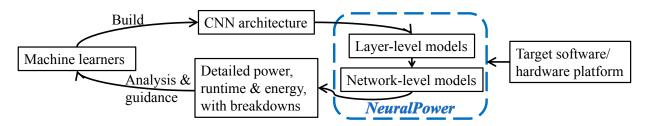

| 6.1 | NeuralPower quickly predicts the power, runtime, and energy consumption of         |    |

|     | a CNN architecture during service phase. Therefore, NeuralPower provides the       |    |

|     | machine learners with analysis and guidance when searching for energy-efficient    |    |

|     | CNN architectures on given software/hardware platforms                             | 83 |

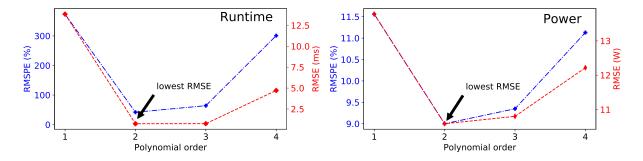

| 6.2 | Comparison of best-performance model with respect to each polynomial order for     |    |

|     | the fully-connected layers. In this example, a polynomial order of two is chosen   |    |

|     | since it achieves the best Root-Mean-Square-Error (RMSE) for both runtime and      |    |

|     | power modeling. At the same time, it also has the lowest Root-Mean-Square-         |    |

|     | Percentage-Error (RMSPE)                                                           | 89 |

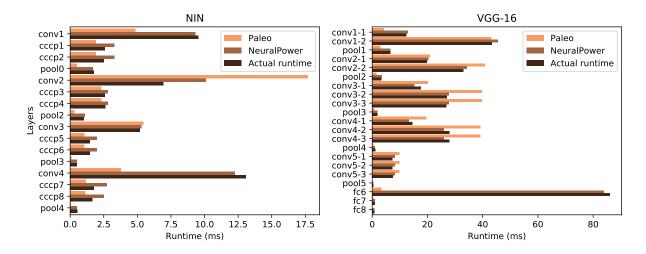

| 6.3 | Comparison of runtime prediction for each layer in NIN and VGG-16: Our models      |    |

|     | provide accurate runtime breakdown of both network, while Paleo cannot. Our        |    |

|     | model captures the execution-bottleneck layers (i.e., $conv4$ in NIN, and $fc6$ in |    |

|     | VGG-16) while Paleo mispredicts both                                               | 93 |

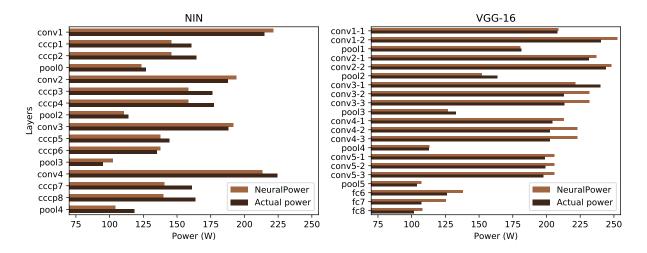

| 6.4 | Comparison of power prediction for each layer in NIN and VGG-16                    | 95 |

# Chapter 1

### Introduction

Power and energy issues have become the major design constraints in developing highperformance computing systems. Several hardware- and software-based techniques exist to

resolve them. For multicore processors, Dynamic Voltage and Frequency Scaling (DVFS)

is widely used in both academia and industry, mainly to reduce the power consumption

while maintaining the same performance. Upscaling of voltage/frequency (V/F) for multicore processors has also been explored by processor manufacturers, e.g., in Intel's Turbo

Boost [15]. Similar techniques are also discussed in other work [88][45]. Nevertheless, as

CMOS technology aggressively scales down to deca-nanometer technology nodes, these issues

have also emerged as important reliability threats throughout the system lifetime. Aging

concerns have therefore gathered a significant momentum and they have already triggered

extensive research on aging modeling and mitigation techniques for older planar MOSFETbased system design.

From a technology standpoint, CMOS technology evolution has recently provided fundamental advancements in addressing power, thermal and aging problems. FinFET has been widely chosen as the next generation CMOS technology, especially for sub-20 nm technology nodes. Because of the different structures between planar CMOS and FinFET, different performance characteristics have been observed between them [54]. In terms of aging considerations, we have recently experienced a "paradigm shift" from older MOSFET-based

models to more accurate and detailed aging models [26]. Moreover, in terms of thermal considerations, the patterns of gate delay for FinFET with respect to temperature are quite different when compared with planar CMOS. The effect is called temperature effect inversion (TEI) [57]. TEI refers to the phenomenon in which the gate delay of FinFET decreases as temperature increases in superthreshold voltage region.

From the application perspective, deep learning, especially convolutional neural networks (CNNs) have been widely used in several important areas, such as text processing and computer vision, in both academic and industrial setups. That is because CNNs have claimed dominance over other existing methods in these domains [31] [36]. However, the high energy consumption of CNNs, which can be attributed to both (a) high power consumption and (b) long runtime, has limited the types of platforms that CNNs can be deployed on. Therefore, it is necessary to introduce energy-efficient CNNs to platforms with limited resources. To achieve energy-efficient CNN designs, it is critical to have accurate power, runtime and energy models.

#### 1.1 Challenges

To resolve the power and energy issues for high-performance computing systems, there are two major challenges. The first is to have accurate power and performance models. Due to the fact that the complexity of the computing systems is increasing, it is always a challenge to have accurate power and performance models. As long as the models are found, one needs to face the second challenge: efficient system optimization. The optimization techniques usually vary greatly from one system to another. Therefore, we need to tackle the challenges case by case. Sometimes, domain knowledge can help to develop new techniques. We list several challenges in details in the following.

The first challenge is to address process variations (PVs). Near-Threshold Computing (NTC) has emerged as a promising solution to greatly increase the energy efficiency of next-generation multi-core systems. However, PVs expose an important effect on the performance

of NTC. Therefore, it is significant to understand and model the PVs, especially when NTC is adopted in emerging computing systems.

Second, it is critical to utilize TEI. As CMOS technology continues scaling, FinFET has recently become the common choice for multi-core systems. In contrast with planar CMOS, FinFET is characterized by lower delay under higher temperatures in super-threshold voltage region, *i.e.*, TEI. To fully utilize the potential of FinFET, it is critical to understand and consider TEI before optimizing the computing systems.

The third challenge comes from the thermal effects, especially aging. Power and thermal issues are the main constraints for high-performance multi-core systems. As the current technology of choice, FinFET is observed to have TEI. While it has been shown that system performance can be improved under power constraints, as technology aggressively scales down to sub-20nm nodes, thermal issues emerge as important reliability concerns throughout the system lifetime.

Finally, it is always hard to analyze the energy efficiency of deep learning applications, such as convolutional neural networks (CNNs). With the increased popularity of CNNs deployed on the wide-spectrum of platforms (from mobile devices to workstations), the related power, runtime, and energy consumption have drawn significant attention. From lengthening battery life of mobile devices to reducing the energy bill of datacenters, it is important to understand the efficiency of CNNs during serving for making an inference, before actually training the model. However, the complexity introduced from both the software side and hardware side makes it difficult to understand CNN efficiencies.

#### 1.2 Thesis contributions

In this thesis, we combine machine learning techniques and domain knowledge to learn the performance, power models for high-performance computing systems. Experimental results show that our learning-based performance and power models on these systems have a high accuracy.

For technology-aware FinFET-based multi-core systems, we propose power-/performance-related management algorithms, including 1) increasing performance at iso-power; 2) reducing power while keeping the same performance; 3) decreasing aging effects with negligible power overhead at iso-performance. For application-aware computing systems which run various deep learning applications, especially CNNs, we apply our learning based model to predict the power, runtime, and energy for various neural network configurations and hardware platforms. The detailed contributions are described in the following.

Learning-based power/performance models: We evaluate PVs and learn the power and performance models for multi-core systems operating under extended range: including near-threshold, nominal, and Turbo modes. We propose to model the problem of the energy minimization or throughput maximization under given requirements as constrained convex optimization problems that can be solved efficiently. Considering PVs on FinFET-based chip-multiprocessors (CMPs), experimental results show that at 30% PV levels, our proposed method (1) reduces energy consumption by 31.09% at iso-performance and (2) increases throughput by 11.46% at iso-power when compared with variation-agnostic nominal case [7].

TEI-aware model and learning: We explore TEI-aware performance improvement and energy savings for multi-core systems. Our experimental results show that on average 15.70% throughput improvement or 31.26% energy savings can be achieved in steady state by a TEI-aware DVFS policy over a TEI-agnostic one. We observe multiple sweet spots resulting from TEI effects and introduce fast algorithms which provide iso-power maximum performance or iso-performance minimum energy consumption. Experimental results confirm the effectiveness of the proposed approach by exhibiting a 45.9-55.3x speedup when compared to state-of-the-art algorithms while losing only 0.22% or 0.68% in achieved performance or energy, respectively [9] [10].

Aging reduction: We are the first to provide a comprehensive evaluation of both TEI and aging effects on the performance and power of FinFET-based multi-core systems with multiple voltage/frequency levels. Our experimental results show that aging effects can be

reduced by up to 53.59% by exploiting the TEI effect. Based on a combined multivariate objective for power and aging, this work proposes an aging-aware algorithm, dubbed *Aging-Min*, to select the optimal TEI-aware voltage/frequency operation points for decreasing the aging effects. Experimental results show that *AgingMin* improves the classic 10-year system lifetime by an average of 1.61 years while introducing less than 1% power overhead when compared to existing state-of-the-art techniques [11].

Modeling for CNN: we propose NeuralPower: a layer-wise predictive framework based on sparse polynomial regression, for predicting the serving power, runtime, and energy consumption of a CNN deployed on any GPU platform. Given the architecture of a CNN, NeuralPower provides an accurate prediction and breakdown for power and runtime across all layers in the whole network, helping machine learners quickly identify the power, runtime, or energy bottlenecks. The experimental results show NeuralPower predicts the runtime, power, and energy of state-of-the-art CNN architectures, with an average accuracy of 88.24%, 88.34%, and 97.21%, respectively. We comprehensively corroborate the effectiveness of NeuralPower as a powerful framework for machine learners by testing it on different GPU platforms [8].

#### 1.3 Thesis organization

The rest of this thesis is organized as follows. Chapter 2 introduces the background knowledge related with PV, TEI, aging effects, and CNNs. Chapter 3 details the power and performance modeling and optimization for process-variation aware multi-core systems. Chapter 4 provides TEI-aware power-performance optimization for FinFET-based multi-core systems. Chapter 5 details the interaction of TEI and aging effects, and the algorithm to reduce aging process by considering TEI effect. Chapter 6 discusses the modeling process and results for power and runtime of convolutional neural networks. Chapter 7 provides the related work. Chapter 8 concludes this thesis and discusses the possible future research directions.

# Chapter 2

# Background

#### 2.1 Technology-aware computing system design

FinFET, a type of non-planar double-gate device, has become the next generation CMOS technology of choice, especially for sub-20 nm technologies. In this section, we discuss the effects associated with this technology, including process variations (PVs), temperature effect inversion (TEI), and aging effects.

We first introduce PVs. As a compounding factor, when transistors scale down and supply voltage reaches near-threshold levels, PVs complicate chip design. Therefore, a thorough understanding of how PVs affect power-performance of CMPs is necessary. Due to the differences in channel and gate formations between bulk CMOS and FinFET, their major sources of process variations are not the same. FinFET has three parameters: gate length  $(L_G)$ , work function  $(\Phi_G)$  and fin thickness  $(T_{SI})$ , which dominate the PVs' effects [16] [55]. Compared to bulk CMOS, we can see there are new dominant factors for PVs' effects, like fin thickness, which is unique for FinFET with 3D fins. Generally a process parameter  $\Theta$  affected by variations is described as:  $\Theta = \Theta_{nom} + \delta_{total}$ , where  $\Theta_{nom}$  denotes the nominal value and  $\delta_{total}$  is total variation from  $\Theta_{nom}$ . In addition, It is widely known that variations are composed of wafer-to-wafer (W2W), die-to-die (D2D) and within-die (WID) variation.

Considering the spatial correlations induced by the manufacturing process, these random variables are difficult to characterize.

Second, we move to explain how TEI occurs. It is well-known that the operating frequency of a digital system is strongly affected by gate delays. The delay of a logic gate is greatly controlled by the drive current. When the drive current decreases, the corresponding gate delay increases, which finally determines a lower operating frequency of the system to meet the timing.

In the case of traditional planar CMOS, it is well known that as temperature increases, the corresponding drive current decreases in the superthreshold voltage region. Therefore, under high operating temperature, processors composed of billions of CMOS devices have to decrease their operating frequency to meet the timing and therefore, performance is decreasing.

For FinFET devices, the trends are quite distinct. One of the biggest differences between FinFET and planar CMOS devices is the structure of the channel. In contrast to planar CMOS comprising of a flat channel with one gate on top of it, FinFET devices have a 3D channel, which is called a "fin". As technology node decreases, the fin becomes smaller and thinner, thus becoming more vulnerable to structural effects. When temperature increases, the tensile effect from the insulator layer below the fin becomes larger, which induces the bandgap narrowing in the channel. The bandgap narrowing directly results in the drop in threshold voltage. In addition, the tensile stress causes a slight increase in the carrier mobility. Therefore, the increase in temperature results in a decrease in FinFET gate delay, which is TEI.

One direct consequence of TEI is that the worst case timing takes place at lowest operating temperatures for FinFET-based circuits. As temperature increases, gate delay decreases, which allows circuits to potentially run at a higher frequency. Digital systems are usually designed to work in a temperature range from -25 °C to 125 °C [57]. Therefore, the worst case timing in FinFET-based digital systems is at -25 °C, rather than 125 °C. To illustrate this effect, we run SPICE simulations for a fan-out-of-four (FO4) ring oscillator (RO) from

Figure 2.1: Maximum operating frequency under a wide range of temperature values for FinFET.

PTM [12] library in a 16 nm FinFET technology node, which is validated against ITRS roadmap [77]. Figure 2.1 shows the normalized maximum operating frequencies for different supply voltage levels in high-performance mode. It is clear that the operating frequency of FO4 RO increases as temperature gets higher. The same effect is also observed in low-power mode.

Finally, we introduce aging effects for FinFET. As described before, TEI allows for devices to run faster at higher operating temperatures. In Figure 2.2, the solid lines correspond to the normalized maximum operating ring oscillator (RO) frequency under the TEI effect. Nonetheless, the manifestation of aging has an exact opposite, counteracting effect: BTI/RTN mechanisms generate traps to capture minority carriers that eventually leads to  $\Delta V_{th}$  fluctuations from the nominal threshold voltage value [85]. Consequently, existing TEI-aware analyses and system-level models inherently fail to account for aging-induced performance degradation, thus resulting in overly-optimistic results. To illustrate this key observation, the dotted lines in Figure 2.2 show the normalized maximum operating RO frequency under the TEI effect and under aging for three and ten years. To achieve a representative comparison, we repeat the HSPICE simulation for the same supply voltage levels as in the aging-unaware cases.

Figure 2.2: Maximum operating RO frequency under the impact of TEI and aging.

We can easily observe that overall performance throughout the RO lifetime is affected by both the TEI effect and the aging mechanisms. Thus, a model that inherently accounts for both these effects is essential for developing an effective yet representative aging reduction scheme for FinFET-based many-core systems.

#### 2.2 Application-driven computing system design

In recent years, CNNs have been widely applied in several important areas, such as text processing and computer vision, in both academia and industry. However, the high energy consumption of CNNs has limited the types of platforms that CNNs can be deployed on, which can be attributed to both (a) high power consumption and (b) long runtime. GPUs have been adopted for performing CNN-related services in various computation environments ranging from data centers, desktops, to mobile devices. In this context, resource constraints in GPU platforms need to be considered carefully before running CNN-related applications.

Figure 2.3: Prediction accuracy versus energy consumption of popular CNN models. This figure is adopted from [91]. Some models are pruned with either magnitude-based pruning [29] or energy-aware pruning [91]. For the architectures that achieve similar accuracy levels during test phase, the energy consumption can vary by close to  $10\times$ .

In this thesis, we focus on the testing or service phase since, CNNs are typically deployed to provide services (e.g., image recognition) that can potentially be invoked billions of times on millions of devices using the same architecture. Therefore, testing runtime and energy are critical to both users and cloud service providers. In contrast, training a CNN is usually done once. Orthogonal to many methods utilizing hardware characteristics to reduce energy consumptions, CNN architecture optimization in the design phase is significant. In fact, given the same performance level (e.g., the prediction accuracy in image recognition task), there are usually many CNNs with different energy consumptions. Figure 2.3 shows the relationship between model testing accuracy and energy consumption for a variety of CNN architectures [91]. We observe that several architectures can achieve a similar accuracy level. However, the energy consumption drastically differs among these architectures, with the difference close to  $10 \times$  in several cases. Therefore, seeking for energy-efficient CNN architecture without compromising performance seems intriguing, especially for large-scale deployment.

# Chapter 3

# Learning for many-core system optimization

#### 3.1 Chapter overview

Nowadays, power consumption plays a more and more important role in designing modern processors. Near-threshold computing (NTC) is a promising technique for power consumption reduction by lowering supply voltage to a value near the threshold voltage of transistors [37]. Operating frequency also scales down with supply voltage to give extra reduction in dynamic power consumption. However, as the frequency scales, the degradation in performance increases. In the context of multi-core systems, under performance constraint, it is not always possible to down-scale voltage/frequency due to the increased performance penalty. On the other hand, Turbo Boost (TB), where the operating voltage and frequency are upgraded higher than nominal values, has been widely implemented to improve the performance [15].

Although DVFS has been well studied for dynamic power management, extended range DVFS (ExDVFS)—DVFS over a wide operating range of voltage and frequency from NTC all the way to TB—remains to be further explored. In the turbo mode, one can upscale voltage/frequency points to achieve better performance, while in NTC mode, supply voltage decreases further to reduce power consumption. By allowing for an extended excursion for

the voltage/frequency pairs, one can more efficiently trade-off power or performance slack across cores running imbalanced threads so as to achieve better power efficiency or higher performance increase.

In addition to architecture-level advancement, FinFET, a type of non-planar double-gate device, has become main stream below the 22nm technology node. In the NTC region, since supply voltage is close to threshold voltage, the overdrive voltage is greatly affected by the change of threshold voltage induced by process variations (PVs). Although, PVs in FinFET have been extensively studied at the circuit level [90] [16], their impact in architecture level is yet to be explored. Therefore, there are more challenges considering FinFET-based computer systems with PVs.

As transistor technology evolves, it naturally motivates us to explore how power and performance optimization works on FinFET-based CMPs. Previous work addressed power and performance optimization on bulk-CMOS based CMPs [84] [44] [24] [63]. However, none of them has studied similar topics on FinFET-based CMPs, especially considering PVs. Our work in this chapter not only constructs a power and performance optimization framework, but also characterizes the impact of PVs and core count in FinFET-based CMPs. The detailed results will be discussed in Section 3.6.5.

#### 3.1.1 Chapter contributions

To the best of our knowledge, the following novel contributions are described and supported in this chapter:

• We perform the quantitative characterization of PV effects in FinFET and propose an accurate multivariate polynomial model to learn power-PV parameter relationship. We then integrate PV information for each individual core in CMPs to get the contraint-posynomial frequency-power model.

- By leveraging the convexity of learned model, we convert the problem of the energy minimization under performance requirements into a constrained convex optimization problem that can be solved efficiently.

- As opposed to energy minimization, we also determine the maximum possible performance under a given power budget over a wide-operating range.

- In addition, further experiments **uniquely** show the benefits from our methods significantly increase with increasing core count and variation level, either in energy savings or throughput improvements. Our work also shows that iso-performance energy savings or iso-power performance improvements in FinFET technology are similar to those obtained for bulk CMOS, but the effect of PVs magnifies these benefits in the case of FinFET implementations.

#### 3.2 Power model and performance metrics

Now we introduce the model used to characterize the dynamic and static power. For a logic module, the power can be divided into dynamic power  $(P_{dyn})$  and static power  $(P_{sta})$ , which can be written as:

$$P_{tot} = P_{dyn} + P_{sta} = \alpha \cdot C_{tot} \cdot V_{dd}^2 \cdot \mathfrak{F} + k_{sta} \cdot I_{leak} \cdot V_{dd}$$

(3.1)

where  $\alpha$  is the switching activity rate,  $C_{tot}$  is load capacitance for the switching gates, and  $k_{sta}$  is a constant proportional to the transistor count of that module. In addition,  $\mathfrak{F}$  is the clock frequency,  $I_{leak}$  is the gate leakage current, and  $V_{dd}$  is the supply voltage.

However, the dynamic power and static power for a core in a CMP are more complicated than the expression in Equation 3.1. To achieve a good abstraction of core level power model, we adopt the convex power similar to the one proposed by Juan *et al.* [44]. The total power consumption of a core is formulated as:

$$P(\mathfrak{F}) = P_{dym}^{peak} \cdot f_d(\mathfrak{F}) \cdot u(\mathfrak{F}) + P_{sta}^{peak} \cdot f_s(\mathfrak{F})$$

(3.2)

where  $P_{dyn}^{peak}$  and  $P_{sta}^{peak}$  are the peak dynamic power and static power respectively, which are determined for the case in which all process parameters, operating voltage/frequency are at nominal values and the utilization is full. The  $f_d(\mathfrak{F})$  and  $f_s(\mathfrak{F})$  are two functions which characterize the dynamic power and static power in terms of the operating frequency and implicitly supply voltage. Finally,  $u(\mathfrak{F})$  expresses the change in dynamic power due to the change of workload, *i.e.*, the change in the utilization. As the utilization is implicitly a function of frequency, we use  $u(\mathfrak{F})$  to denote this.

One of the main drawbacks of the power model stated in Equation 3.2 is that it doesn't take PVs into consideration. To address this problem, we propose a hierarchical two-level regression model in Section 3.3.1.

After obtaining the model for  $f_d$  and  $f_s$  in Equation 3.2, we still need an accurate model for u. As shown in previous work, for CMPs, instructions committed per cycle (IPC) is a good approximate for the activity rate of one core. Based on prior work [66] [4], we approximate the dynamic power as a linear function of IPC. As the other components in Equation 3.2 are utilization independent, it follows that u is a linear function of IPC:

$$u = c_1 \cdot IPC + c_2 \tag{3.3}$$

To measure the performance of a CMP, we use the total throughput (TP) as the metric. Then, performance can be calculated as:

$$TP = \sum_{i=1}^{n} IPC_i \cdot \mathfrak{F}_i \tag{3.4}$$

where  $IPC_i$  and  $\mathfrak{F}_i$  are the instructions per cycle (IPC) and the operating frequency for core i, while n is the total number of cores.

#### 3.3 Model learning process

The proposed power model has two components: (1) the frequency function f, and (2) the utilization function u. To learn  $\hat{f}$  and  $\hat{u}^{-1}$ , we adapt constrained-posynomial functions

$<sup>^{1}</sup>$ As a notation convention in machine learning and statistics, any symbol with a  $\hat{hat}$  represents an estimate, instead of actual values or functions

to map both operating frequency and utilization to the corresponding power consumption by using leave-one-out cross validation (LOOCV). Compared to CMOS-based CMPs, we integrate process variations in the learning process for FinFET-based CMPs. The accuracy and overall validation of the learned model are also provided.

#### 3.3.1 Learning the frequency-power relationship

Extended range operation, especially near-threshold voltage, is more severely affected by process variations than nominal operation and thus, PV effects must be incorporated for a robust model. To address this issue, we propose a variation-aware regression model customized for each core based on PV maps.

Figure 3.1: Hierarchical grid-based modeling of process variations for a CMP die with 16 cores. Different grey levels represent different PV values. The PV pattern used here is only for illustration.

First, we implement a hierarchical grid-based PV model considering spatial correlation as shown in Figure 3.1, a similar one used by Agarwal  $et\ al.$  [1]. Specifically, for component j in core i, the total variation can be expressed as:

$$\delta_{total_{i,j}} = \delta_D + \delta_{C_i} + \delta_{R_j} \tag{3.5}$$

where  $\delta_D$  is die-level variation,  $\delta_{C_i}$  core-level variation and  $\delta_{R_j}$  component-level variation. The three components in Equation 3.5 are independent identical Gaussian random variables (RVs) [1] [14] with mean zero. In addition, we assume their standard deviation is  $\sigma$ . For  $L_G$  and  $T_{SI}$ , we consider two cases,  $3\sigma$  as 10% and 30% of the corresponding nominal value. For  $\Phi_G$ , we also consider two cases,  $3\sigma$  as 10% and 30% of  $|\Phi_{G,N} - \Phi_S|$ , where  $\Phi_{G,N}$  is the corresponding nominal value and  $\Phi_S$  is the work function of the intrinsic semiconductor material [16].

Next, we propose a grid-based modeling methodology in which we first learn the power model for every grid cell (representing a core component) as a function of the process parameters in that grid cell and  $V_{dd}$ . To quantify the impact of process parameters, we propose a model for total power consumption in a module (or core component) as:

$$P_m(\mathbf{X}) = P_{m,dyn}^{peak} \cdot f_{m,d}(\mathbf{X}) \cdot u_m(\mathfrak{F}) + P_{m,sta}^{peak} \cdot f_{m,s}(\mathbf{X})$$

(3.6)

where  $\mathbf{X} = [V_{dd}, L_G, \Phi_G, T_{SI}]$ .  $V_{dd}$  is paired with  $\mathfrak{F}$  for a set of PV parameters.  $P_{m,dyn}^{peak}$  and  $P_{m,sta}^{peak}$  are the peak dynamic and static power, respectively.  $f_{m,d}(\mathbf{X})$  and  $f_{m,s}(\mathbf{X})$  are two functions which characterize the dynamic/static power in terms of process parameters and  $V_{dd}$ . By using process variation maps, one can integrate all components of a specific core, and obtain the final  $(p^{\ell}, \mathfrak{F}^{\ell})$  data for a typical core as in Section 3.3.1.

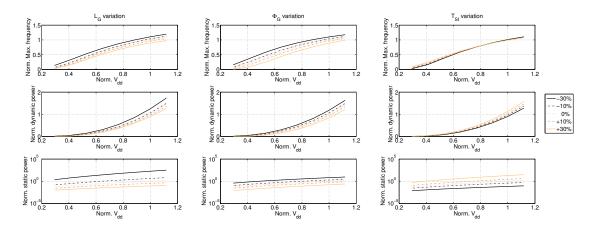

We evaluate the dominant process parameters  $L_G$ ,  $T_{SI}$  and  $\Phi_G$ . We use PTM model cards for 16nm FinFET technology node to form a 23-stage Ring Oscillator (RO) in HSPICE to characterize the delay and total power, and a two-stage inverter chain to characterize the static power. We vary the process parameter values to get their effects on the performance and power. We also change the supply voltage  $V_{dd}$  from 0.35V to 1.05V (nominal value is 0.85V) to change operating mode from NTC all the way to TB. Referring to [41], the operation models are defined as: (1) NTC:  $V_{dd} = [0.35, 0.55]$ ; (2) regular DVFS range:  $V_{dd} = [0.55, 0.85]$ ; (3) TB:  $V_{dd} = [0.85, 1.05]$ . We change the  $V_{dd}$  and process parameters values to measure the frequency, dynamic power, and static power for the RO in HSPICE. Figure 3.2 shows HSPICE simulation results - the normalized maximum frequency, dynamic power and static power corresponding to the three process parameter variations for two cases: mild variation (3 $\sigma = 10\%$ ) and extreme variation (3 $\sigma = 30\%$ ), with respect to different  $V_{dd}$  values. It shows mild (extreme) variation introduce up to 26.13% (81.89%) variation in delay,

19.42% (51.59%) in dynamic, and 3.55X (217X) in leakage power. Furthermore, these variations tend to have a higher impact on delay near threshold, while for dynamic/static power they tend to be higher in nominal and turbo modes.

Figure 3.2: Maximum frequency, dynamic power and static power with respect to process variations. All three PV parameters have a significant impact on static power. They also affect delay and dynamic power across a wide range of operating frequency.

For frequency and dynamic power, we choose a multivariable polynomial regression model. For static power, an exponential multivariable polynomial regression model is a better choice. That is because the static power follows an exponential dependency with respect to the threshold voltage.

Let's consider the dynamic power (for simplicity, we denote it as  $f_m(\mathbf{X})$ ) as example to illustrate how we establish our power model for a module. After experimenting with different multivariable polynomial regression models, we finally choose the one with a total degree of up to four:

$$f_m(\mathbf{X}) = \sum_i c_i \cdot V_{dd}^p \cdot L_G^q \cdot \Phi_G^r \cdot T_{SI}^s$$

$$p, q, r, s \in \{\mathbb{N}, 0\}, \quad p + q + r + s \le 4.$$

$$(3.7)$$

Using a similar learning-based regression process as shown in Section 3.3.1, we achieve a Root-Mean-Square-Percentage-Error (RMSPE) as low as **0.25**% for the dynamic power in the cross validation phase. The same technique applies to the regression of the maximum

frequency  $\mathfrak{F}$  with cross validation RMSPE of 0.38%. For static power, the exponential multivariable polynomial model achieves a cross validation RMSPE of 0.96%.

We continue to collect the power and frequency for the cores in the CMPs. As mentioned before, we use grid-based PV maps to simulate the PVs in CMPs. Specifically, there are three variation sources, die level, core level and core component level. In our experimental setup, one die has  $4\times4$  cores, and each core is composed of  $8\times8$  grid cells, which is illustrated in Figure 3.1. Therefore, the total variation  $\delta_{total_{i,j}}$  for each grid cell j in core i is composed of three Gaussian RVs:  $\delta_D$  in that die,  $\delta_{C_i}$  in core i and  $\delta_{R_j}$  in grid cell j as described in Equation 3.5. Given a set of PV maps, the power consumption for each core only depends on the resulting voltage/frequency pair while considering process variations as described above. By using the accurate power-frequency model we get from the detailed per-core variation information, we achieve unique values for  $\mathfrak{F}$ ,  $f_d$  and  $f_s$  for each  $V_{dd}$  of each core, based on the following rules.  $\mathfrak{F}$  is the minimum frequency across all the grid cells in the core so as to satisfy the timing within each core, while  $f_d$  or  $f_s$  is the sum of  $f_{m,d}$  or  $f_{m,s}$  for all grid cells in that core for a given  $V_{dd}$ . After this integration step, we get the pair  $(p^\ell, \mathfrak{F}^\ell)$  for each core. Due to this integration of PVs, our proposed power models are implicitly heterogeneous, even for a homogeneous multi-core architecture.

#### 3.3.2 Learning the utilization-power relationship

After  $\hat{f}_d$  and  $\hat{f}_s$  are obtained, we now learn the utilization-power relationship,  $u(\mathfrak{F})$ . As prior work [4] has pointed out, the dynamic power can be approximated as a linear function of IPC, since IPC approximately represents the activity rate of a processing core. Therefore,  $u(\mathfrak{F})$  can be expressed as:

$$u(\mathfrak{F}) = c_1 \cdot IPC + c_2 \tag{3.8}$$

where  $c_1$  and  $c_2$  are fitting coefficients. From the dataset, a positive correlation between IPC and dynamic power consumption has been observed. In other words, higher IPC contributes to higher dynamic power dissipation, and vice versa, which leads to a positive slope  $c_1$ .

Furthermore,  $c_2$  is also positive since power is still consumed even for a very low (or close to zero) IPC. Therefore, both  $c_1$  and  $c_2$  are positive and the convexity of model is maintained. Equation 3.8 is a constrained posynomial with d = 1 (the highest order of the polynomial is one), and we repeat the learning procedure described in Section 3.3.1 to learn  $\hat{c}_1$ ,  $\hat{c}_2$  with d set to one.

| Parameters        | Values                                                |

|-------------------|-------------------------------------------------------|

| Number of cores   | 16                                                    |

| Nominal frequency | 2660 MHz                                              |

| Core model        | Intel <sup>®</sup> -X86 Gainestown <sup>®</sup> -like |

| L2 caches         | Private 256KB, 4-way SA, LRU                          |

| L3 caches         | Shared 32MB, 16-way SA, LRU                           |

| DRAM              | 4GB                                                   |

16nm node with FinFET

Technology

Table 3.1: Target architecture.

Here, we describe the dataset  $(p^{\ell}, IPC^{\ell})$  used to learn the  $\hat{c}_1$ ,  $\hat{c}_2$  of  $\hat{u}(\mathfrak{F})$ . The operating frequency of  $(p^{\ell}, IPC^{\ell})$  is fixed at the nominal value, and therefore the changes in dynamic power dissipation come only from the workload characteristics, not voltage/frequency scaling. We use Sniper [13] as the architectural simulator to collect IPCs  $(IPC^{\ell})$  and other required workload characteristics. The target architecture is described in Table 3.1. Default settings are used for the parameters not mentioned here. To demonstrate our approach, we use both PARSEC [3] and SPLASH-2 [89] benchmarks that contain a wide spectrum of multi-threaded parallel applications. For power, we use McPAT [58] to collect dynamic power traces  $(p^{\ell})$ . The temperature here is set to 330K, a typical stable temperature for our target processors. McPAT also provides 16nm FinFET technology parameter set to simulate power, area, and timing under 16nm node. Therefore, McPAT can simulate power of Intel Gainestown-like cores in 16nm FinFET technology. Finally, the average error of the learned is  $\hat{u}(\mathfrak{F})$  2.84%. Similar results are also reported by others [4]. After  $\hat{f}_d(\mathfrak{F})$ ,  $\hat{f}_s(\mathfrak{F})$  and  $\hat{u}(\mathfrak{F})$  are obtained, we are in position to examine the overall learned model  $\hat{P}(\mathfrak{F})$ .

#### 3.3.3 Model validation

So far, the accuracies of  $\hat{f}_d(\mathfrak{F})$ ,  $\hat{f}_s(\mathfrak{F})$  and  $\hat{u}(\mathfrak{F})$  have been determined separately, and therefore the accuracy of the overall learned  $\hat{P}(\mathfrak{F})$  remains unknown. In this section,  $\hat{P}(\mathfrak{F})$  is validated with the power consumption of a whole processor at different frequencies under various workload characteristics. By plugging  $\hat{f}_d(\mathfrak{F})$ ,  $\hat{f}_s(\mathfrak{F})$  and  $\hat{u}(\mathfrak{F})$  into Equation 3.2, the overall power function  $\hat{P}(\mathfrak{F})$  can be expressed as:

$$\hat{P}(\mathfrak{F}) = P_{dyn}^{peak} \cdot \hat{f}_d(\mathfrak{F}) \cdot \hat{u}(\mathfrak{F}) + P_{sta}^{peak} \cdot \hat{f}_s(\mathfrak{F})

= P_{dyn}^{peak} \left( \sum_{i=0}^{5} \hat{\alpha}_i \mathfrak{F}^i \right) \left( \hat{c}_1 \cdot IPC + \hat{c}_2 \right) + P_{sta}^{peak} \left( \sum_{i=0}^{6} \hat{\alpha}'_j \mathfrak{F}^j \right)$$

(3.9)

We collect the power traces, both dynamic and static power, from McPAT with the settings described in Section 3.3.2. In addition to the nominal frequency (2.66GHz), the frequencies are also set to the range (from 3.06GHz to 1.46GHz) at which McPAT has been extensively validated. Please note that NTC is not included here, since McPAT has not been validated for NTC voltage values. Furthermore, only the power values at the nominal frequency are used to train  $\hat{u}(\mathfrak{F})$  as described in Section 3.3.2. In other words, the power values calculated not at the nominal frequencies are not involved in any part of the training process of  $\hat{u}(\mathfrak{F})$  (and thus  $\hat{P}(\mathfrak{F})$ ) — they are "clean" to test the accuracy of  $\hat{P}(\mathfrak{F})$ .

Table 3.2: Validation error of the learned  $\hat{P}$ .

| Benchmark | blackscholes  | canneal   | dedup   | fluidanimate |

|-----------|---------------|-----------|---------|--------------|

| 3.06GHz   | 3.72%         | 1.12%     | 10.19%  | 3.05%        |

| 1.46GHz   | 5.10%         | 3.69%     | 12.08%  | 3.57%        |

| Benchmark | streamcluster | swaptions | vips    | ferret       |

| 3.06GHz   | 7.17%         | 1.49%     | 12.56%  | 1.90%        |

| 1.46GHz   | 9.20%         | 1.77%     | 14.26%  | 2.56%        |

| Benchmark | barnes        | fmm       | lu.cont | ocean.cont   |

| 3.06GHz   | 7.02%         | 4.79%     | 6.22%   | 6.47%        |

| 1.46GHz   | 5.95%         | 3.68%     | 6.83%   | 7.69%        |

| Benchmark | radiosity     | radix     | water   | Average      |

| 3.06GHz   | 2.24%         | 5.11%     | 0.98%   | 4.94%        |

| 1.46GHz   | 1.09%         | 5.55%     | 1.02%   | 5.33%        |

Table 3.2 illustrates that the overall average error is **4.94**% and **5.33**% for the two modes, respectively, or **5.14**% on average across various benchmarks in both PARSEC and SPLASH-2. This confirms that the learned model can accurately describe the power-performance relationship under different voltage/frequency levels and work variations.

#### 3.4 Constrained optimization

We construct a convex power model expressed in Equation 3.2. As mentioned in Section 3.2,  $P_{dyn}^{peak}$  and  $P_{sta}^{peak}$  are two positive design parameters.  $f_d$  and  $f_s$  are two posynomial function of  $\mathfrak{F}$ . The remaining u is a linear function of IPC with two positive coefficients  $c_1, c_2$ . Therefore, Equation 3.2 is convex with respect to  $\mathfrak{F}$  when given a certain IPC value.

In this chapter, we perform a limit study for ExDVFS, with and without PVs and considering various multi-threaded benchmarks on a CMP. To achieve that, we assume here that the voltage/frequency pairs are continuous across the wide operating range, which may not be practical, but offers a conservative upper bound on savings achieved when evaluating ExDVFS. We make use of convex program to formulate and analyze the two following optimal problems: (1) minimize energy consumption under iso-performance requirement; (2) maximize performance under iso-power conditions.

#### 3.4.1 Constrained energy minimization

We first study the energy minimization under given throughput constraint. In this work, we assume that the workload characteristic, especially the IPC for each core in each control epoch can be obtained from performance counters. Based on this, this problem for an *n*-core CMP can be formulated as a convex program during each control epoch:

Objective :

$$arg \min_{\mathfrak{F}_i} \sum_{i=1}^n P_i(\mathfrak{F}_i)$$

Subject to :  $\sum_{i=1}^n IPC_i \cdot \mathfrak{F}_i \ge Perf_{const}$  (3.10)

$\mathfrak{F}_{min} \le \mathfrak{F}_i \le \mathfrak{F}_{max}$ ,  $\forall i$  (3.11)

As  $IPC_i$  for each core *i* is given, the power function  $P_i$  of that core is a convex function of  $\mathfrak{F}_i$ . There are two constraints that need to be satisfied for each ExDVFS control epoch: (1) the throughput should be at least equal to a specific value to meet the iso-performance requirement, and (2) the operating frequency  $\mathfrak{F}$  for each core should be in proper operating ranges, which is defined by our operating ranges in HSPICE. Please note that the power model  $P_i$  varies from one core to another due to the PVs.

## 3.4.2 Constrained throughput maximization

We also consider the dual problem of performance improvement under power constraint, in other words, how much the variation-aware ExDVFS approach can improve the throughput under given power budget. Similarly, given IPC (IPC) for all cores in each ExDVFS control epoch, we can express this problem in a n-core CMP as:

Objective :

$$arg \max_{\mathfrak{F}_i} \sum_{i=1}^n IPC_i \cdot \mathfrak{F}_i$$

Subject to :  $\sum_{i=1}^n P_i(\mathfrak{F}_i) \leq Power_{const}$  (3.12)

$\mathfrak{F}_{min} < \mathfrak{F}_i < \mathfrak{F}_{max}$ ,  $\forall i$  (3.13)

The objective is a linear function of  $\mathfrak{F}$ . There are two constraints: (1) the total power consumption is at most equal to the power budget, which is convex constraint, and (2) the frequency range constraint is the same as Equation 3.11. The above is still a convex optimization problem since the objective is the maximum of a concave function and the constraints are convex.

Convex optimization problem can be solved efficiently by Interior Point method and Dual methods [6]. In this work, we implement the Interior Point method by using Matlab<sup>®</sup> to obtain the optimal  $\mathfrak{F}$  that minimizes the energy consumption of a CMP while satisfying the throughput and other physical constraints. The Interior Point method is extremely fast, taking only 5ms in Matlab to select the best  $\mathfrak{F}$  each control epoch. Therefore, implementing

it as part of the OS kernel will be much faster, which opens the possibility of its applicability in an online setting.

# 3.5 Implementation flow

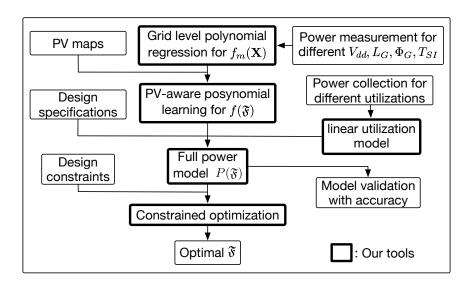

Figure 3.3: Implementation flow for the proposed framework.

The flowchart is provided in Figure 3.3. To begin with, we collect the dataset  $(p^{\ell}, \mathfrak{F}^{\ell})$  for learning  $\hat{f}(\mathfrak{F})$  that captures the changes of power consumptions at wide-range operating frequencies (from NTC to turbo mode) as described in Section 3.3.1. To collect the variation-aware dataset for each core, we make the power measurement across various  $V_{dd}$  and dominant process parameters  $(L_G, T_{SI}, \text{ and } \Phi_G)$ , and perform the regression for grid level power  $\hat{f}_m(\mathbf{X})$  and the integration of PV maps. Next, we learn  $\hat{u}(\mathfrak{F})$  that models the dynamic power changes according to the workload variations as described in Section 3.3.2. The design-specific  $P_{dyn}^{peak}$  is set to 70% of thermal design power (TDP)<sup>2</sup> for a core, and  $P_{sta}^{peak}$  is set to 30% TDP, which is approximately an average proportion for our experimental results and is also similar to results for Intel Xeon core in McPAT paper [58]. By plugging  $\hat{f}_d(\mathfrak{F})$ ,  $\hat{f}_s(\mathfrak{F})$  and  $\hat{u}(\mathfrak{F})$  into Equation 3.2,  $\hat{P}$  is obtained. We then validate the learned  $\hat{P}$  with the performance and power values provided by Sniper and McPAT executing PARSEC and

<sup>&</sup>lt;sup>2</sup>TDP refers to the average maximum power a processor can dissipate to avoid overheating.

SPLASH-2 benchmarks at different operating frequencies, as described in Section 3.3.3. The average RMSPE is **5.14**%. Furthermore, the overhead of voltage transitions for DVFS is less than 9ns [65] and therefore is negligible during each control epoch (1ms). We emphasize that the proposed learning framework is generic and is not restricted to a certain simulator or application. To perform the limit study of the maximum benefits of deploying wide-range operations from NTC to turbo mode, the workload characteristics of each processing core along with user-specified constraints are fed into the optimization framework described in Section 3.4.1 and 3.4.2 to select the best  $\mathfrak{F}$  for each control epoch. Note that workload characteristics from other sources, such as on-chip performance counters, can also be plugged into the proposed framework for calculating the best  $\mathfrak{F}$ . Finally, the performance constraint in Equation 3.10 and the power constraint in Equation 3.12 are set to the throughput achieved and power consumed, respectively, under the nominal  $V_{dd}$  and  $\mathfrak{F}$  for each benchmark. To reduce the randomness, our results are based on at least ten independent sets of PV maps.

# 3.6 Experimental results

In this section, we establish our experiments and perform the convex optimization as formulated in Section 3.4. We set normalized operating frequency from 0.05 to 1.22 (nominal  $\mathfrak{F}$ = 2.66GHz), which covers from NTC up to turbo mode.

# 3.6.1 Iso-performance energy optimization

For simplicity, we use ExDVFS to denote the DVFS over wide operating ranges: NTC, nominal and turbo mode. To achieve a comprehensive analysis of the effects due to PVs, we compare the following approaches:

• Baseline: the approach without ExDVFS or variation-aware adaption. All cores run at the same nominal  $V_{dd}$  and conservative  $\mathfrak{F}$  (the slowest  $\mathfrak{F}$  across all cores).

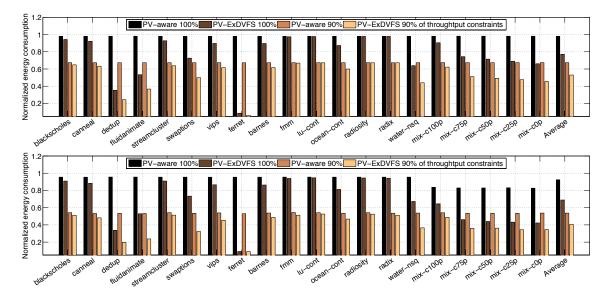

Figure 3.4: Average energy minimization results across 10 variation maps under 100% and 90% throughput constraints. **Top**:  $3\sigma$  (standard deviation) of process parameters is 10% of their nominal values. PV-ExDVFS achieves the lowest energy points, the average reduction compared with the baseline approach is 22.88% for 100% throughput (hard) constraint and 47.13% for 90% throughput (soft) constraint. **Bottom**:  $3\sigma$  is 30%. The corresponding energy reduction of PV-ExDVFS is 31.09% for hard constraint and 59.59% for soft constraint.

- **PV-aware**: the approach only integrating fine-grained PV information. In this case, cores run individually at the highest  $\mathfrak{F}$  for the same  $V_{dd}$ . No dynamic adaptation is performed.

- PV-ExDVFS: the newly proposed approach based on fine-grained PV information in addition to ExDVFS. In this case,  $V_{dd}/\mathfrak{F}$  levels are customized for each core based on the PV information, and the optimal levels are chosen in a workload-aware fashion as described in Section 3.6.1 and 3.6.2.

We evaluate the energy minimization under iso-performance constraints by comparing the experimental results of the above approaches on different workloads and their mixtures from PARSEC and SPLASH-2 benchmark suites. The evaluations are based on region-of-interest (ROI) [13], excluding the initialization and cleanup phases for parallel benchmarks. Each workload mixture is composed of benchmarks randomly chosen from the two suites to represent a kind of heterogeneous multi-threaded workload. For example, mix-c75p means

75% of threads are core-bound while the rest are memory-bound. The classification is similar to the one used in [3][89]. The results of all approaches normalized by the baseline case (**Baseline**) are listed in Figure 3.4. All results are the average improvements across ten randomly generated variation maps. Furthermore, we evaluate the case with "soft" constraints. Namely, we set the total throughput at 90% of the baseline in Equation 3.10 to explore the case where we further reduce energy in exchange of only 10% of total throughput.

Figure 3.4(top) illustrates that PV-ExDVFS achieves the lowest energy points, the average reduction compared with the baseline approach is 22.88% for 100% throughput (hard) constraint and 47.13% for 90% throughput (soft) constraint. From the figure, we can see that PVs have a great impact on the power and performance in CMPs. Without ExDVFS algorithms, CMPs can still achieve 32.70% energy reduction on average with knowledge of only process variation information for the soft constraint case, but the benefit increases by a half when ExDVFS is enabled. We note that among the PARSEC and SPLASH-2 benchmarks analyzed, ferret is the most imbalanced benchmark in terms of computation requirements per thread and therefore benefits the most from an extended DVFS paradigm. Indeed, in this case we observe a **10X** power reduction at iso-performance, while for 10% performance drop, a 20X power reduction is observed. To further evaluate the effects of PV induced on CMPs, we perform similar comparisons on CMPs with extreme PV level ( $3\sigma$ = 30%). Comparing the top and bottom figures of Figure 3.4, we find that more energy is saved in all cases. For the hard constraints, an additional 5.68% and 8.21% are saved by PV-aware and PV-ExDVFS, respectively. For the soft constraints of 90% throughput, the corresponding additional savings are 13.58% and 12.46%.

# 3.6.2 Iso-power performance optimization

Similar to the analysis in Section 3.6.1, in this section we also evaluate the three approaches using the same baseline. We also consider the "soft" constraints. Namely, we increase the total power to 110% of the baseline in Equation 3.12 to find out how further to improve

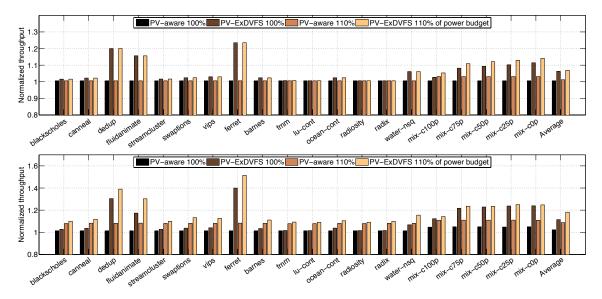

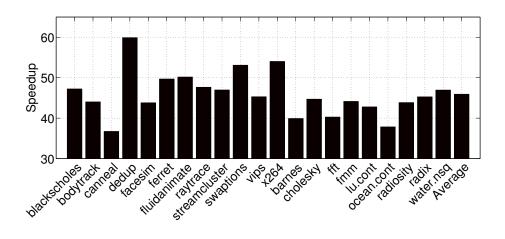

Figure 3.5: Average throughput improvement results across 10 variation maps with 100% and 110% power budgets. **Top**:  $3\sigma$  (standard deviation) of process parameters is 10% of their nominal values. PV-ExDVFS achieves the highest throughput points, the average improvement compared with the baseline approach is 6.25% for 100% power (hard) budget and 6.93% for 90% power (soft) budget. **Bottom**:  $3\sigma$  is 30%. The corresponding throughput improvement of PV-ExDVFS is 11.46% for hard constraint and 18.17% for soft constraint.

throughput in exchange of 10% more power consumption. The results of all approaches normalized by the baseline case are listed in Figure 3.5.