# Supporting Information

# Accumulative polarization reversal in nanoscale ferroelectric transistors

Halid Mulaosmanovic<sup>1\*</sup>, Thomas Mikolajick<sup>1,2</sup> and Stefan Slesazeck<sup>1</sup>

<sup>1</sup> NaMLab gGmbH, 01187 Dresden, Germany

<sup>2</sup> Chair of Nanoelectronic Materials, TU Dresden, 01062 Dresden, Germany

## **Corresponding Author**

\*E-mail: halid.mulaosmanovic@namlab.com

#### S1. Abrupt switching in nanoscale FeFETs

The switching behavior of the ferroelectric transistors is largely influenced by their size. In fact, large-area devices are characterized by a gradual polarization reversal,<sup>1,2</sup> whereas the nanoscale transistors considered in this study (W = 80 nm, L = 30 nm,  $t_{HfO2} = 10$  nm) exhibit an abrupt switching both in the time and field domain. This discrepancy can be understood by the fact that the large devices contain a multitude of switchable ferroelectric domains in the HfO<sub>2</sub> layer (in contrast to the small devices<sup>3</sup>). Therefore, there will be a distribution of coercive fields among different domains, which leads to a gradual  $V_T$  switching upon a voltage amplitude variation.<sup>2</sup>

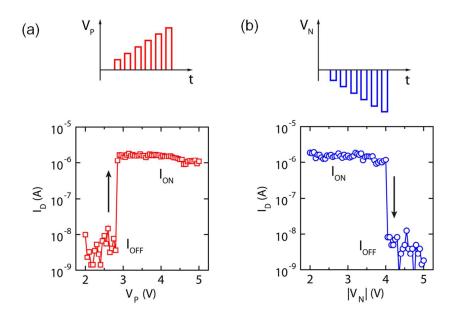

The switching in the time domain of the nanoscale FeFETs was discussed in the main text. For the sake of completeness, here we report the switching curves in the voltage domain as well. A more detailed analysis can be found in Ref. 3. Figure S1 shows the switching from OFF to ON state (a) and from ON to OFF state (b). The sharp switching for both transitions testifies to the equivalence of the two polarization states (up and down). This furthermore means that the accumulative polarization reversal considered in the main text can be equivalently achieved starting from the ON state, which would end up in the OFF state after a certain number of received negative gate pulses.

Figure S1 | Abrupt switching of nanoscale ferroelectric transistors in the field (amplitude) domain. (a) Switching from OFF to ON state upon increasing amplitude of positive gate pulses  $V_P$ ; (b) Switching from ON to OFF state upon increasing amplitude of negative gate pulses  $V_N$ . Pulse width of excitation pulses was constant and equal to 1 µs.

#### S2. Stimuli accumulation vs. inter-arrival time of electrical stimuli

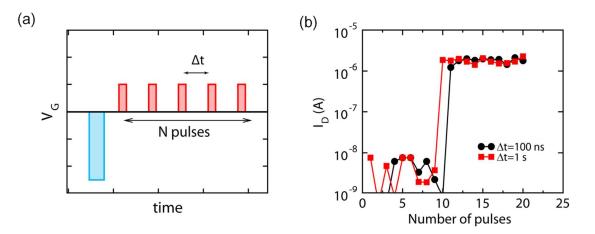

Our experiments reveal that the accumulative switching described in Fig. 2 of the main text is insensitive to the variation of the temporal distance between consecutive pulses (pulse interarrival time  $\Delta t$ , as indicated in Fig. S2a). This was confirmed on a large time scale from  $\Delta t = 100$  ns to  $\Delta t = 1$  s (Fig. S2b), which suggests that the nanodomains created upon the progressive electrical excitation are stable during the explored  $\Delta t$  range.

Figure S2 | Accumulative switching vs. inter-arrival time of electrical stimuli. (a) Gate voltage excitation scheme adopted to explore the accumulative switching. (b) Switching from OFF to ON upon excitation pulses having  $V_P = 2.2 \text{ V}$ ,  $t_{PW} = 1 \text{ µs}$  for two different inter-arrival times  $\Delta t$ . Note that the two switching curves are within the variability range described in Fig. 4, which therefore means the switching is invariant with respect to  $\Delta t$ .

### **References:**

(1) Müller, J.; Böscke, T. S.; Schröder, U.; Hoffmann, R.; Mikolajick, T.; Frey, L. Nanosecond Polarization Switching and Long Retention in a Novel MFIS-FET Based on Ferroelectric HfO<sub>2</sub>. *IEEE Electron Device Lett.* **2012**, *33* (2), 185-187.

(2) Mulaosmanovic, H.; Ocker, J.; Müller, S.; Noack, M.; Müller, J.; Polakowski, P.; Mikolajick, T.; Slesazeck, S. Novel Ferroelectric FET Based Synapse for Neuromorphic Systems. *Symp. VLSI Technol., Dig. Technol. Pap.*, **2017**, T176-T177.

(3) Mulaosmanovic, H.; Ocker, J.; Müller, S.; Schroeder, U.; Müller, J.; Polakowski, P.; Flachowsky, S.; van Bentum, R.; Mikolajick, T.; Slesazeck, S. Switching Kinetics in Nanoscale Ferroelectric Field-Effect Transistors Based on Hafnium Oxide, *ACS Appl. Mater. Interfaces* **2017**, *9*, 3792-3798.

(4) JEDEC Standard JESD28-A, Procedure for Measuring N-Channel MOSFET Hot-Carrier-Induced Degradation under DC Stress, **2001**, 10.